## **Developments in silicon trackers at LPNHE for future experiments**

G. Calderini LPNHE Paris

G. Calderini, FCC-Workshop, Paris LPNHE, 24/04/2020

CINIS

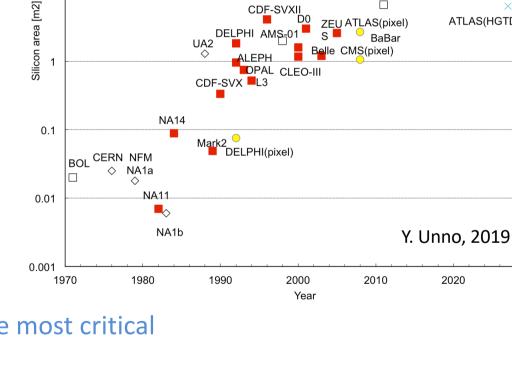

#### Since the '90s, silicon trackers played a crucial role in HEP experiments 1000 Strips (HEP)

100

10

□ Strips (Astro/Nucl)

Pixel (HEP)

♦Pads

×FAST

Running conditions and detector requirements have changed a lot in these 40 years

Surface has increased exponentially, requirements in terms of dataflow, radiation hardness, material budget, number of channels

Pixels have been recently the core 0.001 1970 of most silicon tracking systems, where the running conditions are the most critical

Constant evolution which will continue in the next years for the next experiments

CDF-SVXII

2030

CMS(HL)

ATLAS(HL)

CMS(HL)

CMS(ECT) ATLAS(HL)

ATLAS(HGTD)

CMS

GLAST

ATLAS

**ZFU ATLAS**(pixel)

AMS-02

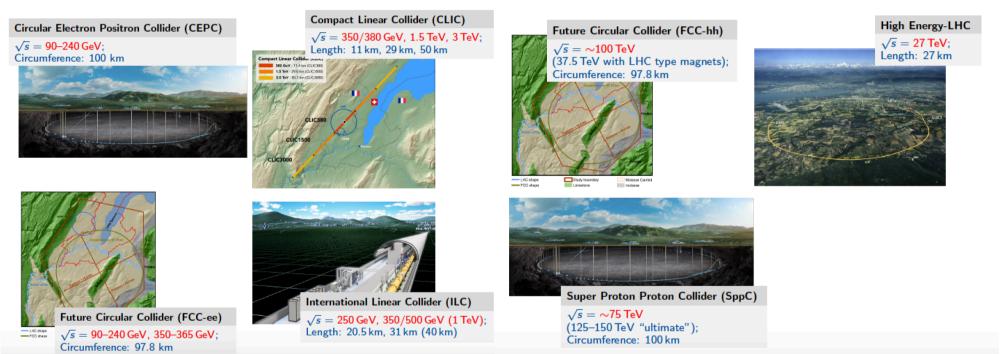

The required technology development for sensor, readout electronics and infrastructure (mechanics, cooling) is very different as a function of the machine

High-energy e+e- collider proposals

## High-energy hadron collider proposals

At LPNHE we develop aspects of trackers which will be very important for the two classes of machines. I will concentrate on sensors and advanced cooling structures. We are also on other aspects.

For recent developments outside what we do at LPNHE, you can have examples in my previous FCC-France presentation. https://indico.in2p3.fr/event/19693/contributions/76083/attachments/55956/74003/FCC-calderini.pdf

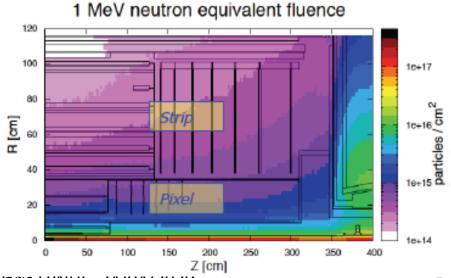

#### LHC FCC-hh FCC-ee CLIC 3 TeV Exp. HL-LHC Parameter N x 10<sup>15</sup> 10<sup>16</sup> 1016 - 1017 $< 10^{10}$ <1011 Fluence [neg/cm<sup>2</sup>/y] 2-4 G\*\*\*\*) 20 M \*\*\*) 240k Max. hit rate [s<sup>-1</sup>cm<sup>-2</sup>] 20 G 100 M Surface inner tracker [m<sup>2</sup>] 2 15 1 1 10 Surface outer tracker [m<sup>2</sup>] 200 200 400 200 140 0.3%\*)-2% 0.1%<sup>\*)</sup>-2% Material budget per detection 0.2% 1% 0.3% layer [X<sub>0</sub>] <~25x25 25x25 Pixel size inner layers [µm<sup>2</sup>] 100x150-~50x50 25x50 50x400 BC spacing [ns] 25 25 25 20-3400 0.5 ~1k \*\*\*) <~25-1k\*) $0.2^{(1)}-1k^{(1)}$ ~10-2 ~5 Hit time resolution [ns]

#### Silicon vertex and tracking detector parameters

\*) ALICE requirement \*\*) LHCb requirement \*\*\*) At Z-pole running \*\*\*\*) max. output rate for LHCb/high intensity flavour experiments: 300-400 Gbit/s/cm<sup>2</sup>

#### Hadron colliders

- Very high radiation levels:  $\leq 10^{18} n_{eq}/cm^2$

- Very high hit rates

- Very precise timing: <0(5 ps)</p>

#### Lepton colliders

- Very small single point resolution (≤ 3 μm)

- Very low material budget (≤ 0.2%X₀/layer)

#### Remarks

- Note that ps-level timing was not part of initial HL-LHC detector requirements

- Became available through pioneering R&D on LGAD / MCP / precise timing with silicon

- Now well motivated for vertex separation / pattern reconstruction

## Fighting against radiation

This is one of the key features we developed for HL-LHC sensors

#### Instantaneous conditions

- pileup and high event rate

- increased occupancy

- higher granularity sensor

- SEU-robust, fast readout

## Integrated effects (radiation dose)

- leakage current

- change in operation voltage

- reduced charge collection

- rad-hard components

- thin sensors (partial depletion)

- <u>Peak luminosity</u>: 5-7 x 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> → ~x5-7

- <u>Average pile-up</u>: up to  $\langle \mu \rangle \sim 200 \rightarrow \sim x8$

- <u>Integrated luminosity</u>: 3000 fb<sup>-1</sup>  $\rightarrow \sim x10$

- Requested <u>radiation hardness</u>: 2x10<sup>16</sup> n<sub>eq</sub>/cm<sup>2</sup> → x20

G. Calderini, FCC-Workshop, Paris LPNHE, 24/04/2020

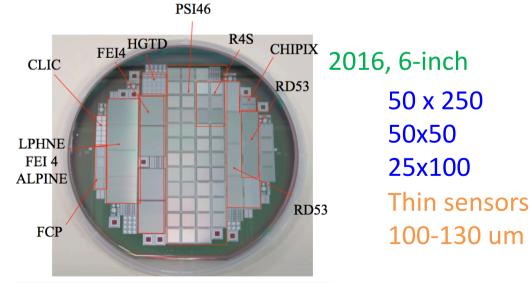

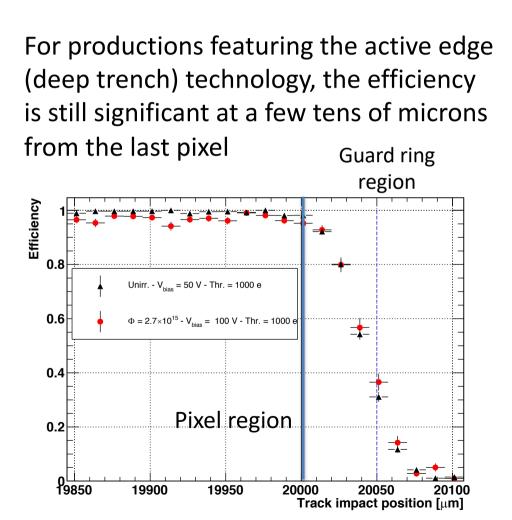

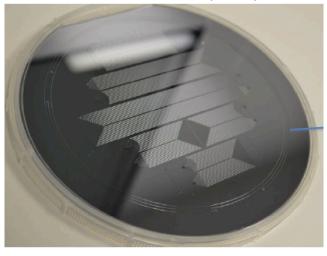

## Many LPNHE productions in collaboration with FBK Trento Increasing performance with respect to radiation and track multiplicity in the event

50x400 and 50x250 pixels with and without active edges; 200um thick

2018, 6-inch 50x50 25x100 Thickness down to 50 and

100um

Common ATLAS-CMS G. Calderini, FCC-Workshop, Paris LPNHE, 24/04/2020

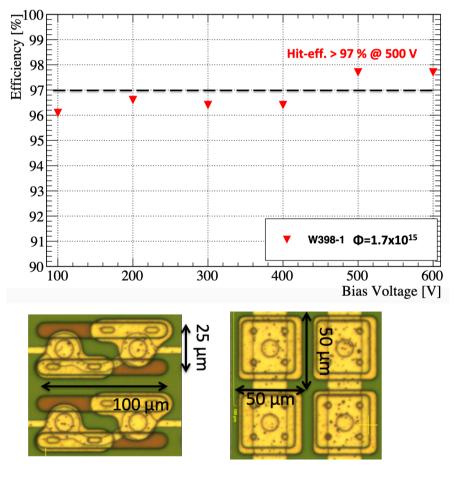

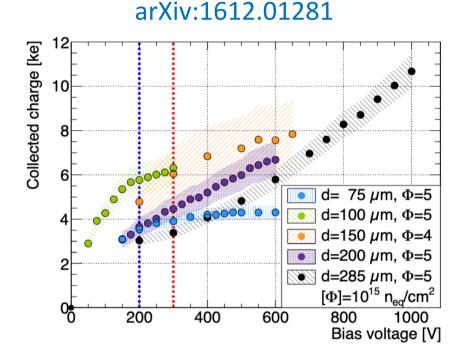

#### Hit efficiency after irradiation

Thanks to the reduced sensor thickness, the hit performance is still significantly high (>97%) even after irradiation

#### Hit efficiency

G. Calderini, FCC-Workshop, Paris LPNHE, 24/04/2020

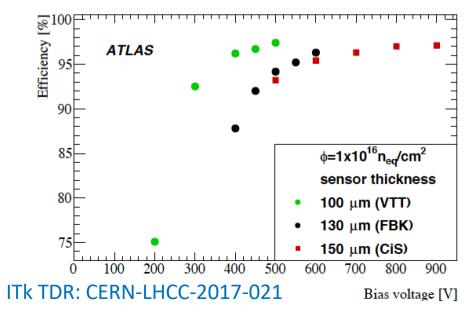

# Thin sensors are very performant with respect to radiation damage but also for material budget

After heavy irradiation the bulk cannot be fully depleted anymore. Interest to go thin!

- After irradiation, reduced collection distance, thin sensor can be optimal

- Stronger electric field, faster collection

- Lower power dissipation

- Lower occupancy at high eta

- Less material budget

Even at very high fluence (for planar pixels), thin sensor can guarantee an excellent hit reconstruction efficiency

G. Calderini, FCC-Workshop, Paris LPNHE, 24/04/2020

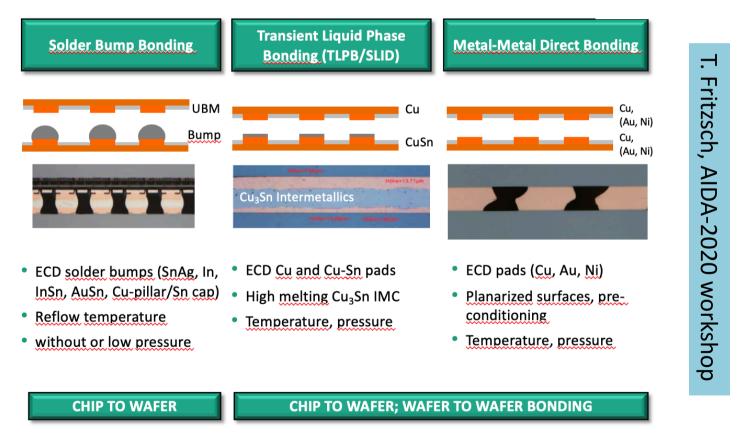

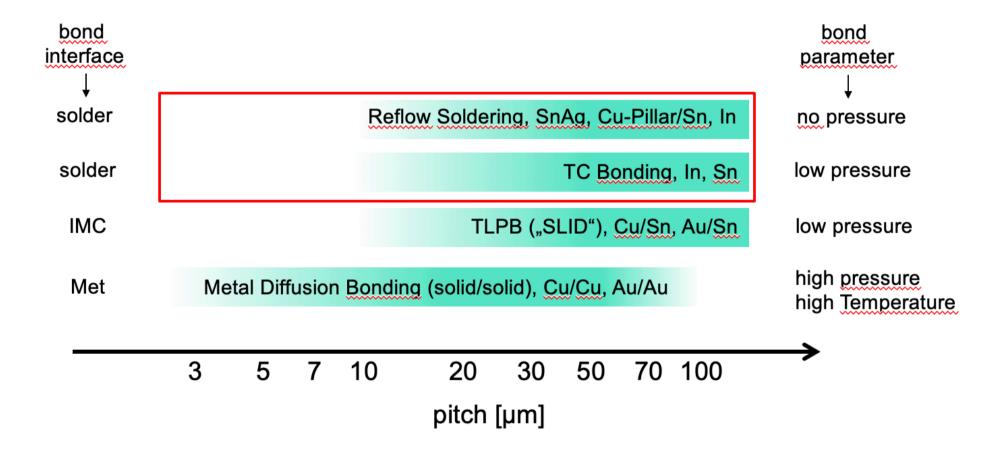

### Small pitch limitations

Small pitch could limited by interconnection techniques

Standard solder bump bonding, but also copper pillars, is in general limited to a pixel dimension of at least few tens of microns

Advanced techniques can be used to overtake this limit

IZM

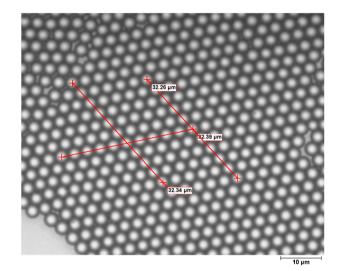

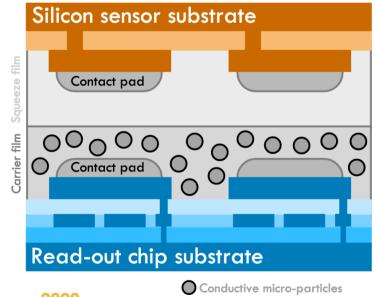

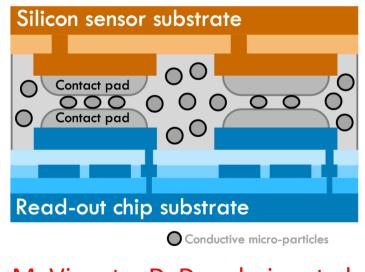

### Anisotropic conductive films (ACF): LPNHE in the AIDAinnova

Anisotropic conductive films can also be used as interconnection technique

- Application potentially important also from the cost point of view

- Bump-bonding represent a significant fraction of the hybridization cost of pixel modules

- Development is also part of AIDAinnova proposal in the hybrid detectors Working Package

#### M. Vicente, D. Dannheim et al.

G. Calderini, FCC-Workshop, Paris LPNHE, 24/04/2020

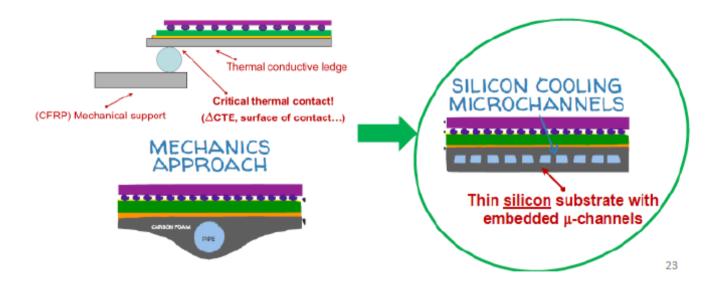

Advanced cooling structures Microchannels at LPNHE

#### Reducing material budget: a transversal challenge

Reducing the sensor thickness is not the only key to reduce the material budget A significant fraction of x/x0 is brought by the services

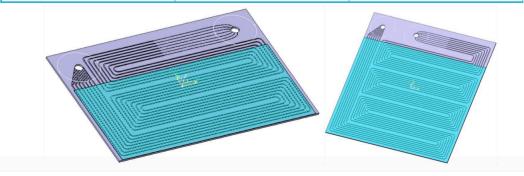

Since a few years the LPNHE group is developing light cooling structures in the framework of the REFLECS, REFLECS2 project (M. Bomben) and of AIDA-2020

Micro-channel structures developed following two axes:

- develop cooling blocks for our silicon modules

- develop structures able to study the evaporative behaviour of CO2 in channels and compare with models

| "Snake" design microchannel cooling unit size |            |             |  |  |

|-----------------------------------------------|------------|-------------|--|--|

| Design                                        | Width [mm] | Height [mm] |  |  |

| Single                                        | 30.0       | 30.0        |  |  |

| Double                                        | 30.0       | 41.3        |  |  |

| Quad                                          | 42.4       | 48.0        |  |  |

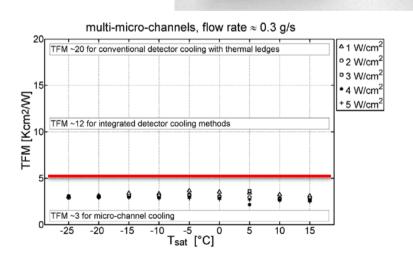

#### Micro-channel cooling

More uniform cooling, less material in the system, less cooling fluid (strong point in industrial applications)

Already used in existing trackers (NA62, LHCb) but challenging at ATLAS/CMS; CO2 pressure of tens of atmospheres!

Much better cooling Thermal Figure of Merit (TFM) due to CO2 evaporation and to uniform distribution of cooling structure

This technology can be used not only in hybrid pixels but channels can be carved directly in the readout chip. AIDAinnova development for CMOS

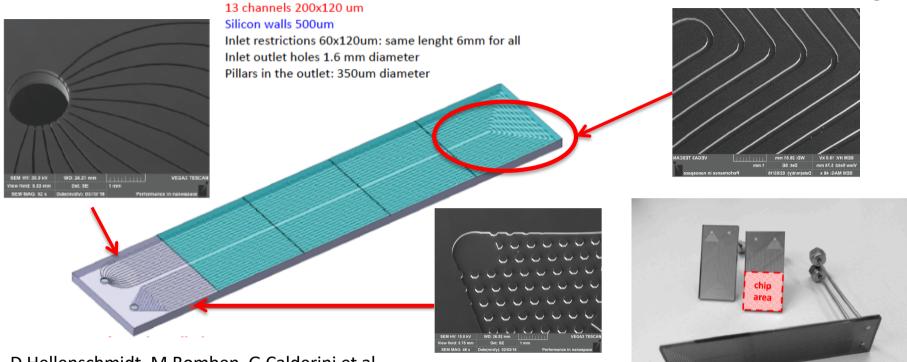

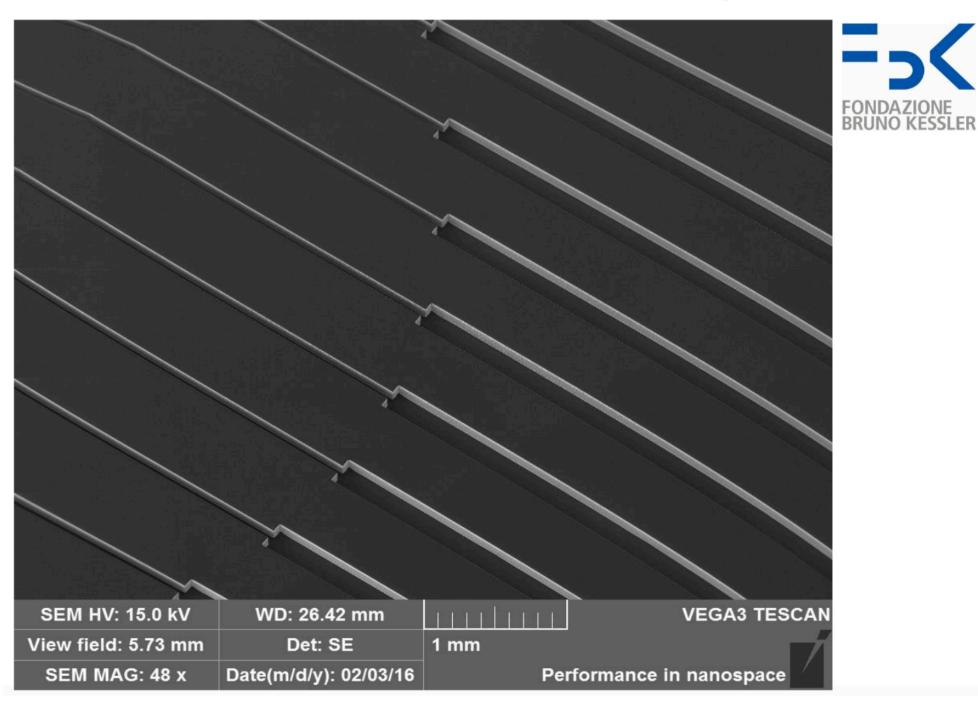

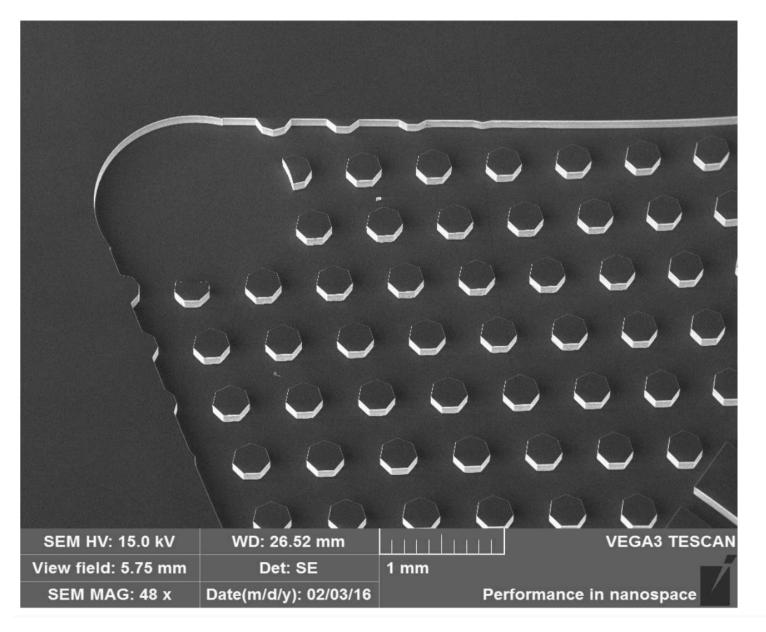

#### Prototypes produced by LPNHE with FBK and IEF Orsay

D.Hellenschmidt, M.Bomben, G.Calderini et al, Nucl. Instrum. Meth. A 958 (2020) 162535

Details of the channel design

#### Inlet fanout

|                     |                       |                          | FONDAZIONE<br>BRUNO KESSLER |

|---------------------|-----------------------|--------------------------|-----------------------------|

| SEM HV: 30.0 kV     | WD: 24.21 mm          | VEGA3 TESCAN             |                             |

| View field: 5.33 mm | Det: SE               | 1 mm 7                   |                             |

| SEM MAG: 52 x       | Date(m/d/y): 03/10/16 | Performance in nanospace |                             |

#### Channel size modulation to control CO2 boiling

## Detail of the outlet; pillars to reduce the surface (force) on the plexiglass cover

### Conclusions

The data-taking conditions at colliders have evolved towards challenging tracking environments over the last 30 years

In parallel, a lot of technological progress has been made in detectors and in silicon trackers in particular, to cope with these new conditions

Different families of devices have been developed at LPNHE to match specific contexts; I went through some examples, there are more.

I tried to give snapshots of some areas in which there were significant recent improvements, but there are many more!

For each future machine there is already a tracker solution which is developing, but technology will evolve even more in the meantime

## Importance of 4<sup>th</sup> coordinate: Timing Fourth dimension is the next step of the new generations of trackers Will be able to solve ambiguities due to fast bunch crossing or pileup

NA62 Collaboration led the path, with a resolution per station of the order of 180 ps

ATLAS/CMS developing timing layers

Hard

scatter jet

"Stochastic pileup jet

G. Calderini, FCC-France Workshop, Paris LPNHE, 14-15/11/2019

p<sub>T</sub> [GeV]

QCD pileup jet

time [ps]

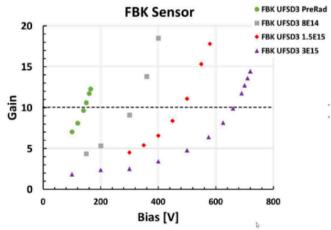

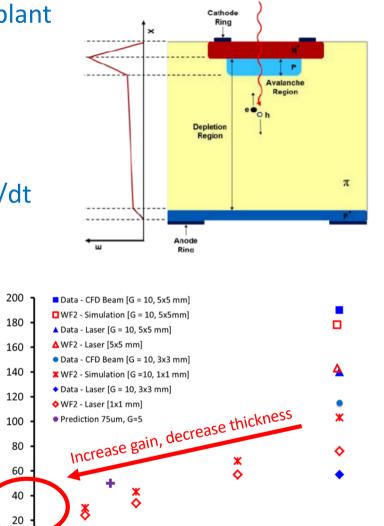

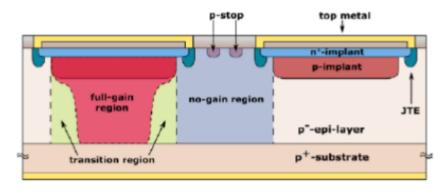

#### LGAD – Low Gain Avalanche Diode

- Highly doped p+ region below the n+ implant

- This generates a multiplication layer

- Internal gain factor from 10x to 30x (before irradiation)

- Low thickness to maximize slew rate: dV/dt

Gain decreases after radiation (de-activation of the gain layers)

150

200

Thickness [µm]

250

300

350

• Options under study: Gallium or Carbon co-implantation

G. Calderini, FCC-France Workshop, Paris LPNHE, 14-15/11/2019

0 +

50

100

Timing Resolution [ps]

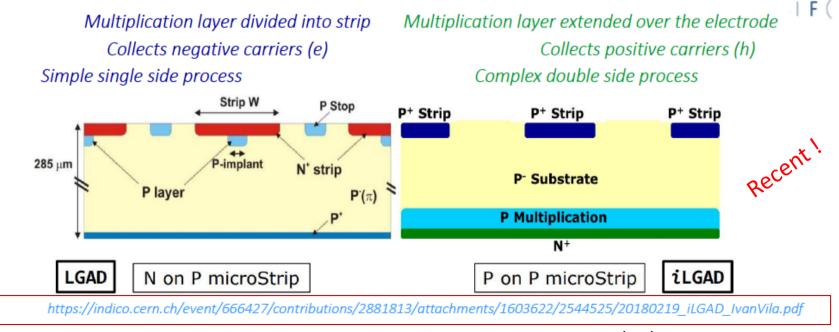

#### Inverted LGAD - (I-LGAD)

In standard LGADs, the presence of a multiplication layer prevents the use of small pixel implants due to the width of the no-gain region

A few techniques are available to avoid this limitation: one is the use of Inverted-LGADS (I-LGADs) where the multiplication layer is on the opposite face

G. Calderini, FCC-France Workshop, Paris LPNHE, 14-15/11/2019