# TB preparation meeting Status on LLR jobs

Jérôme NANNI

LLR technical coordinator

# Status on LLR jobs

#### Electronics

- Modify CCC to deliver 40Mhz :

- LV cables:

- Check existing

- Make new internal cables for SMB5 <</p>

- **Update DIF firmware:**

- Move to 40MHz and 5Mhz

- Add gated clock 🙂

- Add OneWire + control command 😑

🗖 Synchro between DAQ 🙂

## Status on LLR jobs

#### > Mechanics:

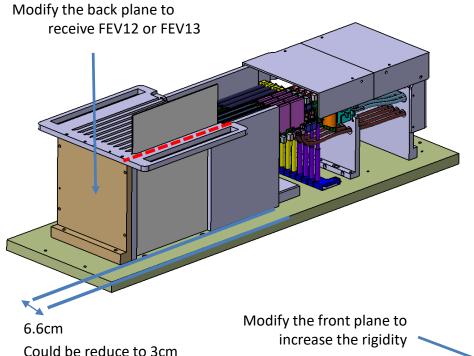

- □ Study solution to integrate FEV board + SMB4/5 🙂

- Add solution to maintain boards

- Reduce effort on interconnection due to cables .

# Modification start 10/02/20

Assembly after modification ~ end of February •

### Status on LLR jobs

We need to define, where our structure will be positioned, in front of the beam or after IJC structure ?

Maybe the last time, we use this structure. We move to a new solution to improve the pitch between 2 layers, close to IJC lab or use your structure + all DAQ

10/02/2020

TB DESY2020 preparation meeting

Solution to maintain SMBV5

Solution to maintain cables

### To conclude

- Electronics: well progressing

- Mechanics: new design, reception end of February

#### New production (assembly) of 2 SLAB in Japan with PCB, wafer and chips from LLR but time is short ... maybe too short.

#### Packet send today to Japan