# **SILICON BASED QUANTUM COMPUTING**

## Agenda

- Introduction

- Hardware status with focus on silicon

- How to go to large scale?

- ERC QuCube original idea

- Project organization

- Highlights and results

### Opportunities High performance computing

Global High Performance Computing (HPC) market share, by end use, 2017 (%)

US\$ 32 billions in

2017

Gaming

Media & Estadaia

- Media & Entertainment

- Retail

BESI

- Transportation

- Government & Defense

- Education & Research

- Manufacturing

- Healthcare & Bioscience

- Others

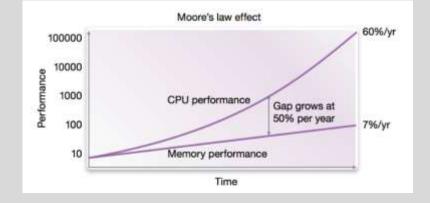

### **Scaling limitations**

Memory wall and power consumption are in the way of growing computing capabilities

### HOW TO REACH THE PROMISE OF QUANTUM COMPUTING?

#### QUANTUM SIMULATION

Better pharmaceutical, materials, chemistry, physics,...

#### MACHINE LEARNING & BIG DATA

Autonomous vehicles, finance, mathematics

Hundreds of qubits

Millions of errorless quantum operations

#### LIVING WITH ERRORS

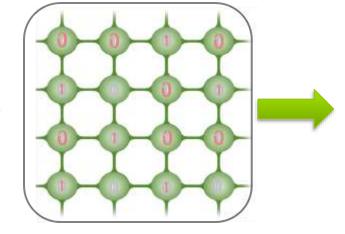

### Millions of errorless quantum operations

Quantum Error Correction protocols

millions of physical qubits in a 2D array

**1 Errorless logical qubit** > 1000 physical qubits

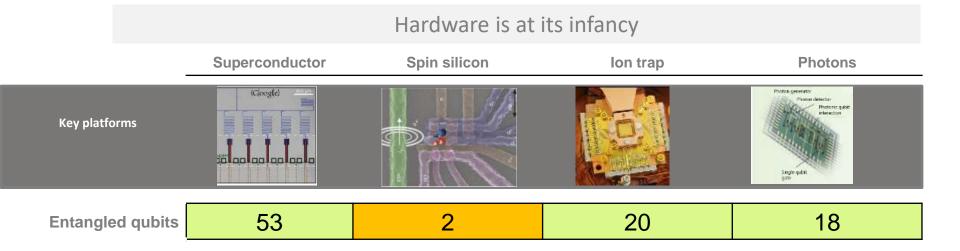

### WHERE DOES QUANTUM COMPUTING STAND?

#### WHERE DOES QUANTUM COMPUTING STAND?

|               | Hardware is at its infancy |                      |                    |                                                                                                |

|---------------|----------------------------|----------------------|--------------------|------------------------------------------------------------------------------------------------|

|               | Superconduc                | tor Spin silicon     | lon trap           | Photons                                                                                        |

| Key platforms |                            |                      |                    | Proton generator<br>Proton desirator<br>Proton desirator<br>Educación<br>Strajfe quict<br>gato |

| Entangled qu  | bits 53                    | 2                    | 20                 | 18                                                                                             |

| :             | Size (100µm) <sup>2</sup>  | (100nm) <sup>2</sup> | (1mm) <sup>2</sup> | 1 mm <sup>2</sup>                                                                              |

| Fid           | elity 99.3%                | 98%                  | 99.9%              | 50% (mesure)<br>98% (portes)                                                                   |

| Sp            | eed 100 ns                 | 5 µs                 | 100 µs             | 1 ms                                                                                           |

| T° of opera   | tion 20mK                  | 1K                   | Room T°            | 4K                                                                                             |

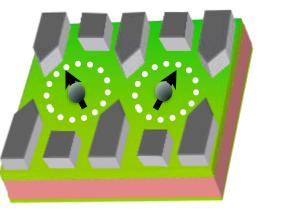

Spin degree of freedom of an electron

$\begin{array}{c} \mathbf{0} \Rightarrow |\uparrow\rangle \\ \mathbf{1} \Rightarrow |\downarrow\rangle \end{array}$

Gate defined quantum dots

### Single and two qubits gate demonstrations

How to go to large scale?

- Variability

- Controlability

- Individual qubit addressing

- Cross talk

- Large scale coherence

#### OBJECTIVE

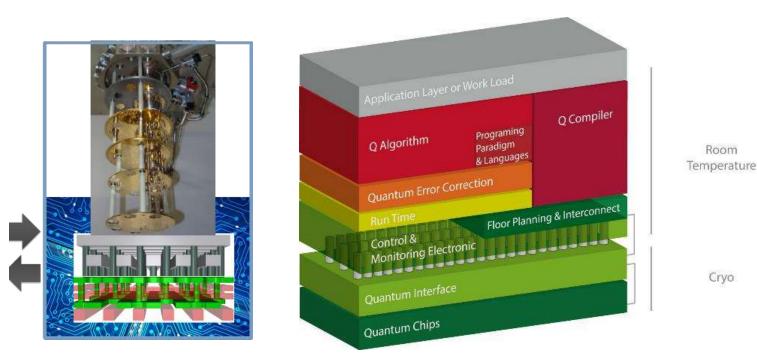

Design and fabricate a **quantum accelerator** encoding quantum information in silicon spins and develop low level software allowing its use to solve **dedicated** useful problems.

### STRATEGY FOR BUILDING A QUANTUM COMPUTER

1

leti

C22Lech

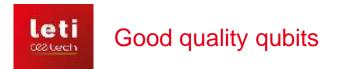

Definition of good quality single & few qubits

2D array definition

3

2

Long distance quantum information transfer

4

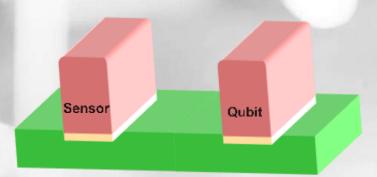

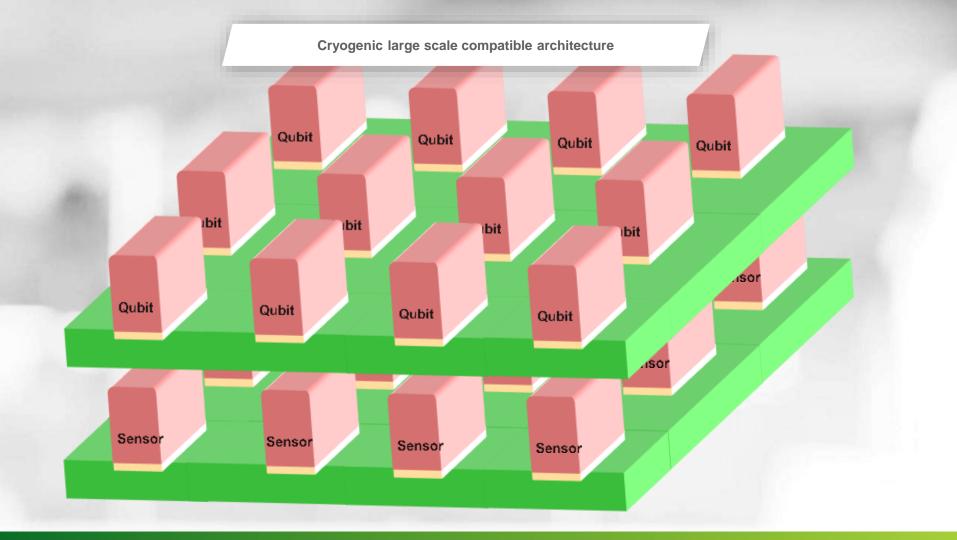

Cryogenic large scale compatible architecture

Cryogenic large scale compatible architecture

Cryogenic large scale compatible architecture

Cryogenic large scale compatible architecture

Meunier, De Franceschi, Vinet, Hutin (2017)

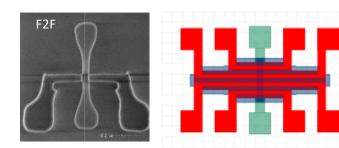

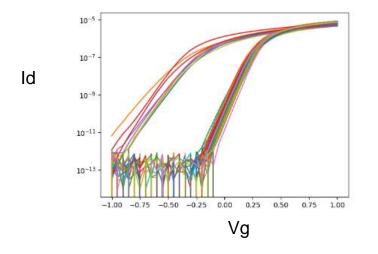

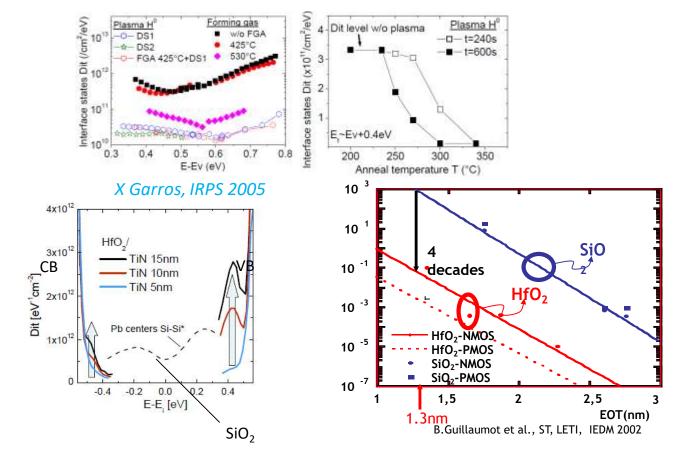

## Fabrication highlights: robust baseline developments

# Fabrication highlights: materials optimization

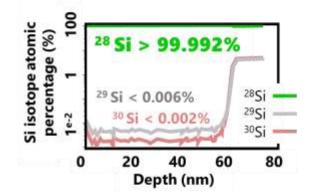

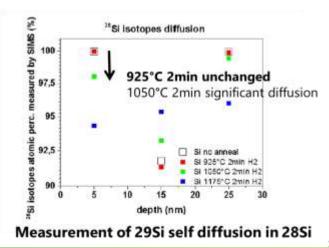

# <sup>28</sup>Si wafers

Mazzocchi et al., J of Crystal Growth (2018)

| species                          | concentration<br>(µmol/mol) |  |

|----------------------------------|-----------------------------|--|

| CH <sub>4</sub>                  | $\leq 0.05$                 |  |

| C <sub>2</sub> H <sub>6</sub>    | $\le 0.02$                  |  |

| $C_2H_4$                         | $\le 0.02$                  |  |

| C <sub>3</sub> H <sub>6</sub>    | $\leq 0.02$                 |  |

| C <sub>3</sub> H <sub>8</sub>    | $\le 0.01$                  |  |

| i-C <sub>4</sub> H <sub>10</sub> | $\le 0.02$                  |  |

| n-C4H10                          | $\le 0.02$                  |  |

| More than 52 other<br>species    | $\leq 80.35 \pm 20.135$     |  |

#### Microelectronics grade <sup>28</sup>Si

## Fabrication highlights: materials optimization

# Good quality qubits highlights

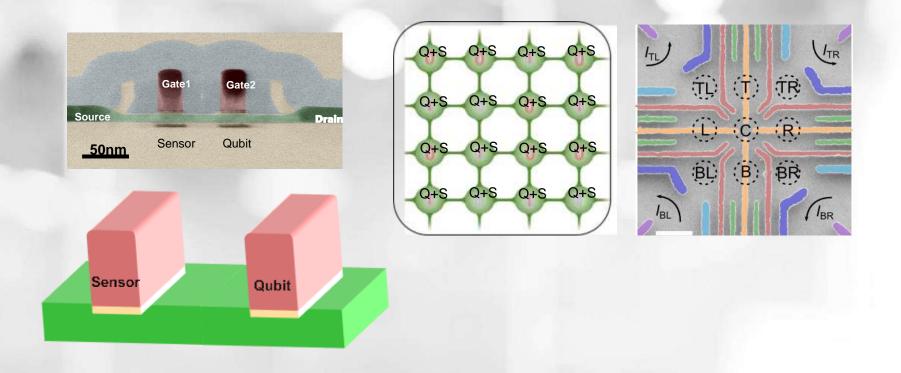

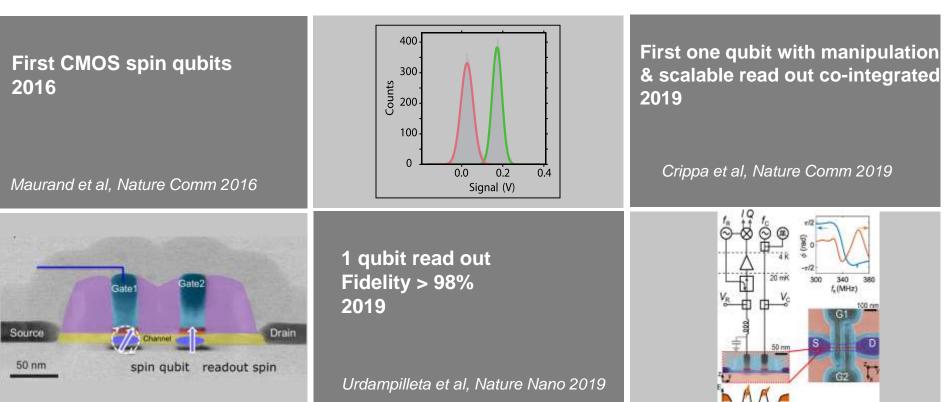

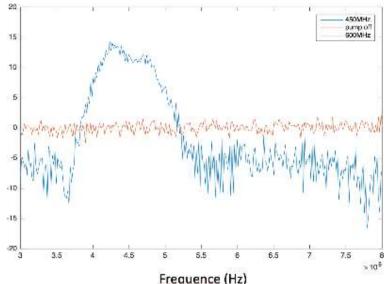

Gate-reflectometry with superconducting TWPA to increase fidelity and read out speed

- Design and fabrication of TWPA (N. Roch's team)

- First 0.3 K ٠

# Good quality qubits highlights

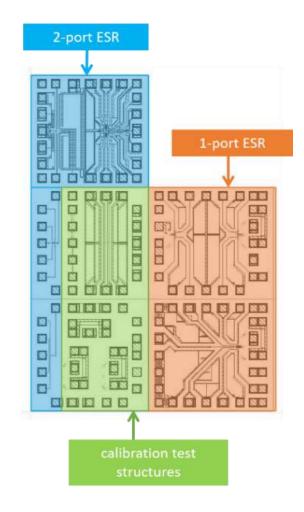

Design and integration of metal lines for ESR manipulation

(for electron spin qubits manipulation)

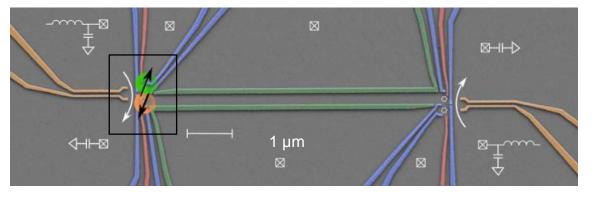

### Towards large scale highlights Fast spin coherent link and Spin entanglement at distance

Fast spin coherent link and spin entanglement at distance

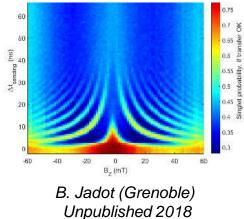

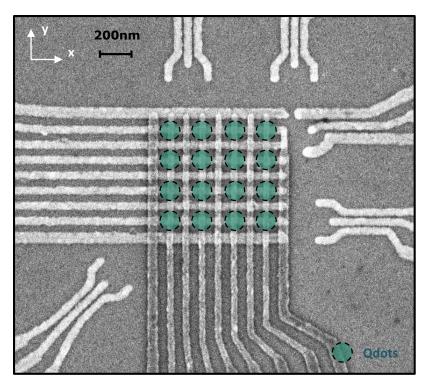

### Towards large scale highlights 4x4 line-column addressing

in III-V

## Control electronics highlights

**First co-integration of a quantum device quantum device** (double quantum dot) together with control electronics in commercial technology (28FDSOI) To be published @ ISSCC2020

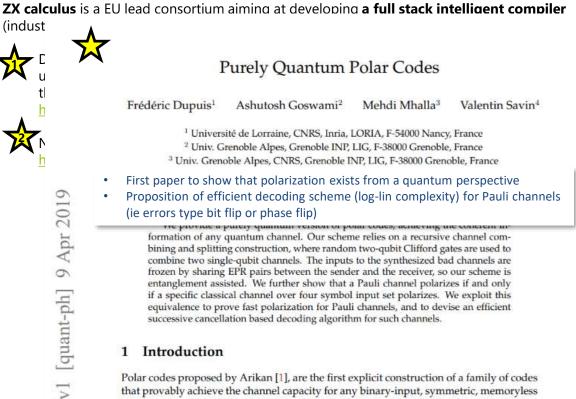

# Quantum algorithms highlights

channel. His construction relies on a channel combining and splitting procedure, where a

les

ts.

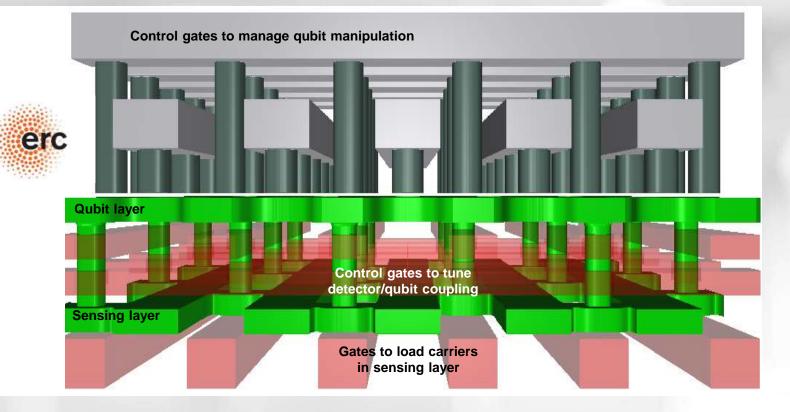

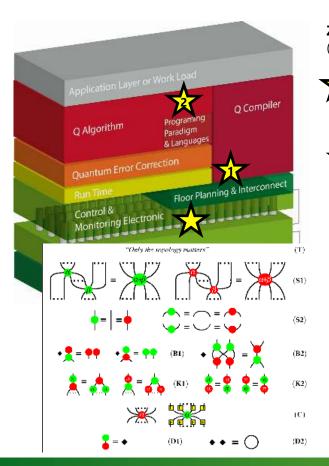

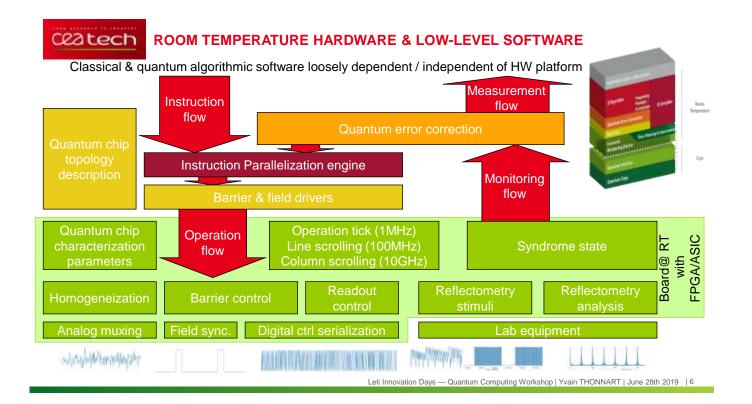

# Architecture highlights

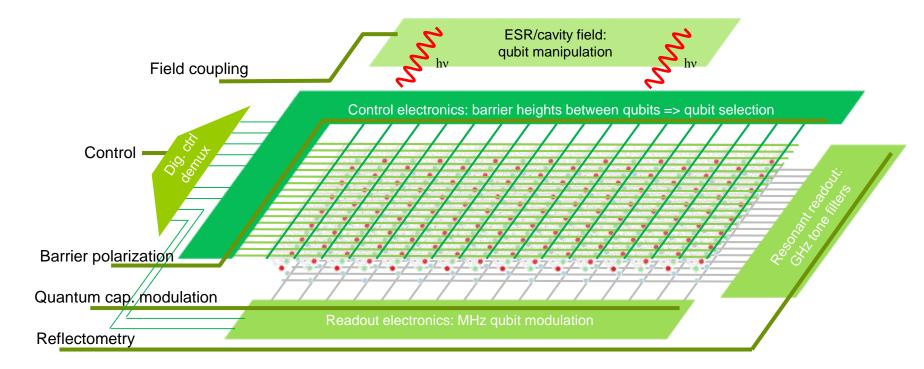

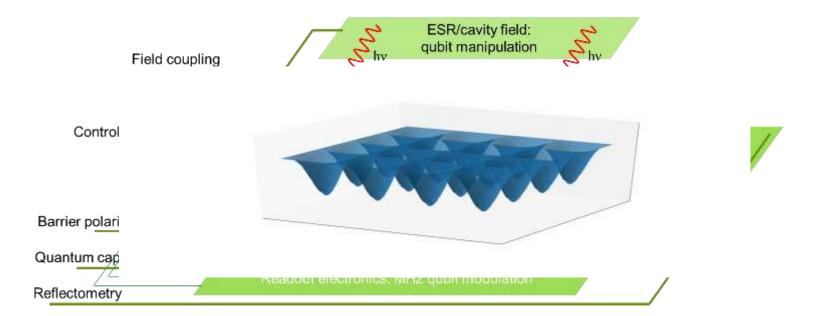

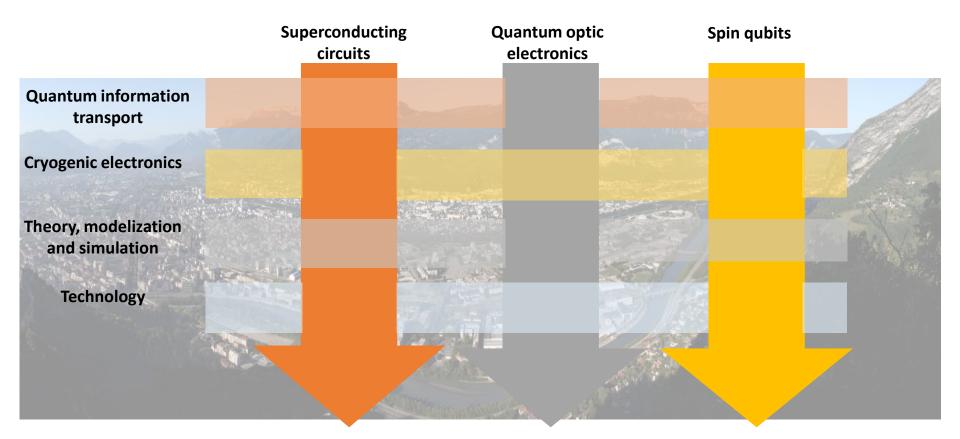

### CONTROL ELECTRONICS AND CHIP ARCHITECTURE

## Architecture definition v0 (must have)

### CONCLUSION

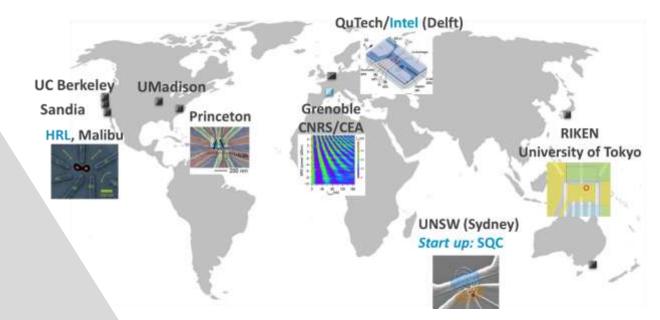

Quantum computing is a **disruptive innovation** in computing. **French** industrial and research ecosystem is **at the state-of-the-art**

#### State of the art

UNSW, 2015

### Grenoble Quantum Program

#### **Motivation & positioning**

- Become the hardware leader in terms of qubits quality & quantity

- Interlock with users ecosystem to optimize usage-hardware design

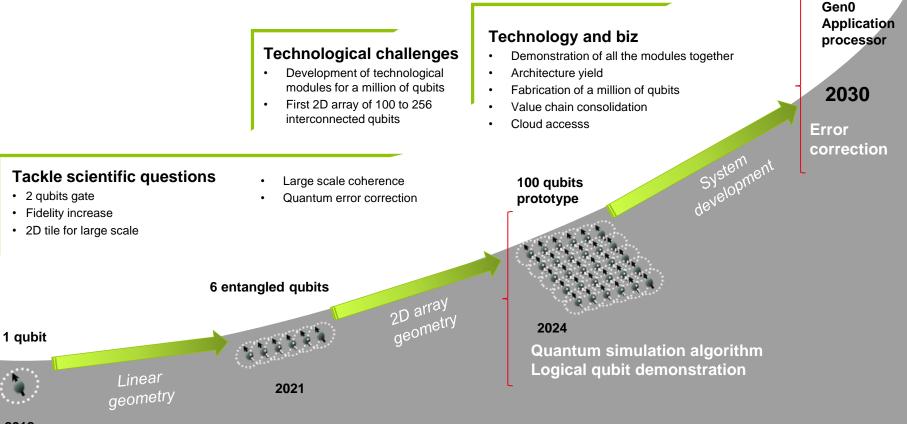

### SI SPIN QC ROADMAP

#### 2018

# Leverage collective intelligence

#### 60000 students, 100 researchers in fundamental quantum sciences

- Create the feeling of belonging to an adventure

- Leverage the physicist for risk analysis and for finding problems

- Leverage the engineering skills to propose solutions and move on (open and close doors)

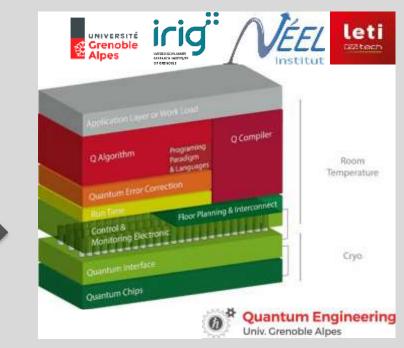

### Quantum Engineering

Univ. Grenoble Alpes

# QuantECA: Large scale quantum integration

Leti, technology research institute Commissariat à l'énergie atomique et aux énergies alternatives Minatec Campus | 17 rue des Martyrs | 38054 Grenoble Cedex | France www.leti.fr