# Highlights of The 21<sup>st</sup> International Workshop on Radiation Imaging Detectors IWORID 2019, Chania, Crete

A.Rozanov,

Aix Marseille Univ. CNRS, IN2P3, CPPM 17 February 2020

https://indico.cern.ch/event/774201 86 talks, many tens of posters

#### CMS tracker design HL LHC, Stefano Mersi

- double tracker layers to trigger on high pT tracks

- pixels design RD53 with ATLAS 25x100 um

- Macropixel-strips inner part 100 um by 1467 um,

5cm

- Strip-Srip outer part 90 um by 5 cm

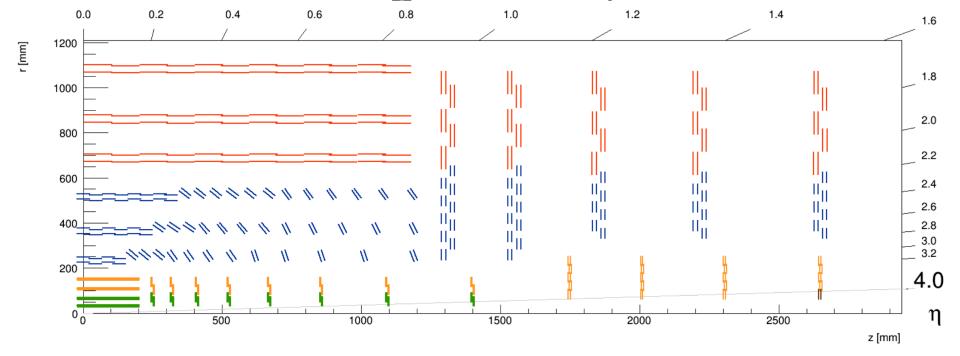

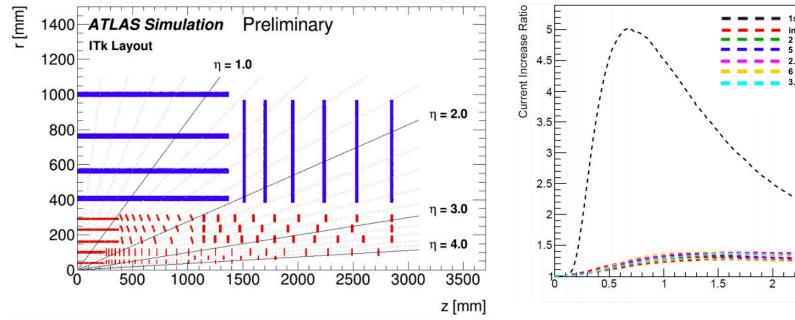

#### ATLAS ITK for HL LHC. Karola Dette

- 4 pixel layers RD53, 25x100 um and 50x50 um, n<4</li>

- 4 strip layers, 165m<sup>2</sup>, 75umx24/48 mm

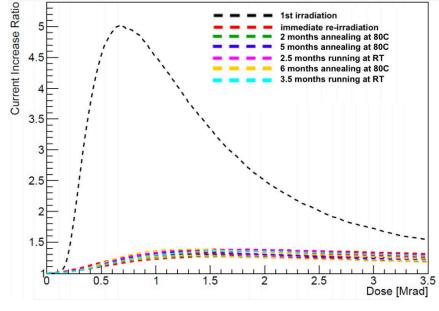

- Solve initial current problem in 130nm electronics by pre-irradiation

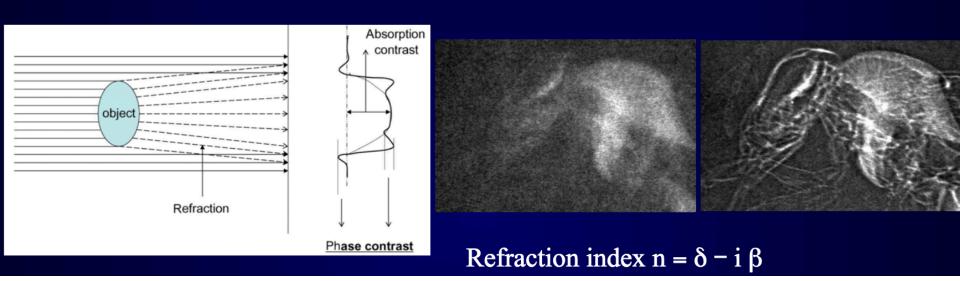

#### X-Ray Phase Contrast imaging, Fulvia Arfelli

High coherence of SR introduces Phase Contrast effect in the images

- with synchrotron radiation free space propagation phase contrast

- interference pattern between refracted and unrefracted waves produce intensity variations detected by detector

- sample to detector distance must be optimized to detect the interference pattern

- Many methods: analyzer crystal imaging, diffraction enhanced imaging, general= absorption +refraction+scatering

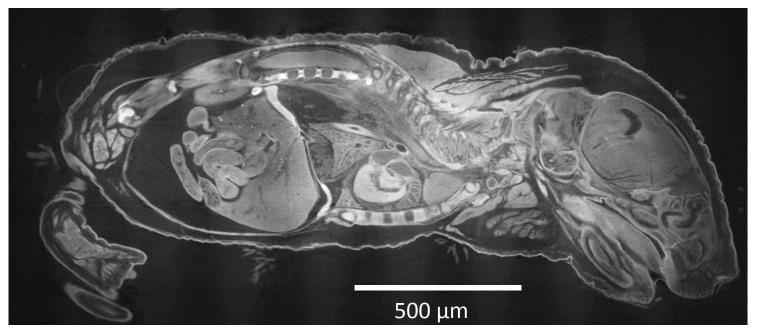

# Small animal micro-CT with TimePix Jan Zemlicka

- 300 um Si and 1000um CdTe detectors

- Threshold in each pixel above the noise

- Unlimited dynamic range, sample 1-100mm

- Resolution 0.5-50 um

### Thin CMOS pixel sensors, Marc Winter

| Detector                   | EUDET-BT                | STAR-PXL               | ALICE-ITS2                | CBM-MVD                     |

|----------------------------|-------------------------|------------------------|---------------------------|-----------------------------|

| CMOS process               | AMS-0.35 (planar, 4 ML) |                        | Tower-0.18 (4-well, 6 ML) |                             |

| $\sigma_{sp}$              | $\lesssim$ 3.5 $\mu m$  | $\gtrsim$ 3.5 $\mu m$  | $\sim$ 5 $\mu m$          | $\sim$ 5 $\mu m$            |

| $ig  \Delta_t$             | $\sim$ 115 $\mu s$      | $\sim$ 195 $\mu s$     | $<$ 10 $\mu s$            | $\sim$ 5 $\mu s$            |

| $P_{diss}$ /cm $^2$        | $\sim$ 250 mW           | $\sim$ 170 mW          | $\sim$ 35 mW              | < 50 mW                     |

| Hits/cm <sup>2</sup> /s    | $>$ 10 $^{6}$           | $>$ 10 $^6$            | $>$ 10 $^6$               | $\lesssim$ 10 $^{8}$        |

| TID                        | $\sim$ 200 kRad         | $\sim$ 200 kRad        | > 1 MRad                  | $\sim$ 10 MRad              |

| NIEL [ $n_{eq}$ /c $m^2$ ] | few 10 $^{12}$          | $\textbf{few 10}^{12}$ | $>$ 1 $\cdot$ 10 $^{13}$  | $\sim$ 1 $\cdot$ 10 $^{14}$ |

- Future needs:

- CLIC 1 Mrad, 0.3 MHz/cm<sup>2</sup>

- HL-LHC outer 80 MRad, 100-200 MHz/cm<sup>2</sup>

- HL-LHC inner 2x500 MRad, 2000 MHz/cm<sup>2</sup>

- FCC pp > 1 GRad, 200-20000 MHz/cm<sup>2</sup>

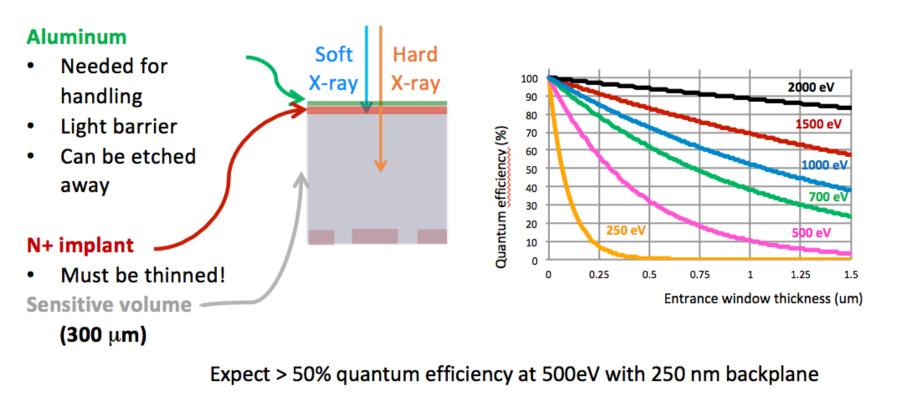

# Characterization of Monch0.3 for soft Xray applications, Sabina Alvarez

- soft X-ray FEL 250 eV- 1900 eV

- pixels 25x25 um, area 1 x 1 cm, 1kHz frame rate

- single photon resolution> 700 eV, FWHM 320 eV

- ENC 36 electrons = 130 eV

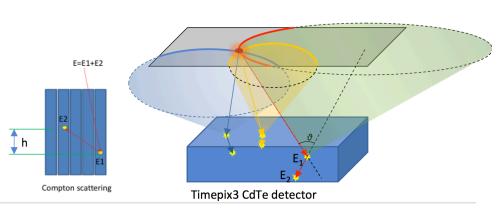

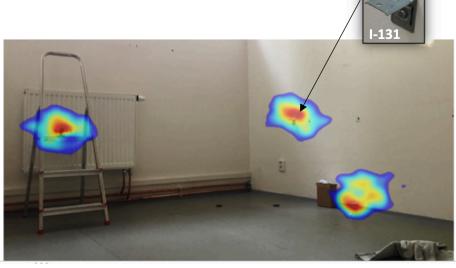

# Single Layer Timepix3 Compton Camera, Daniel Turucek

- 55 um pitch, 255x255 pixels, 1.46 ns time resolution

- pair of events happening in different depth of CdTe

1mm depth sensor

- thyroid cancer search resolution 2.5 mm (gain factor of 5), reduce dose by factor 4

- mounted on helicopter, drones, localization of radioactive wastes

#### JUNGRAU detector for XFEL, Marco Ramilli

- Dynamic Gain Switching ~110dB,~10000 10 KeV photons

- 75 um pixel pitch, 320/250 um Si thick sensor

- ASIC 256x256 pixels, array 4x2 ASICs

- 16 memory cells with >200kHz

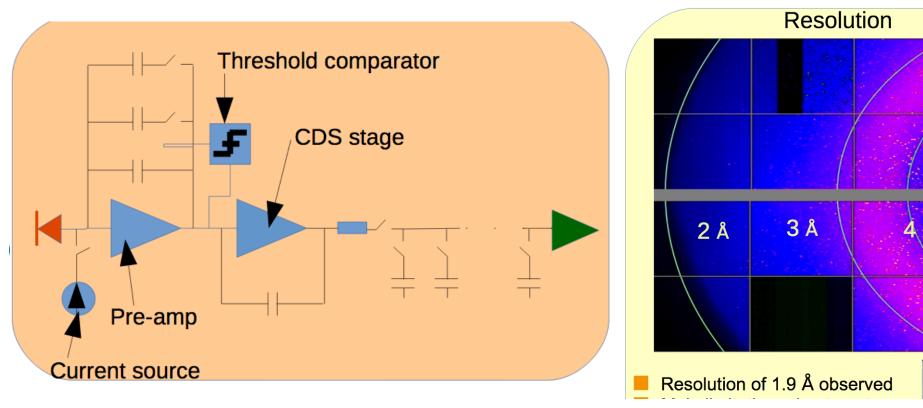

#### CMOS for e/Xray detectors Nicola Gerini

- 12 inch wafers

- LASSENA, PERCIVAL

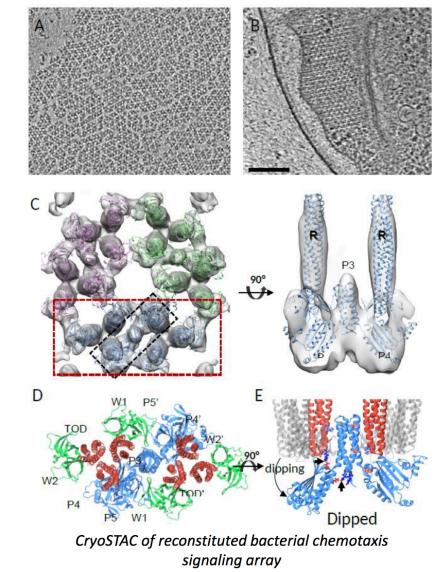

- CRYO Electron Tomography

2017 Nobel Price in

Chemestry (Dubochet, Frank,

Henderson) for biomolecules

- Electron energy 100 KeV instead of 300 KeV as sigma elastic is bigger ?

- 50x50 um, 2048x2048 pixels, 2500 frames/s, 200 um thick sensor, area 100 cm<sup>2</sup>

#### **Cryo Electron Tomography**

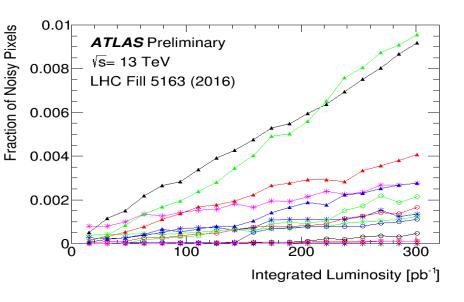

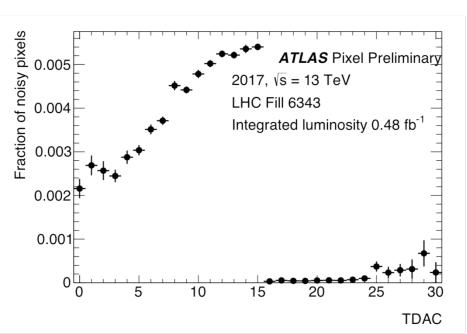

#### SEU upsets in ATLAS IBL AlexandreRozanov

- Correlation of noisy pixels with initial TDAC value.

- Low TDAC values correspond to high thresholds.

- Biggest fraction of the noise happens after SEU flip 0->1 of MSB of TDAC, which sharply reduces the pixel threshold and increases the noise.

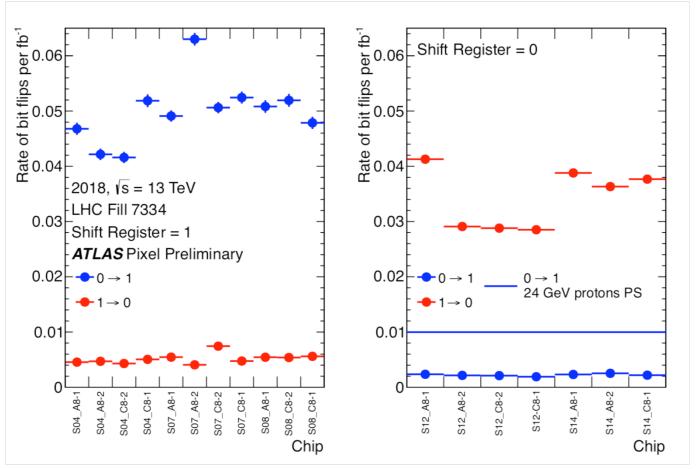

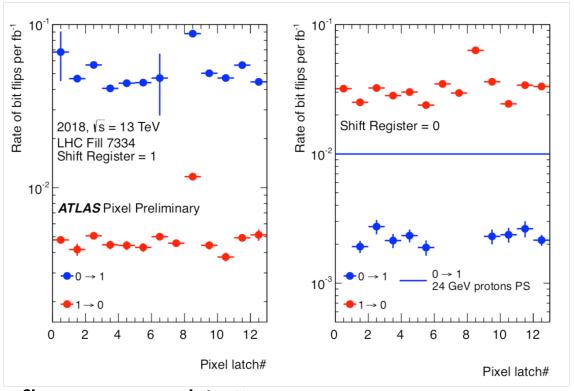

#### Distinguish SET from SEU

- Read back local memory at the end of fill and compare with initial settings

- Separate modules with Shift Registers (SR) "1" and "0"

- Rate of flip flops versus chip #

- Glitches(SET) on LOAD line dominate 0->1 flips when SR=1

- Glitches(SET) on LOAD line dominate 1->0 flips when SR=0

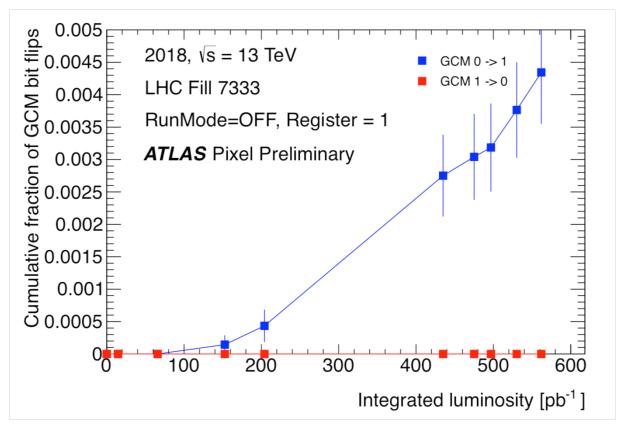

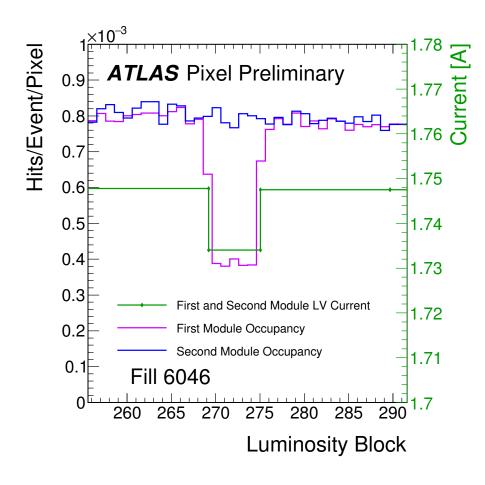

### Global Configuration Memory

- Read back of the tripled Global Configuration Memory (GCM) during the LHC fill

- 0->1 transitions are dominated by glitches (value of the loaded last register was xFFFF)

- 1->0 transitions not observed, triple memory suppress real SEU

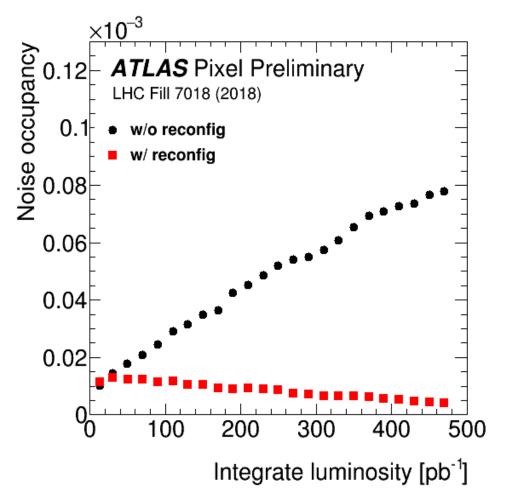

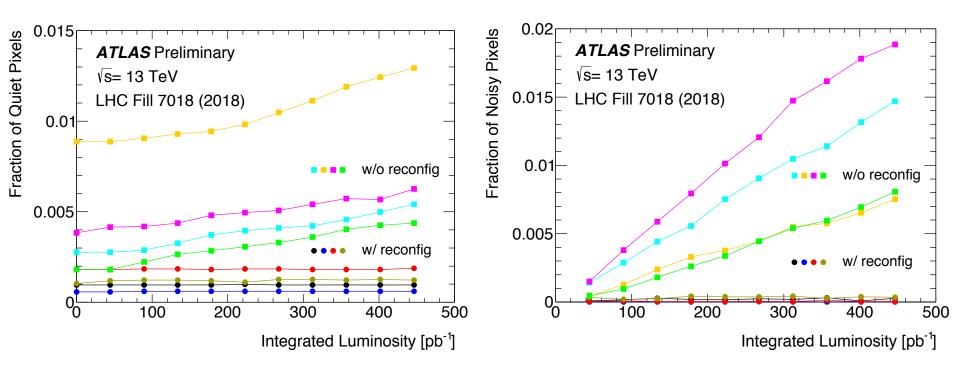

#### Noise with reconfiguration in test run

- Noise in IBL high η modules with and without reconfiguration

- Decrease of the noise with reconfiguration is due to the more frequent (11 min) refreshing per unit of luminosity

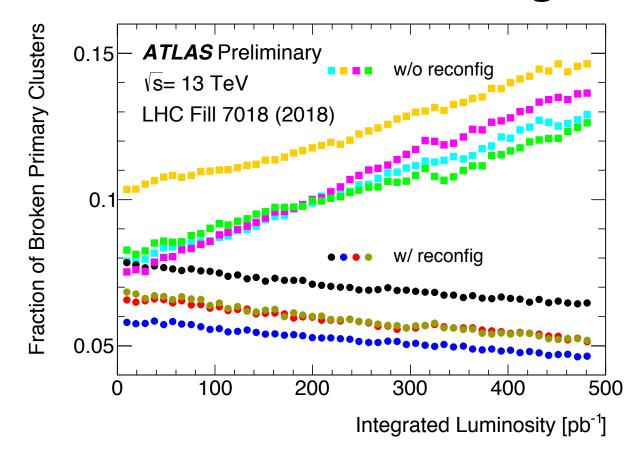

#### Broken clusters with reconfiguration

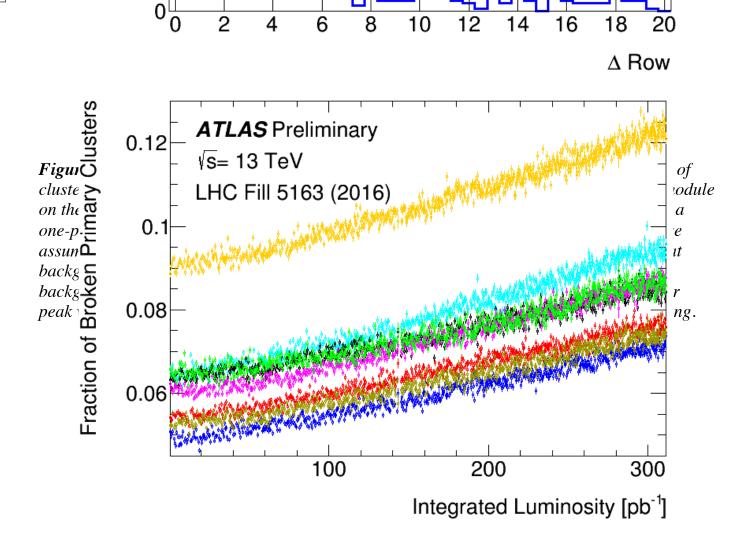

Fraction of broken clusters with and without reconfiguration

#### Conclusions on ATLAS SEU

- ATLAS Pixel detector with IBL at R=3.3 cm efficiently operates at high luminosity with expected SEUs.

- SEUs in global memory create silent modules, current jumps, occupancy jumps, de-synchronizations.

- Global Configuration Memory SEUs mitigated in 2017 by refreshing the memory during ECR every 5 seconds without dead time.

- SEUs in Local pixel memory create quiet pixel, broken clusters, noisy pixels.

- Local pixel memory bit flips are dominated by glitches (SET) on the LOAD line of DICE latches.

- During few test runs in 2018 local pixel memory was gradually refreshed during ECRs with the full period of 11 minutes. Complete cure of quiet pixels, broken clusters and noisy pixels due to SET/SEU.

- Plans to fully deploy the gradual refreshing of local pixel memory in IBL FE-I4 during ECR in Run3 in 2021.

- For future pixel FE electronics design: suppression of glitches (SET) could be as important as SEU hardness.

- The tests on 24 GeV CERN PS facility is a good method for SEU/SET measurements and design validation.

### Additional

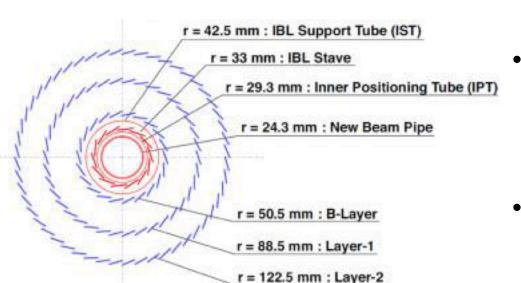

# ATLAS IBL Frontend ASICs at the Large Hadron Collider at CERN

- LHC delivered in 2015/2018 total of 156 fb<sup>-1</sup> integrated luminosity to ATLAS for 13 TeV pp collisions.

- Maximum of 2.1 10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup> peak stable beam luminosity.

- Up to 0.77 fb<sup>-1</sup> luminosity delivered per LHC fill.

- Pixel detector operated at extremely high-radiation environment, in particular Insertable B-Layer (IBL) at R=3.3 cm received the dose  $1.03\ 10^{15}\ 1\ \text{MeV}\ n_{eq}\ \text{cm}^{-2}$ .

- For introduction to ATLAS

Pixel and LHC see talk Paolo

Sabatini

- IBL pixel front end chip FE-I4-B in 130 nm technology was designed with Single Event Upset (SEU) hard configuration memory.

- Inside the pixels Dual Interlocked Cell (DICE) latches were used.

## Word 0 Memory array 32 x 16 Word 32 Data in<15:0>

T3 Figure 26: Diagram of the CNFGMEM block.

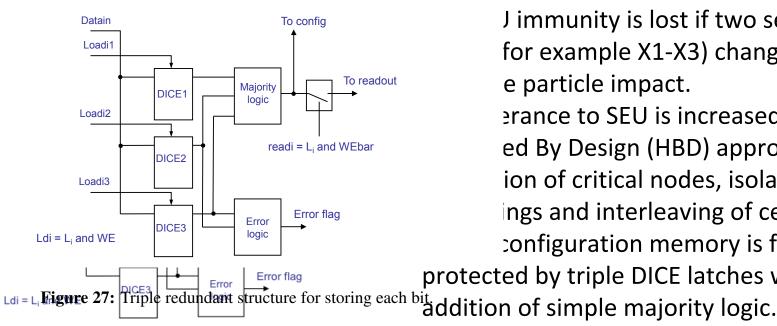

#### ches

latches have redundant storage nodes restore the cell original state when an error is induced in a single node. s coupled inverter latch structure with nodes (X1-X4) stores data in two pairs of plementary values.

.. positive upset pulse on X1, than transistor MP2 is blocked, avoiding propagation of this perturbation to node X2.

> J immunity is lost if two sensitive for example X1-X3) change the state e particle impact.

erance to SEU is increased by ed By Design (HBD) approach: spatial ion of critical nodes, isolated wells, ings and interleaving of cells. configuration memory is further

19

protected by triple DICE latches with

#### SEU in Global Registers

- Global Registers (GR)

corruption has big impact

on module operation:

- change of the low voltage consumption

- drops in occupancy

- silent modules

- desynchronized modules.

- Refreshing of the GR restore proper function of the module.

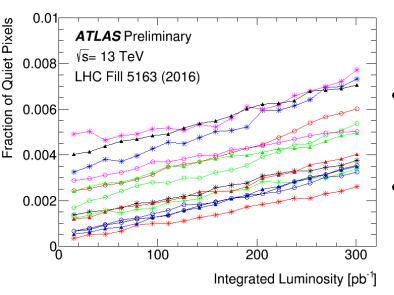

#### SEU in Local Pixel Memory

- Pixel local configuration: 13 bits/pixel: Enable, TDAC (thresholds 5 bits), FDAC (feed back current 4 bits), HitBus, Injection Caps (2 bits).

- SEU DICE cross-section measured for FE-I4-A in the 24 GeV proton test beam is 1.1 10<sup>-15</sup> cm<sup>-2</sup> (enable bit, 0 ->1 transition).

- Hadron flow at IBL predicted by PYTHIA/ FLUKA simulation tuned to ATLAS data: 91.0 10<sup>11</sup> cm<sup>-2</sup> fb<sup>-1</sup> hadrons with E>20 MeV at planar modules.

- Expect 274 pixels/fb<sup>-1</sup>/chip SEU flips of Enable bit 0->1

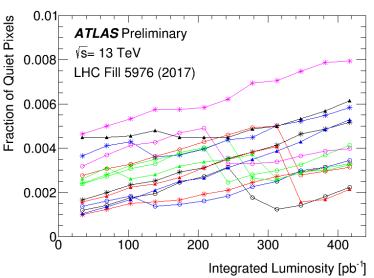

- Enable bit SEU flip 1->0 : "Quiet" pixel.

- 2016: no automatic recovery actions, linear rise of quiet pixels

- 2017: automatic recovery actions drops the number of quiet pixels in the middle of the fill.

- Quiet pixels cause clusters to be broken

- In high η modules average cluster length is 9

- Fraction of broken clusters versus luminosity

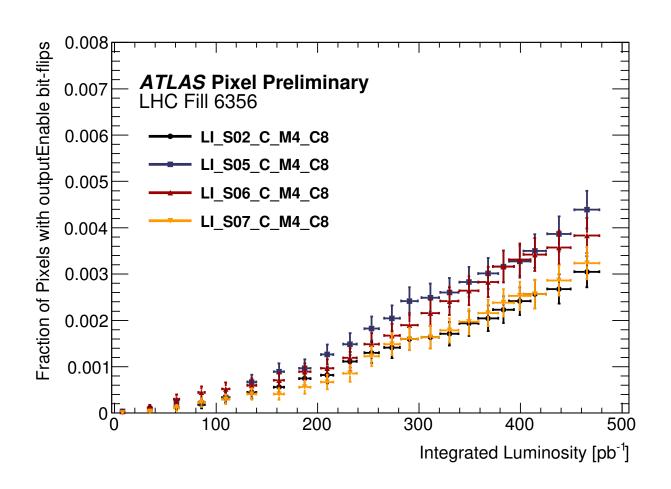

#### SEU in local Enable bit

- Test with four high η modules

- Enable bits initially set to "0" (masking all pixels in the module)

- During LHC fills some Enable bits are flipped by SEU to "1"

### SET nature of flips for different bits

- Rate of flip flops versus bit #

- Glitches(SET) on LOAD line dominate 0->1 flips when SR=1

- Glitches(SET) on LOAD line dominate 1->0 flips when SR=0

- Uniform rate for most of the bits, except HitOr (bit# 8)

- HitOr has very special layout, as interconnection of all pixels

- 24 GeV proton results contaminated by SET due to SR flips

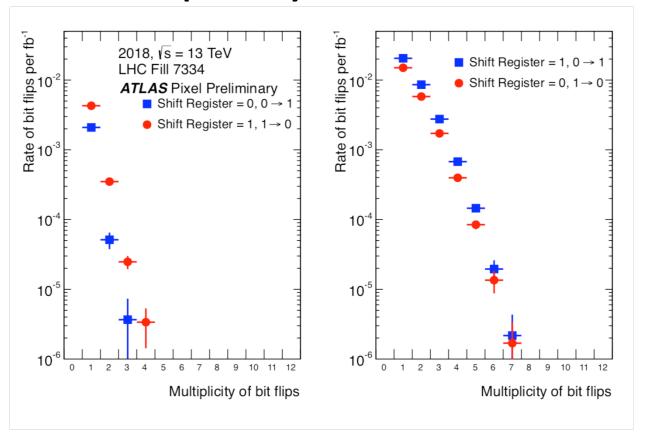

#### Multiplicity of SEU/SET

- Are the glitches on LOAD line common to several bits or individual?

- Multiplicity of bit flips are peaked at "1", so glitches are mainly individual (pairs of transistors T1-T2 or T3-T4)

- Longer tails in SET may indicate small multi-bit contribution

#### **Absolute SEU Cross-sections**

| Beam, SEE type                                              | Transition | SR<br>value | Rate per fb <sup>-1</sup> (stat./syst.) | Cross-section 10 -15 cm <sup>2</sup> |

|-------------------------------------------------------------|------------|-------------|-----------------------------------------|--------------------------------------|

| LHC: Mainly SEU                                             | 0->1       | 0           | 0.22 ± 0.01 ± 0.09 %                    | 0.24 ± 0.13                          |

| LHC: Mainly SEU                                             | 1->0       | 1           | 0.46 ± 0.01 ± 0.19 %                    | 0.51 ± 0.26                          |

| LHC: Mainly SET on Load line                                | 1->0       | 0           | 3.07 ± 0.02 ± 0.80 %                    | 3.39 ±1.34                           |

| LHC: Mainly SET<br>On load line                             | 0->1       | 1           | 4.68 ± 0.03 ± 1.21 %                    | 5.16 ±2.04                           |

| 24 GeV protons:<br>Mostly SEU with<br>some SET<br>admixture | 0->1       | 0           | n.a.                                    | 1.10                                 |

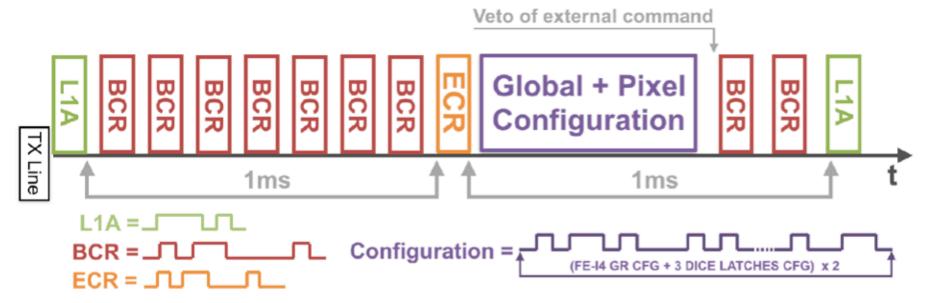

#### Reconfiguration mechanism

- Global Configuration Memory refreshed periodically since August 2017: dramatic decrease of silent chips, current jumps, occupancy jumps, de-synchronizations in IBL

- A 2ms time window used by ATLAS to send Event Counter Reset (ECR) signal to detector electronics was exploited to perform such reconfiguration:

- ATLAS ECR period is 5 seconds

- Reconfiguration during ECR didn't add any extra dead time to ATLAS

- Bitstreams for local memory reconfiguration are much larger than for Global Configuration Memory => trying by splitting in several ECR cycles => full reconfiguration during 11 minutes

- Local memory refreshing tested in few LHC fills => see results on next slides

### Quite and Noisy with reconfiguration

- Quite and Noisy pixels with reconfiguration in the test run

- Eight high η modules under test: four reconfigured

and four not reconfigured