# The WaveCatcher Systems: a Family of Powerful and Low-Cost Digitizers

cea

Dominique Breton, C.Cheikali, Jihane Maalmi, Pascal Rusquart - CNRS/IN2P3/LAL (Orsay) Eric Delagnes - CEA/IRFU (Saclay)

# The WaveCatcher systems:

2 to 64-channel 12-bit 3.2GS/s oscilloscope-like digitizers, close to the picosecond level in timing precision

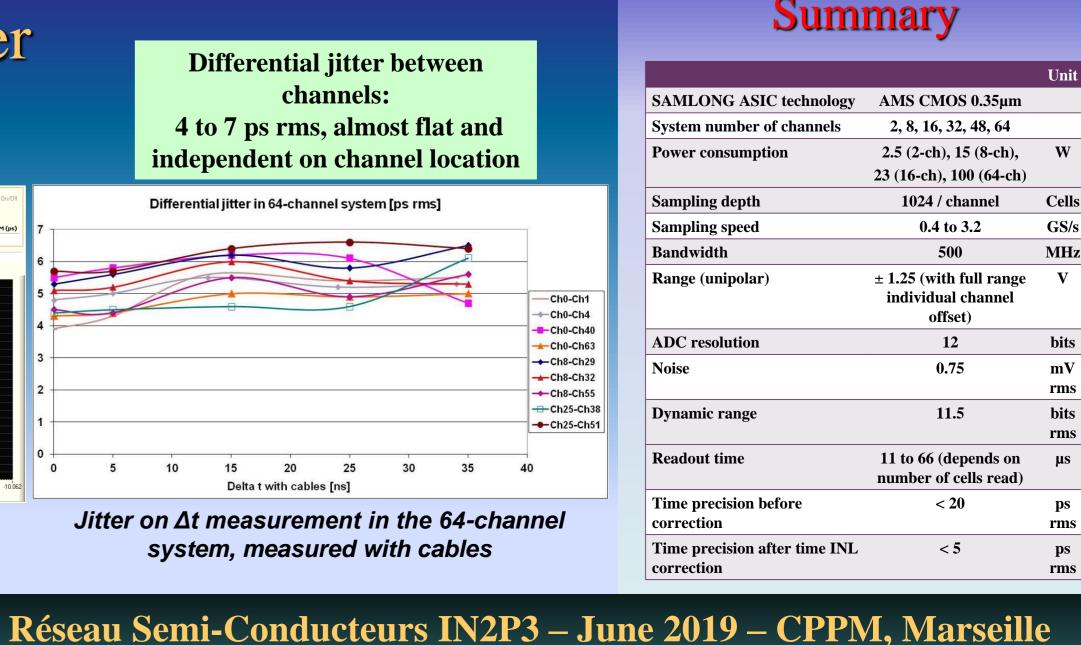

- Based on the **SAMLONG** Analog Memory ASIC

- Sampling rate ranging between 400 MS/s and 3.2GS/s.

- 1024 samples/channel

- 12 bits of dynamic range, working on 14 bits

- Small signal bandwidth > 500MHz

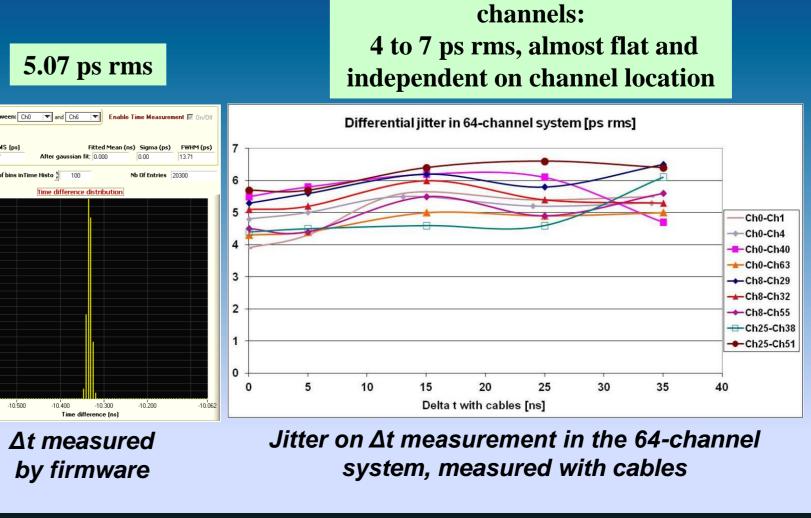

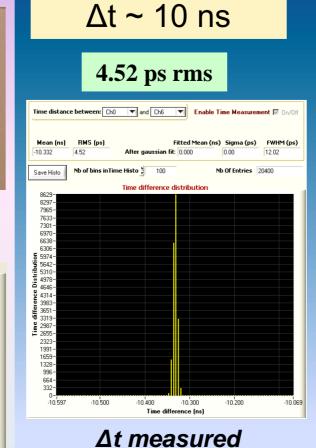

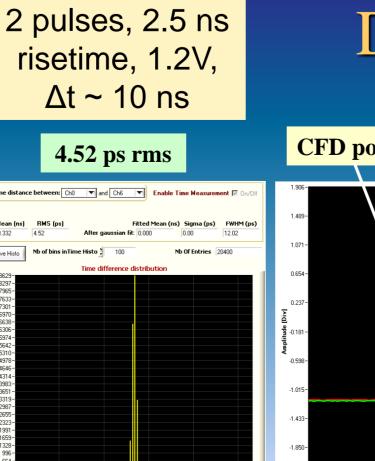

- Sampling jitter < 5 ps rms at the system level

- Up to 64+8-channel synchronous system

- Advanced Oscilloscope-Like Software (Plug and Play)

- Embedded feature extraction: Baseline, Peak, Charge, CFD (TDC-like mode) ....

# 2 channels 8 channels 16 channels Board **USB** powered **Desktop** or Desktop

CAEN: 64 channels 8 to 16 channels **Mini-Crate**

### Why Analog Memories

Modern high-end ADCs have broken the GS/s frontier but their implementation becomes difficult. Their companion FPGAs have to be high end and the cost per channel explodes. The use of analog memories like **SAMLONG** makes it possible to perform high quality digitizing at low cost and with a low power consumption.

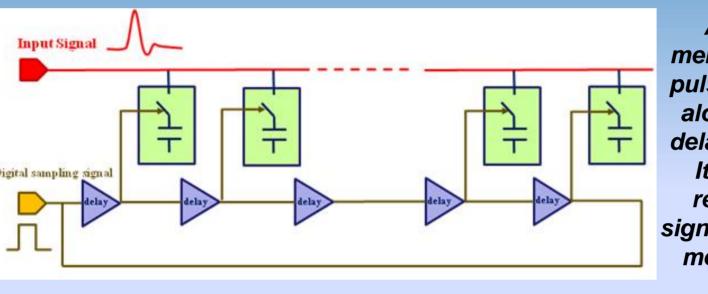

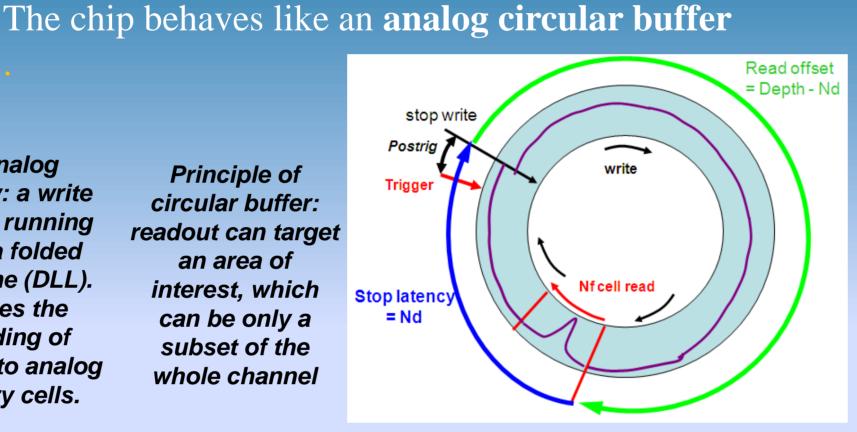

An analog memory: a write pulse is running along a folded delay line (DLL). It drives the can be only a recording of subset of the signal into analog whole channel memory cells.

Principle of circular buffer: readout can target an area of interest, which

## at 3.2GS/s ADC Structure patented in 2001

Some advantages of the matrix structure:

- Servo-controled DLLs permit accurate timing, stable with temperature.

- Input amplifier : stable high input impedance.

- 1 Amplifier/Line: better Bandwidth/

- Consumption Factor Of Merit

- Channel information spread over numerous lines permits fast readout.

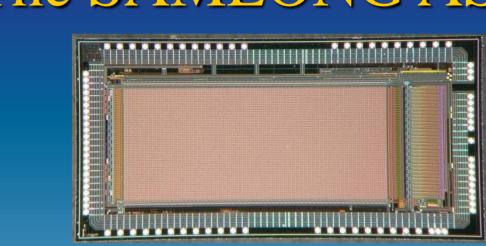

### The SAMLONG ASIC

- AMS CMOS 0.35µm technology.

- 2 differential channels with 1024 cells.

- Configurable by a SPI-like serial link.

- Embedded DACs for internal tuning

- "Built-in TDC"

Readout:

12 to 14 bits

10 to 20 MHz

- 100,000 transistors, 11 mm<sup>2</sup>

- TQFP 100 14x14 package

- New: lower power and noise version has been designed (SAMLONG\_D) and will soon be mounted on new mezzanine boards

2-Slot MotherBoard

**MotherBoards**

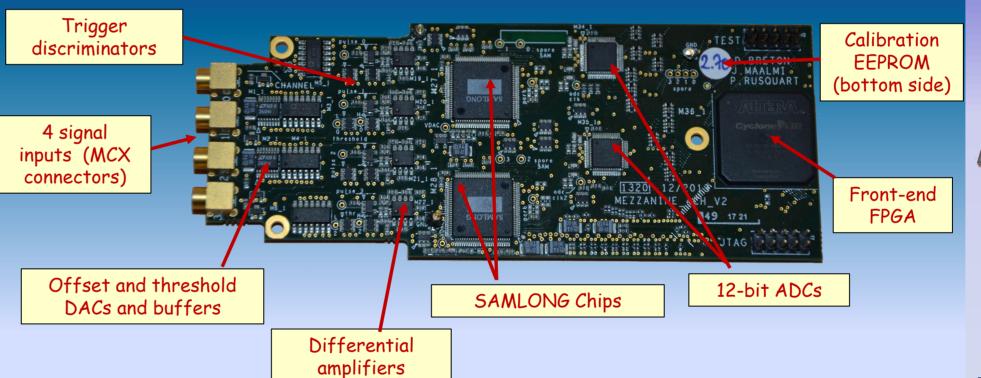

#### Several modes Trigger & Readout of triggering are available in the WaveCatcher Trigger architecture (common mode) boards and systems. all front-end boards Backplane • Each analog input is discriminated by a comparator with an individual DACprogrammable threshold. • Each discriminator output

Controller board

(Mezza\_mother)

## System Features

The Sampling MATRIX

Our sampler chip is made of a matrix of L lines and

C Columns of analog memory cells. Its main clock

doesn't exceed 200 MHz. It is virtually multiplied

by 16 inside the chip thanks to the 64 vertical **servo**

controlled delay line loops (DLL). The input signal

is split in 16 branches, each housing a voltage buffer.

- to each channel

- Individual trigger discriminator on each

- each channel

- modes for **coïncidence** triggering

- as additional analog inputs

- One **pulse generator** on each input • External clock input for multi-board

- applications (8, 16 & 64-channel)

- interfaces (8, 16 & 64-channel)

- Possibility to upgrade the firmware via

- Embedded signal amplitude and baseline

- Embedded digital CFD for time measurement

### • Possibility to add an individual DC offset

- Integrated raw trigger rate counter on

- External & internal trigger + different

- 2 **extra** memory **channels** for « digital » signals on 16-channel board => can be used

- Embedded USB, UDP and Gigabit optical

- Embedded **charge** extraction

- extraction

# 4-Channel Front-End mezzanine

**Application Examples** These acquisition systems are used in test benches or experiences in a multitude of labs,

- projects and fields: • particle beam monitoring

- accelerators

- R&D on detectors

- study of new fast photo-detectors (SiPMs, MCP-PMTs, MeshAPDs) • new generation of detectors (LGAD, pico-second Micromegas, diamonds) for high energy

- physics • research on TOF-PETs for medical imaging

- particle physics detectors...

#### through USB(2.0), **UDP** or **Optical** links (Ethernet over optical) • The next step is to develop the 2.5

The control and

readout is possible

Gbits/s USB3 interface. Firmware can be

uploaded via USB using the fwloader tool developed at LAL (C.Cheikali)

WaveCatcher Main Panel

Control and Readout

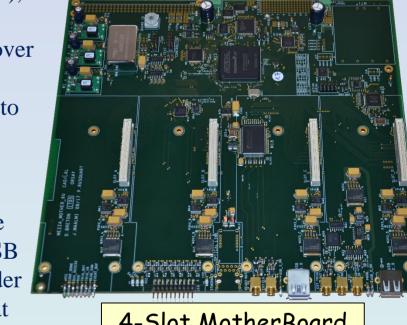

motherboards have

been developed for

They permit separating

from the specific front

the acquisition part

housing 2 or 4

mezzanines.

end part.

4-Slot MotherBoard

Online XY plot

#### A Custom Control & Readout Architecture and Protocol

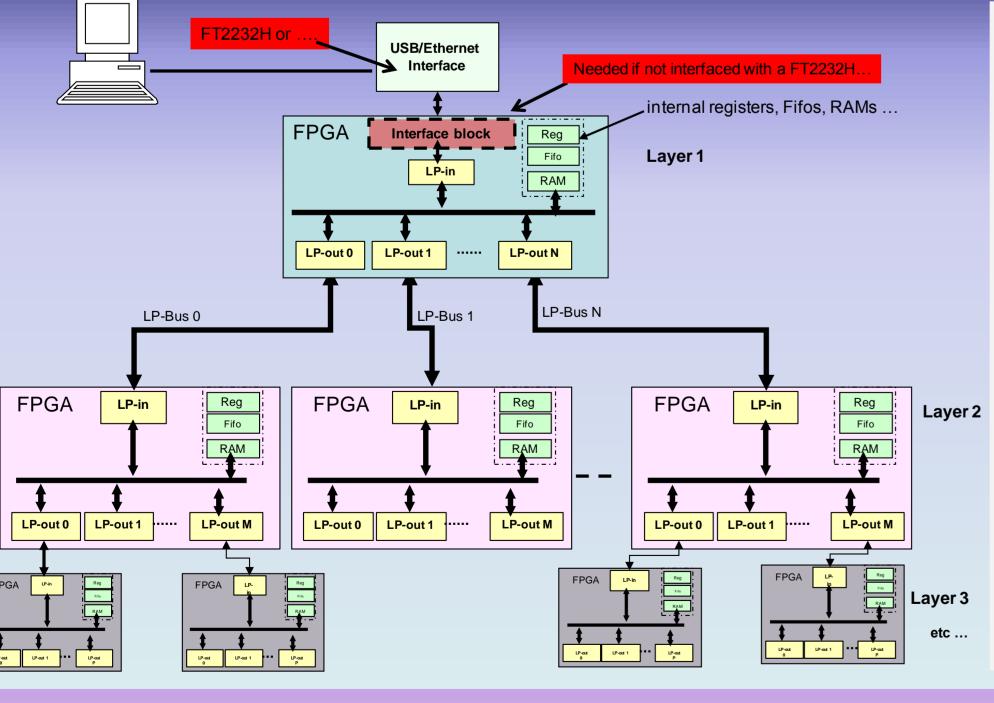

- The Multi-Layer Parallel Interface aims at simplifying the communication between FPGAs located at different levels in the system.

- The same firmware decoding blocks are implemented in the FPGAs independently of their hierarchy level in the system (same or different boards).

- Software Libraries: Layer 2 LAL\_USB\_ML and LAL\_UDP libraries have been developed to handle the ML communication protocol. UDP transfers are secured with warranty of **no data loss** thanks to a continuous handshake between the firmware and the library.

# Dedicated software and C-libraries

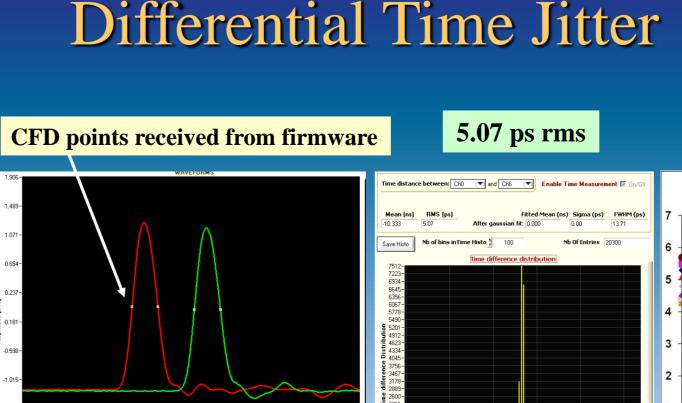

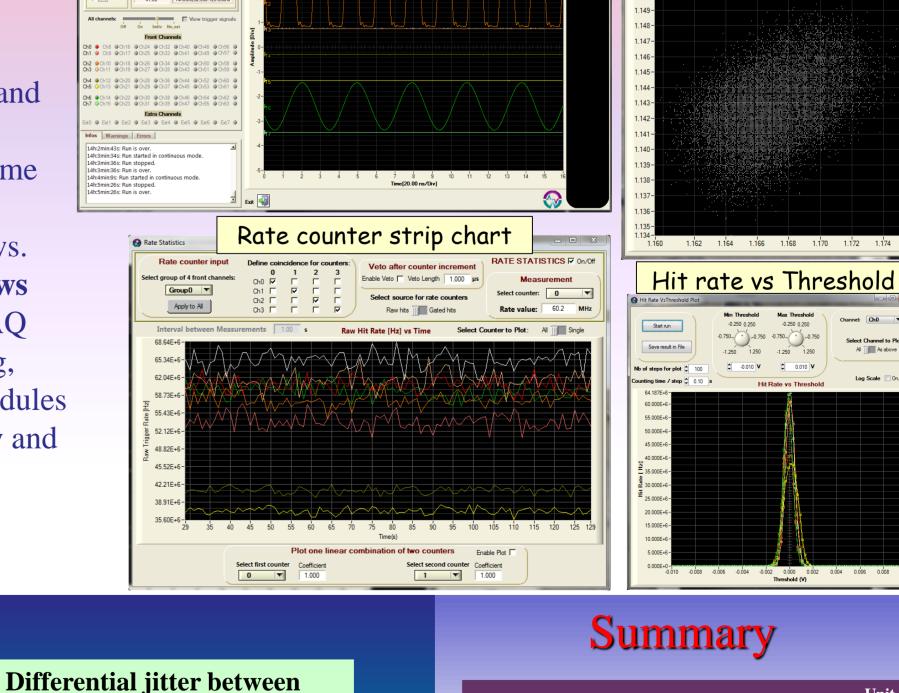

A dedicated **Software**, compatible with all WaveCatcher modules (from the 2-channel module to the 64-channel crate) has been developed under Labwindows CVI. It permits configuring all the available parameters on the modules, visualising and saving data (ASCII or Binary) but also making different online histogramming of: Differential Time Jitter, Amplitude, Charge, Baseline, XY plots... Unfortunatey, this Software runs only on Windows.

A dedicated C-library, compatible with Windows and Linux allows the users to build their own DAQ software (via USB or UDP). It permits initializing, configuring and reading out the WaveCatcher Modules Documentation is available for Software, Library and

Modules. A dedicated website houses all information and updates for Software, Firmware and Library.

Rate counter strip chart

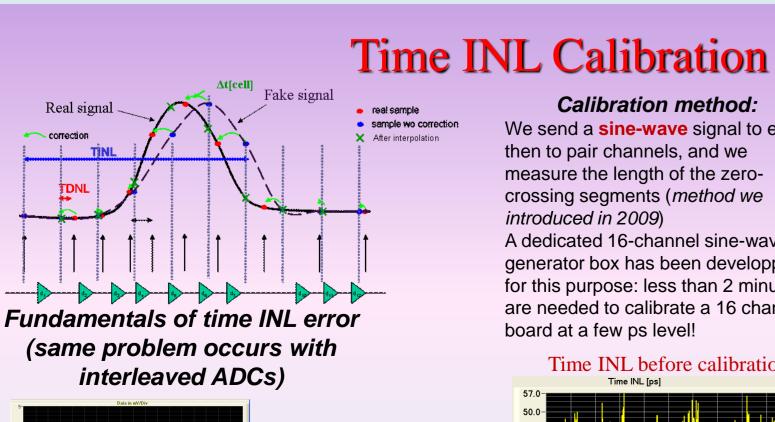

**Zero-crossing**

segments of the

sine-wave are

considered as

straight lines

(or their logical OR or AND)

can be used for triggering the

board (pos or neg edge

individually selectable)

Calibration signal generator Calibration method: We send a **sine-wave** signal to even then to pair channels, and we measure the length of the zerocrossing segments (method we introduced in 2009) A dedicated 16-channel sine-wave generator box has been developped for this purpose: less than 2 minutes are needed to calibrate a 16 channel board at a few ps level! Time INL before calibration

by software

The 2 pulses recorded by the

WaveCatcher board