# **SAMPIC: a 16-channel Waveform-TDC** for picosecond time measurement

D. Breton, O. Lemaire, J. Maalmi, P. Rusquart, P. Vallerand – CNRS/IN2P3/LAL Orsay

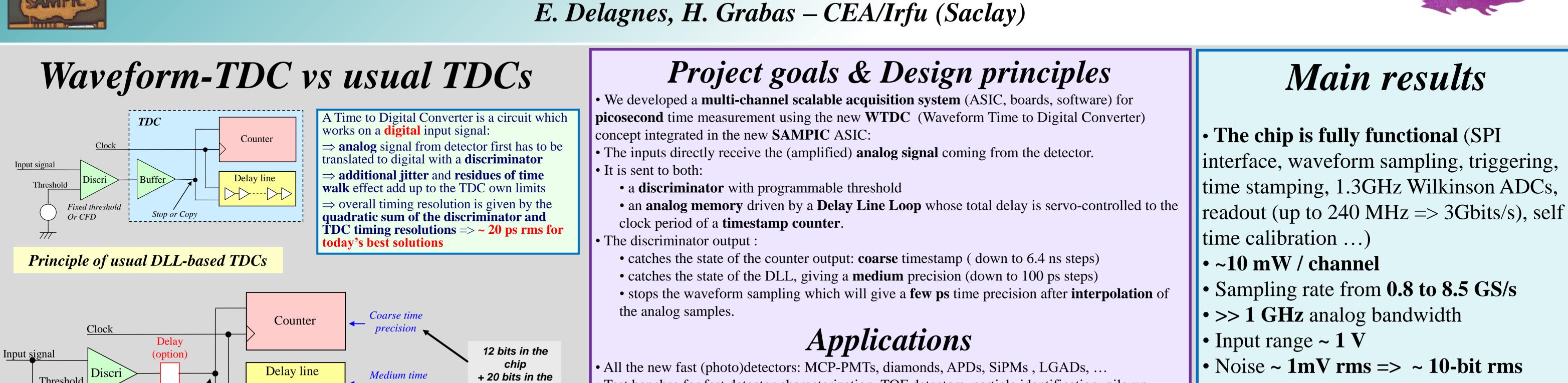

#### **Principle of the Waveform TDC (patented)**

An analog memory is added in parallel with the delay line. It samples the input signal which can now be analog and permits performing an interpolation of the samples recorded on the latter.  $\Rightarrow$  the discriminator is no longer in the critical timing path  $\Rightarrow$  time resolution can reach a few ps rms, even on small analog signals !

FClk 🗖

In15

DLL (64 outputs)

. . . . . . . . . . . .

Channel #0

. . . . . . . . . . . .

SCA (64 cells

ZOI Finder(cell

ADCs & Mem

Channel #15

SAMPIC block diagram

Counter

Ring Oscillator + Gray counter

C Read

Ch to Conv

Ch to

Data

Convert

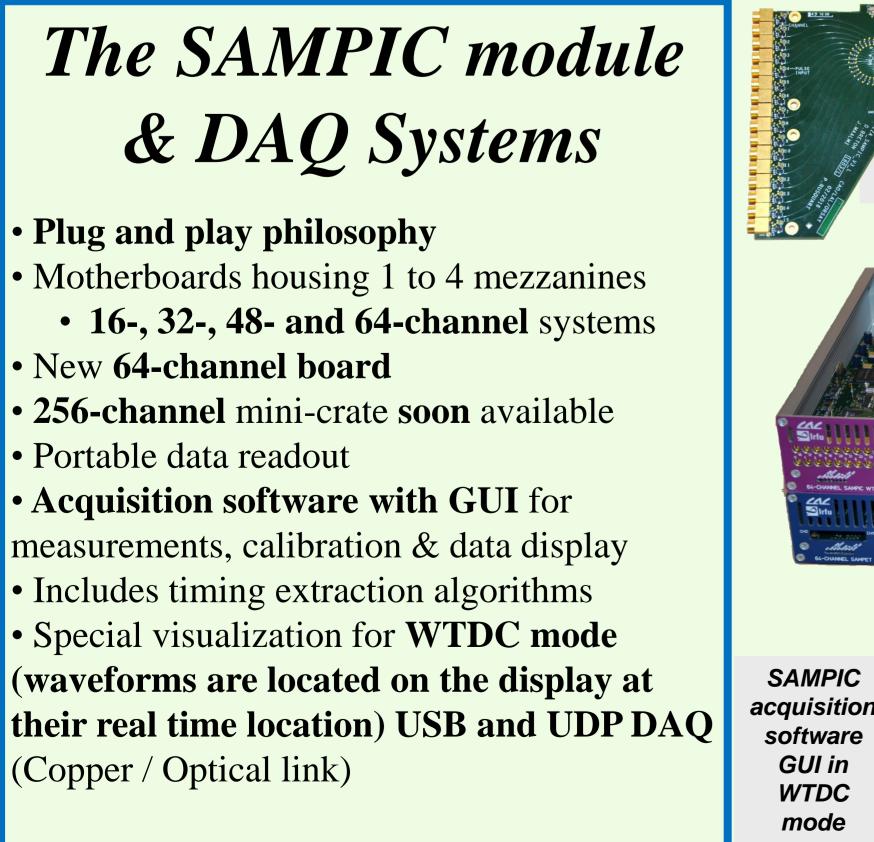

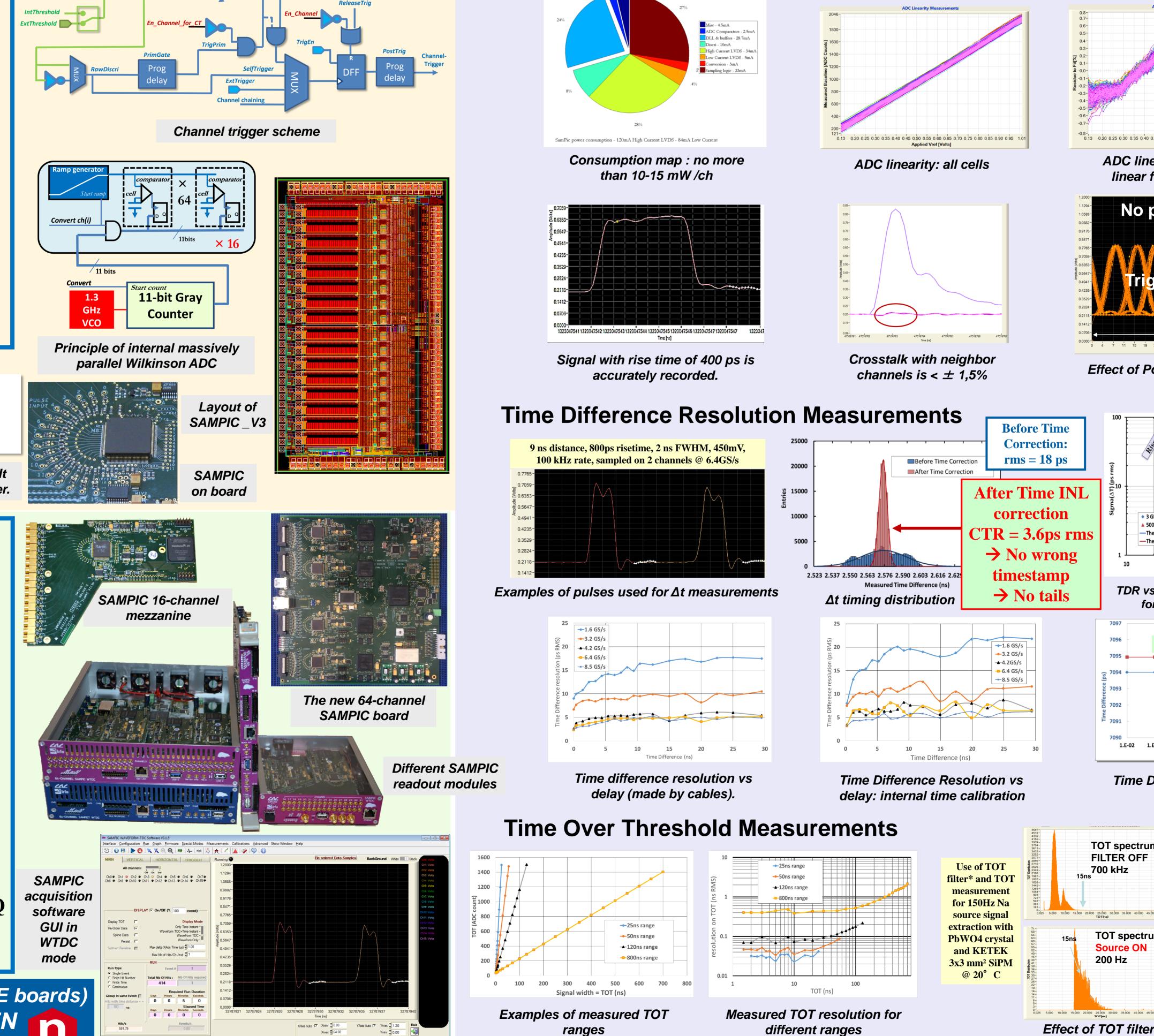

## The SAMPIC ASIC

- **16 single-ended channels**:

- Independent and self triggered (or Central Majority Trigger, or External Trigger)

- 64 analog sampling cells/ch

- One 11-bit ADC/ cell (total : 64 x 16 = 1024 on-chip ADCs)

- One common 12-bit Gray counter

- (@160MHz) for coarse time stamping

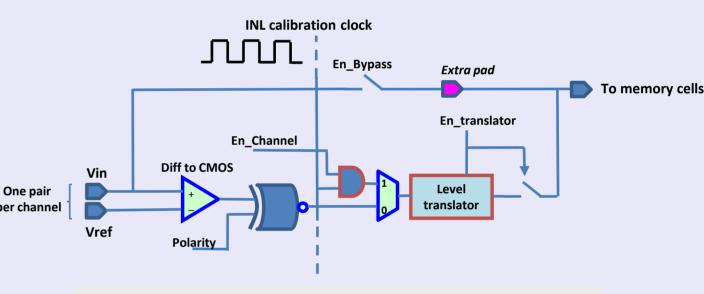

- One common servo-controlled DLL: (from 1,6 to 10 GS/s) for medium precision timing & analog sampling

- One common 11-bit Gray counter running @ 1.3GHz and used for the massively parallel

• Test benches for fast detector characterization, TOF detectors, particle identification, pile-up rejection, TOF-PETs, muon detectors, ...

#### **Project** schedule

• Project started in January 2012. May 2013: submission of SAMPIC\_0, demonstrator ASIC for technology evaluation & validation of the WTDC principle...

• November 2014: submission of SAMPIC\_V1 with a few bug corrections and new design of the analog sampling cell => better linearity and dynamic range

• November 2015: submission of SAMPIC\_V2 with advanced features (input block, 16-bit timestamp, gated trigger coincidence, independent channel ADCs, TOT measurement & filter ...) • November 2016: submission of SAMPIC\_V3 with a few bug corrections and addition of other advanced features (self calib, ping-pong, channel chaining, trigger multiplicity, smart posttrig, ...) • December 2017: submission of SAMPIC\_V3D with the last corrections. 1400 chips produced.

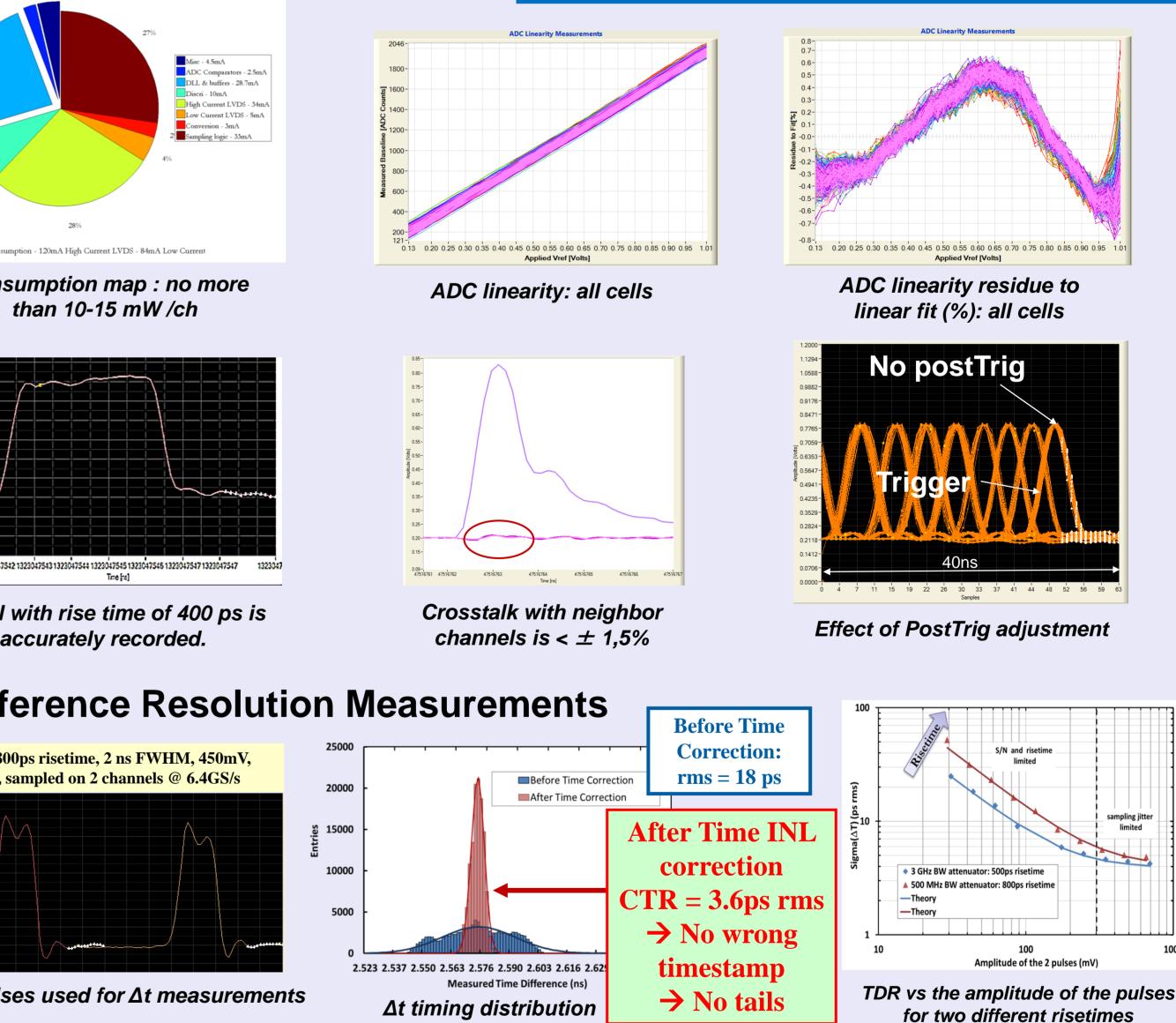

### **Performance Summary**

|                                                                         |                                       | U    |

|-------------------------------------------------------------------------|---------------------------------------|------|

| Technology                                                              | AMS CMOS 0.18µm                       |      |

| Number of channels                                                      | 16                                    |      |

| Power consumption (max)                                                 | 180 (1.8V supply)                     | n    |

| Discriminator noise                                                     | 2                                     | mV   |

| SCA depth                                                               | 64                                    | С    |

| Sampling speed                                                          | 0.8 to 8.5 (10.2 for 8 channels only) | G    |

| Bandwidth                                                               | >>1                                   | G    |

| Range (unipolar)                                                        | ~ 1                                   |      |

| ADC resolution                                                          | 7 to 11 (trade-off time/resolution)   | b    |

| SCA noise                                                               | < 1                                   | mV   |

| Dynamic range                                                           | > 10                                  | bits |

| Conversion time                                                         | 0.1 (7 bits) to 1.6 (11 bits)         |      |

| Readout time / ch @ 2 Gbit/s (full waveform)                            | < 450                                 | 1    |

| Single Pulse Time precision before correction (4.2 to 8.5 GS/s)         | < 15                                  | ps   |

| Single Pulse Time precision after time INL correction (4.2 to 8.5 GS/s) | < 3.5                                 | ps   |

dynamic range

• Conversion ranges from 7 bits (100ns) to 11 bits (1.6µs)

TOT measurement and filter between 2.5 and 700 ns.

Single channel time resolution: ~ **3.5 ps rms**

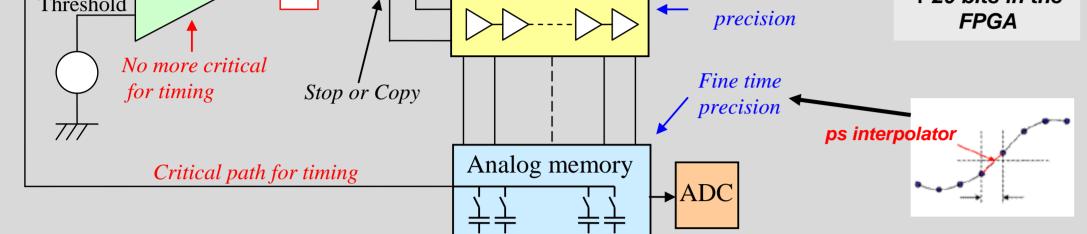

#### SAMPIC new input block

In order to permit performing a standalone calibration and dealing with small differential digital signals, the chip houses a dedicated input block on each channel. The latter includes a fast discriminator and edge selection. It can be switched off and **bypassed** in order to retrieve the usual analog waveform recording mode.

Simplified scheme of SAMPIC input block

No noticeable effect ....

-- DeltaT (ps)

1.E+01

Event Rate (kH)

Time Difference Resolution vs

input signal rate

TOT spectrum

TOT spectrum

Source ON

200 Hz

FILTER OFF

700 kHz

Resolution on DeltaT (ps rm

1.E+02

**TOT** spectrum

**FILTER ON**

Source OFF

60 Hz

0.025 5.000 10.000 15.000 20.000 25.000 30.000 35.000 40.000 45.000 49.

3.2GSPS, 15ns TOT

Source ON

Wilkinson ADC conversion (7 to 11 bits) • Several trigger modes available, including majority trigger

• Integrated TOT measurement & Filter \* • Integrated smart readout: 12-bit LVDS readout bus (running up to 240 MHz)

• **SPI Link** for register • Technology: AMS 0.18µm CMOS, now

moving to TSI 0.18µm

- Mixed analog/digital design

- Low cost, low leakage

- High end technology

- Size: **8 mm**<sup>2</sup>

- Package: 128-pin QFP, pitch of 0.4mm

Principle of the single 64-cell DLL driving the 16 channels. It ensures a constant width to the write pulse even after trigger.

New SAMPIC modules (desktops & VME boards) will soon be developed by CAEN

\* The TICAL ERC project (grant number 338953 from EU; PI: Paul Lecoq) has also contributed to the developments of the TOT features integrated in the chip

Contacts: breton@lal.in2p3.fr, eric.delagnes@cea.fr, jmaalmi@lal.in2p3.fr

Réseau Semi-Conducteurs IN2P3 – June 2019 – CPPM, Marseille