## The TIMESPOT project A System Approach to 4D tracking

#### **Adriano Lai**

INFN – Sezione di Cagliari – Italy

Istituto Nazionale di Fisica Nucleare

- 1. Why 4D? Why timing?

- 2. Aim and Structure of the project: organization in Work Packages

- 3. Why 3D sensors?

- 4. 2018 activity and first results

a. Progress on sensor developments

b. Progress on front-end electronics

- c. Progress on algorithms for real-time tracking

- 4. Perspective

- 5. Conclusion

# The problem of tracking at HI-LUMI colliders and posed requirements

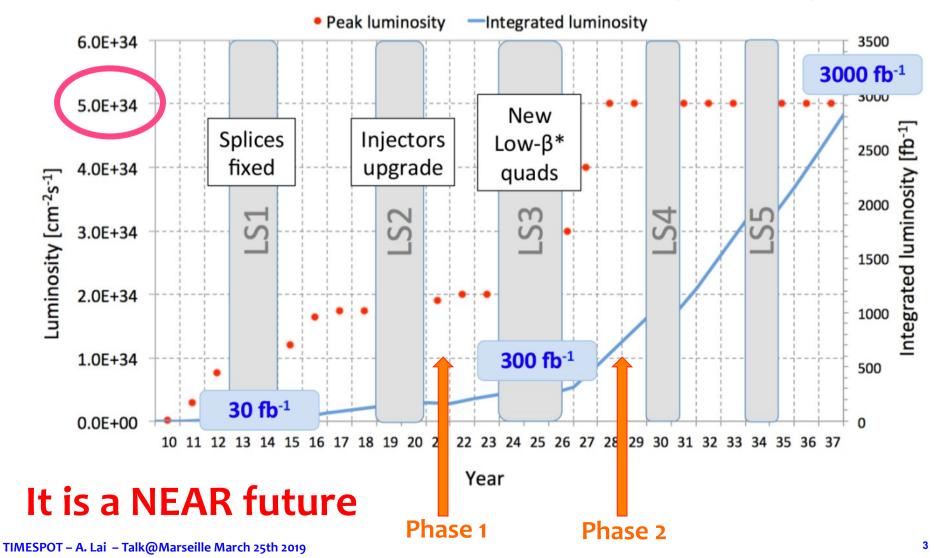

#### LHC upgrade program

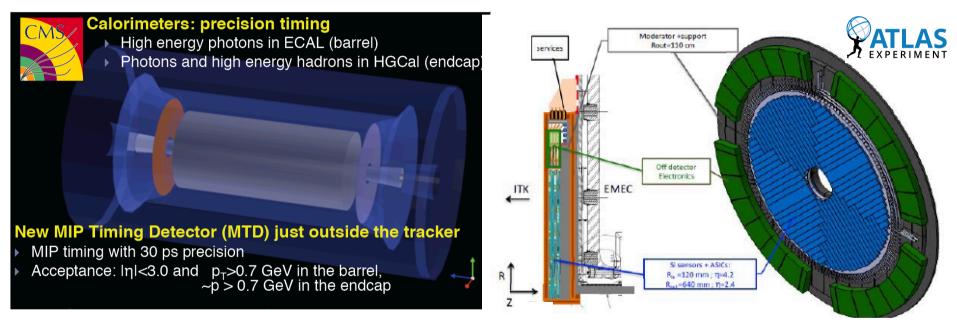

## CMS and ATLAS Phase2: Timing Layers.

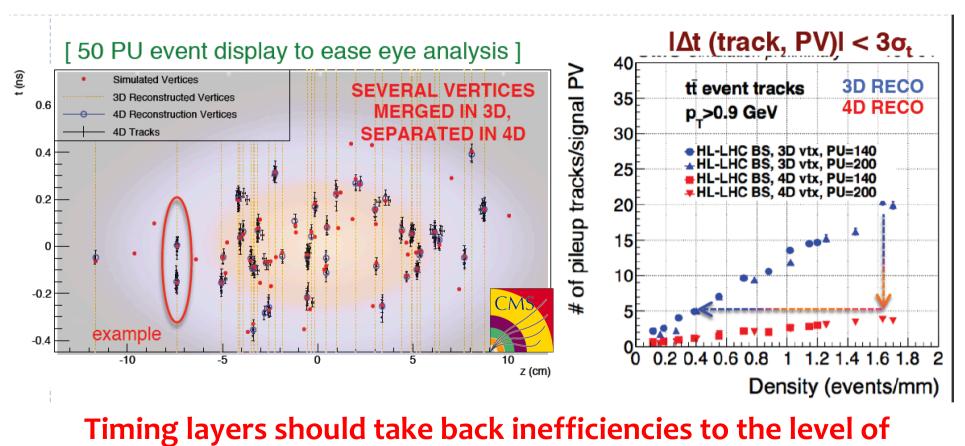

Both experiments are aiming at an upgrade in Inner Tracking systems, but high pile-up (O(100)) merges vertices even after upgrades, causing important inefficiencies in Primary Vertex (PV) identification (around 15%)

- Coarser space resolution w.r.t. trackers (power and number of channels saving)

- Use measurement of track path length and momentum to determine time-at-vertex for the track

- Pick timing layer hits by means of tracking, integrating timing layer hits into 3D Kalman

- Filter

- Back propagate smoothly to tracker, using a higher-dimensions KF with timing information

→ Timing used at trigger and/or analysis level

## CMS and ATLAS Phase2: Timing Layers.

Both experiments are aiming at an upgrade in Inner Tracking systems , but high pile-up (O(100)) merges vertices even after upgrades, causing important inefficiencies in Primary Vertex (PV) identification (around 15%)

Phase1 (1-2%)

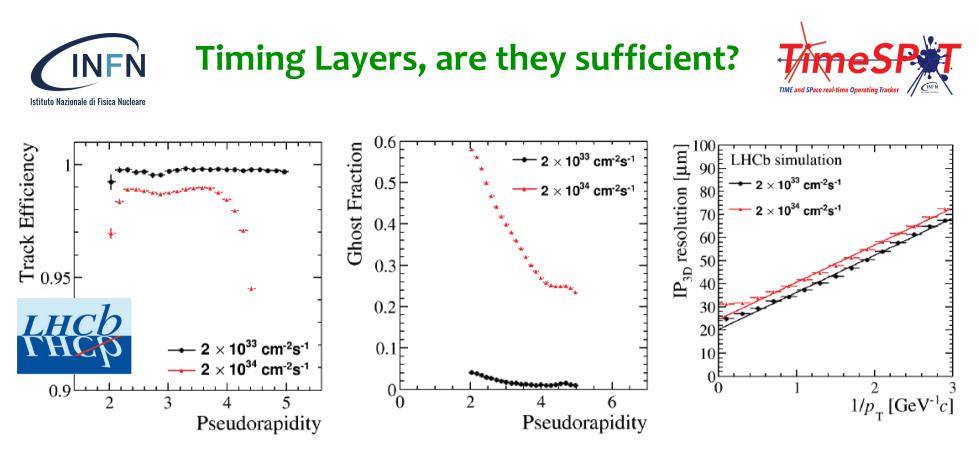

The LHCb experiment has a slightly different time-scale for the upgrade. It will reach 2 x 10<sup>34</sup> in luminosity after LS4 (year 2030)

Studies on physics perormance using a non-upgraded detector show a dramatic drop in performance, which can be (only partially) recuperated increasing (x4) the granularity of the vertex detector (or adding time information to pixels)

Moreover, LHCb requirements in radiation hardness, are ≈ x10 those of ATLAS/CMS Phase2

#### Timing Layers, are they sufficient?

To keep the PV reconstruction performance at the due level about 6 ps time resolution per track must be kept

Correspondingly, at least 200 ps per pixel are required: timing INSIDE the tracker

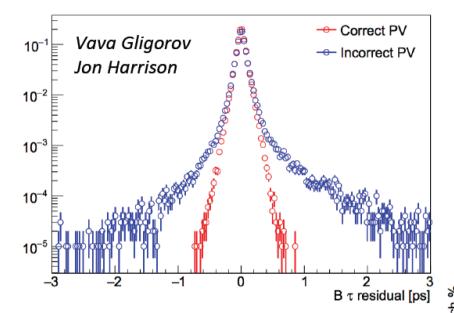

An important channel of activity in the LHCb physics program requires an accurate measurement of lifetime in B and C meson decays

Incorrect PV identification dramatically spoils the lifetime measurement

## **Beyond LHC Hi-Lumi?**

|                                | LHC ALICE<br>ITS | CLIC               | HL LHC<br>Outer pixel | HL LHC<br>Inner pixel | FCC pp                              |

|--------------------------------|------------------|--------------------|-----------------------|-----------------------|-------------------------------------|

| NIEL<br>(n <sub>eq</sub> /cm²) | 10 <sup>13</sup> | < 10 <sup>12</sup> | 10 <sup>15</sup>      | 10 <sup>16</sup>      | 10 <sup>15</sup> - 10 <sup>17</sup> |

| TID                            | < 3 Mrad         | < 1 Mrad           | 80 Mrad               | 1 Grad                | 40 Grad                             |

| Hit rate<br>(MHz/cm2)          | 10               | < 0.3              | 100-200               | 2000                  | 200-20000                           |

General specifications for a vertex detector of the next generation (Hi-Lumi and beyond)

- Space resolution:  $\approx$  10 µm (pixel pitch  $\approx$  50 µm)

- Radiation hardness: 10<sup>16</sup> to 10<sup>17</sup> 1 MeV n<sub>eq</sub>/ cm<sup>2</sup> (sensors) and > 1 Grad (electronics)

- Time resolution: 100 ps per pixel or better (< 10 ps per vertex)

- Data rates of the order of n x Tb/s to be handled (real-time?)

## **TIME & SPace real-time Operating Tracker**

## Structure, organization and objectives of the project

#### Main target:

Develop and realize a demonstrator consisting of a complete and simplified tracking system, integrating about 100-1000 read-out channels (pixels), satisfying the following characteristics:

- Space resolution: O (10 µm)

- Radiation hardness: > 10<sup>16</sup> 1 MeV n<sub>eq</sub>/ cm<sup>2</sup> (sensors) and > 1 Grad (electronics)

- Time resolution: < 100 ps per pixel (target  $\approx$  30 ps )

- Real time track reconstruction algorithms and fast read-out (data throughput > 1 TB/s)

#### Activities are organized in 6 work packages:

P.I. : A. Lai, Cagliari

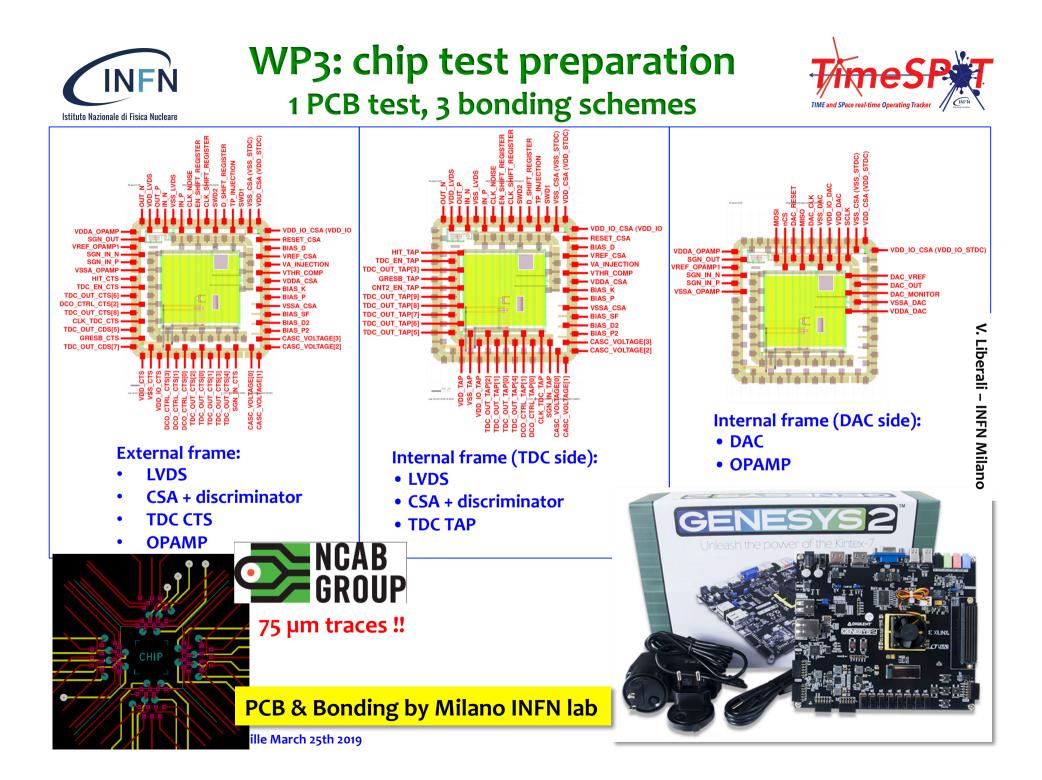

- 3D silicon sensors: development and characterization (GF. Dalla Betta Trento) 3D diamond sensors: development and characterization (S. Sciortino Perugia) Design and test of pixel front-end (V. Liberali Milano)

- 4. Design and implementation of real-time tracking algorithms (N. Neri Milano)

- 5. Design and implementation of high speed readout boards (A. Gabrielli Bologna)

- 6. System integration and tests (A. Cardini Cagliari)

Sezioni INFN: Bologna, Cagliari, Genova, Ferrara, Firenze, Milano (+Bergamo), Padova, Perugia, Torino, TIFPA.

≈ 60 heads, ~ 20 FTE. People from LHCb, ATLAS, CMS + others

- 1. Why 4D? Why timing?

- 2. Aim and Structure of the project: organization in Work Packages

- 3. Why 3D sensors ?

- 4. 2018 activity and first results

a. Progress on sensor developments

b. Progress on front-end electronics

c. Progress on algorithms for real-time tracking

- 4. Perspective

- 5. Conclusion

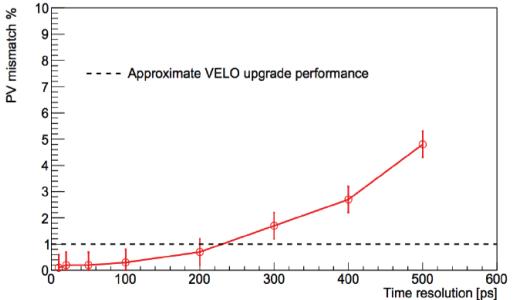

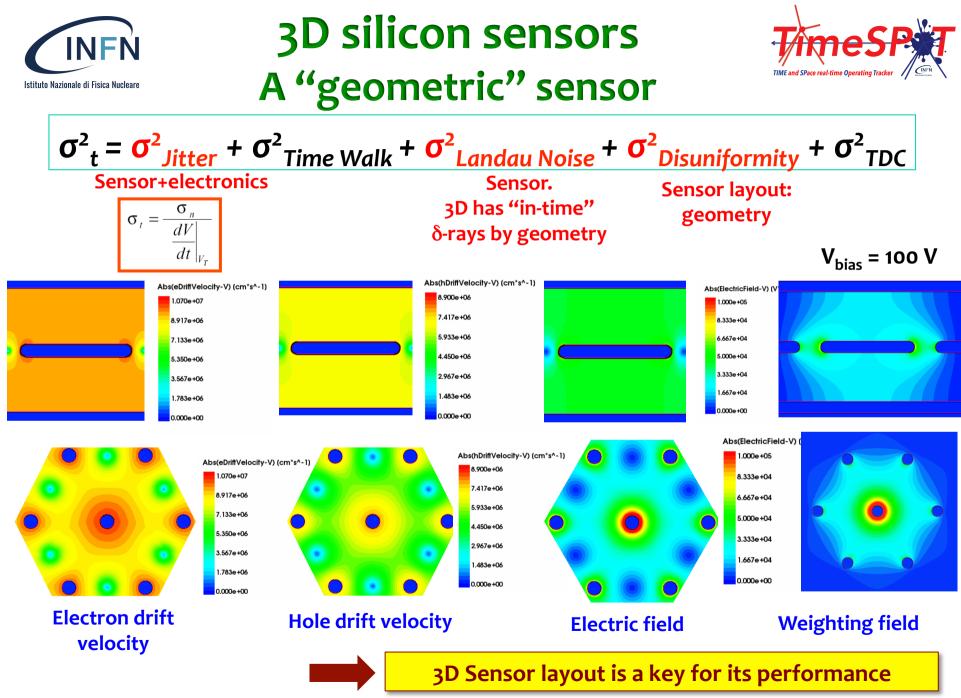

## **3D silicon sensors**

#### PROS

- Un-matched radiation hardness<sup>(1)</sup>

- Already used technology<sup>(2)</sup> for vertex detectors

- Strong mitigation of Landau fluctuation by geometry

- ➤ Extremely fast signal: optimal potentiality for timing<sup>(3)</sup> (not yet exploited!) → <u>optimization by design</u>

#### CONS

- Fabrication complexity and cost (w.r.t planar standard technology)

- ➤ Geometric inefficiency (~blind electrodes) → tilt<sup>(2)</sup> or stagger

- (1) J. Lange et al, Radiation hardness of small-pitch 3D pixel sensors up to a fluence of  $3\times10^{16}$  n<sub>eq</sub>/cm<sup>2</sup>, 2018 JINST 13, P09009.

- (2) C. Da Via et al., 3D Silicon Sensors: Design, large area production and quality assurance for the ATLAS IBL pixel detector upgrade. NIMA, vol 694 Dec. 2012.

- (3) S. Parker et al., Increased Speed: 3D silicon Sensors; Fast Current Amplifiers, IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 58, NO. 2, APRIL 2011.

Charge deposition distance is decoupled from electrode distance

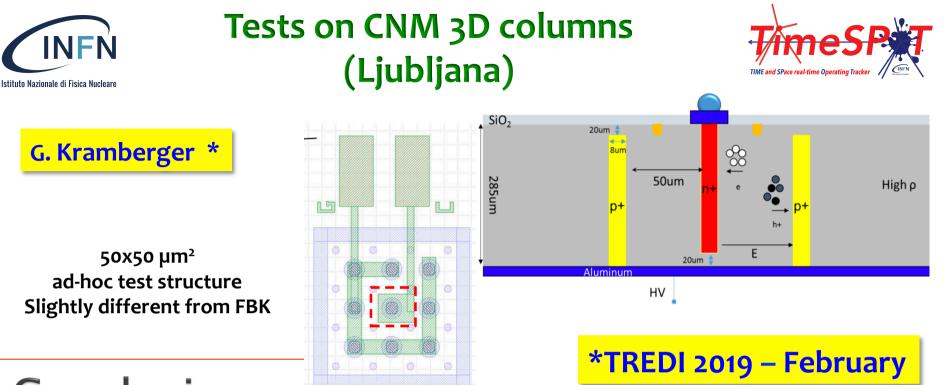

\*TREDI 2019 – end of February

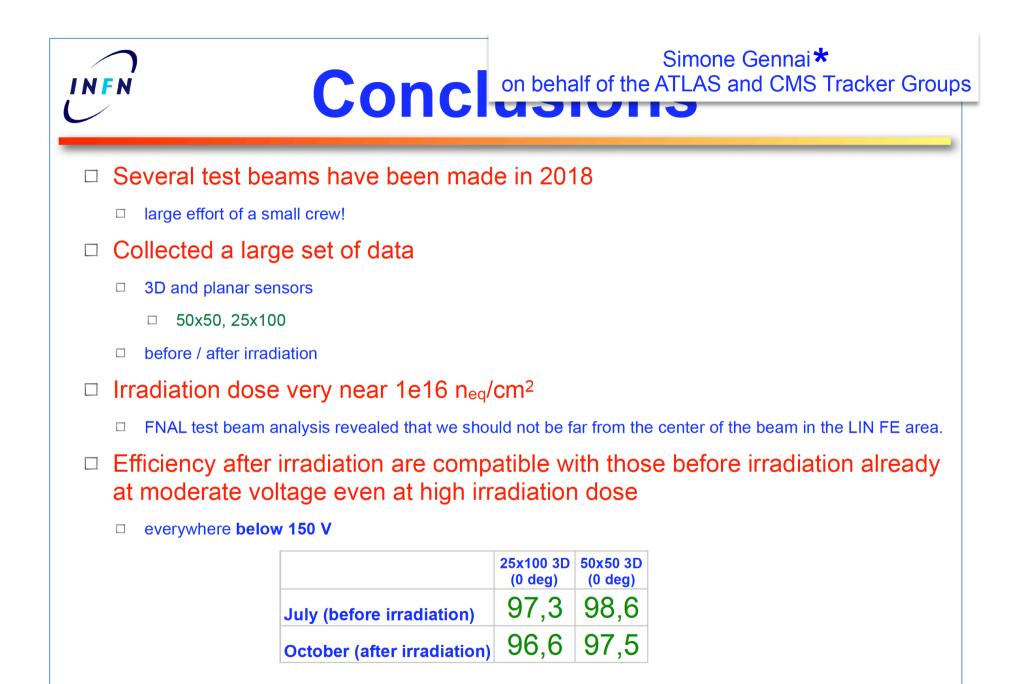

## Conclusions

- > Timing in small cell 50x50  $\mu m^2$  3D detectors was measured and simulated.

- Very good agreement between simulated and measured results was found, within 10%, which validates simulation.

- Contribution to the timing resolution due to different hit positions (disuniformity) is found to be comparable to landau fluctuations in LGAD at high gain:

- For multi-cell operation the resolution of 20 ps at -20°C temperature is predicted.

- $^\circ~$  Single cell 50x50  $~\mu m^2$  detector (1E) time resolution depends mainly on applied voltage ~30 ps at >100 V and -20°C

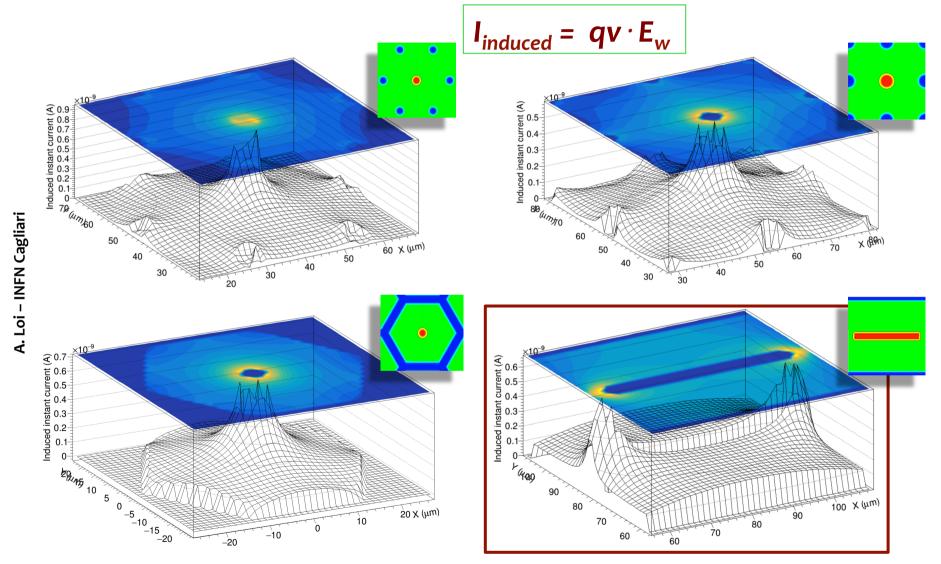

## Simulations and sensor Design 2D-based "Ramo maps"

Trench-shaped geometry

INFŃ

Istituto Nazionale di Fisica Nucleare

- 1. Why 4D? Why timing?

- 2. Aim and Structure of the project: organization in Work Packages

- 3. Why 3D sensors?

- 4. 2018 activity and first results

- a. Progress on sensor developments

- **b.** Progress on front-end electronics

- c. Progress on algorithms for real-time tracking

- 4. Perspective

- 5. Conclusion

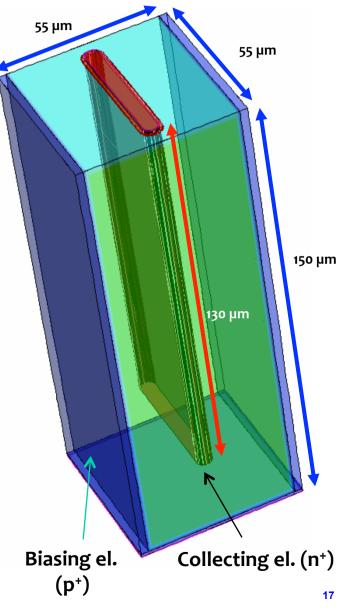

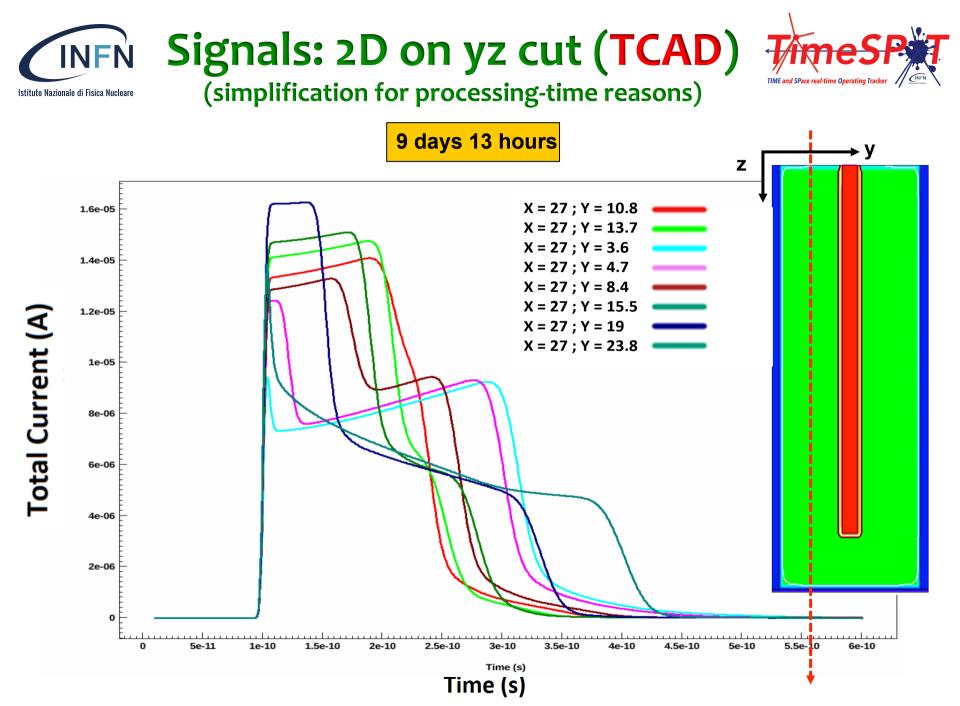

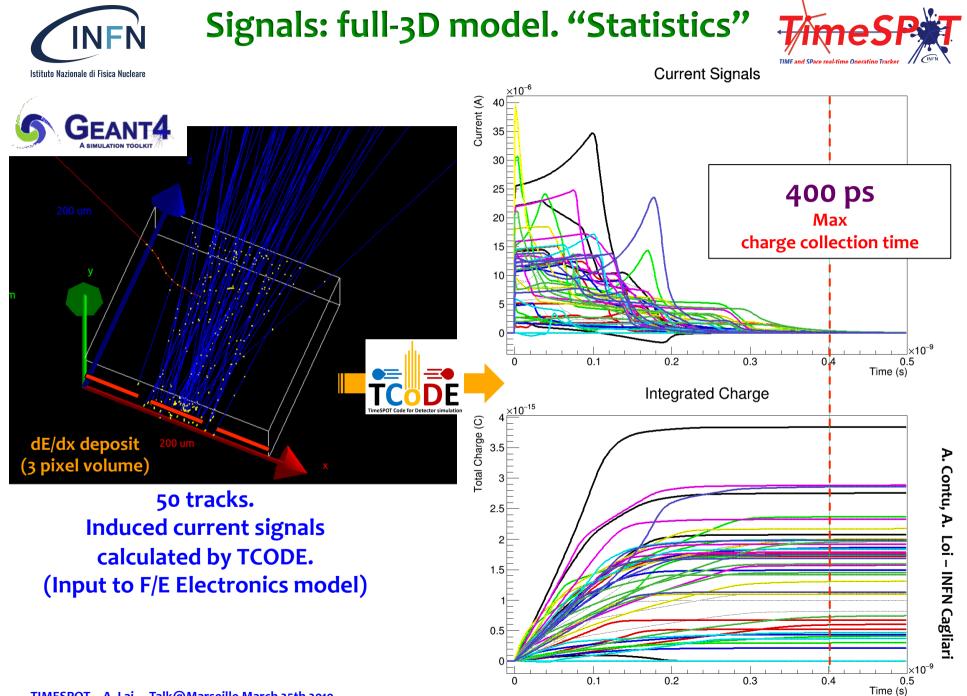

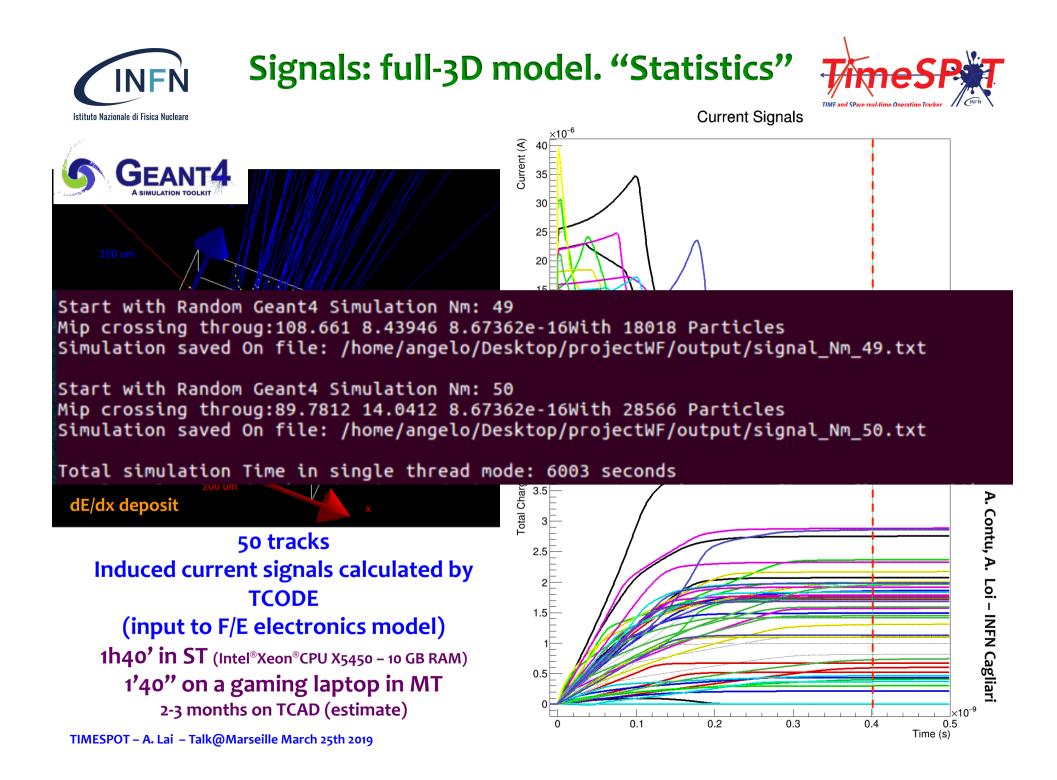

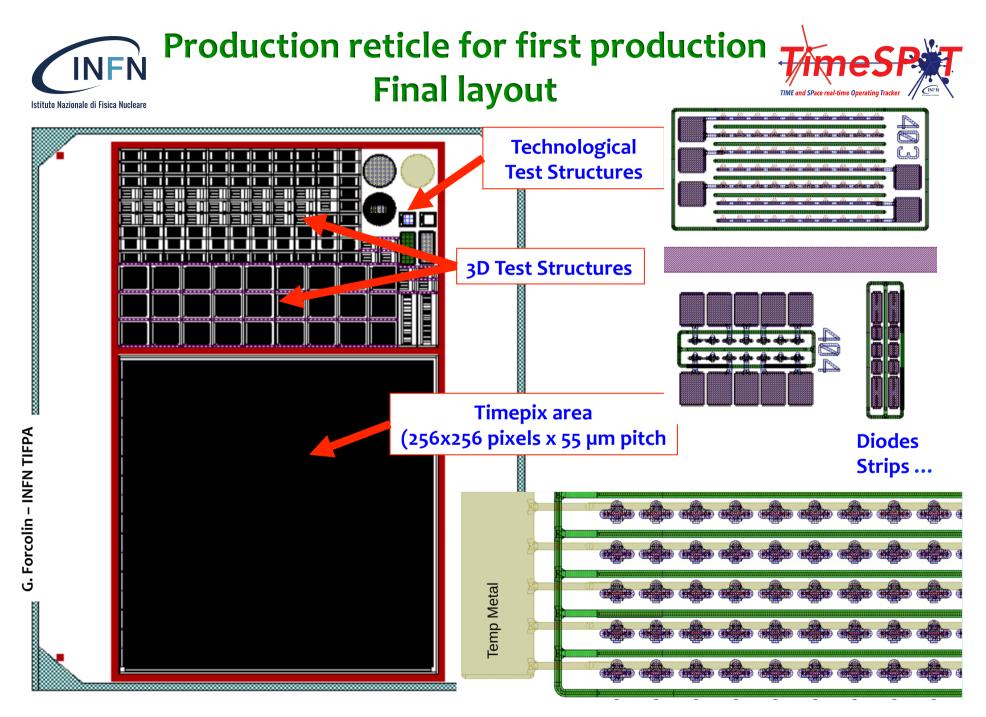

## Trench geometry and Tools for full-3D simulation

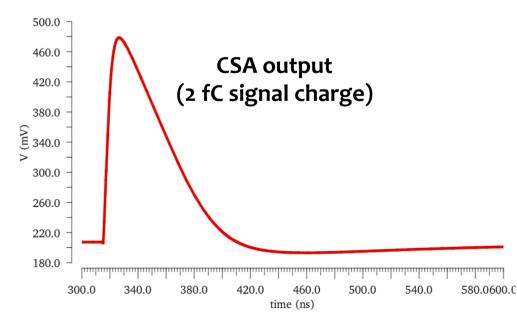

- Total charge deposit for MIP ≈ 2 fC

- Full depletion @ less than 100 V

- 55x55 µm<sup>2</sup>: TIMEPIX family-compatible pitch

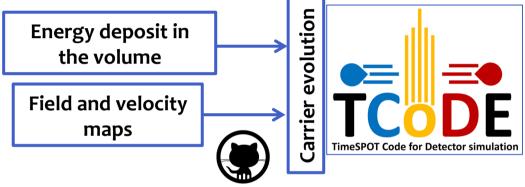

https://github.com/MultithreadCorner/Tcode

Induced current signal simulation:

- 1. dE/dx detailed physics for MIP (Geant4)

- 2. Detailed E field and mobility maps (e.g. TCAD)

- 3. Induced signal evolution (carrier transport):

- Sentaurus TCAD: <u>> 30 h</u>\* for 1 signal and no secondary particles on a 24-cores machine.

- (Custom) TCODe: < 1 min for full simulation.</p>

\*with very accurate and clever meshing

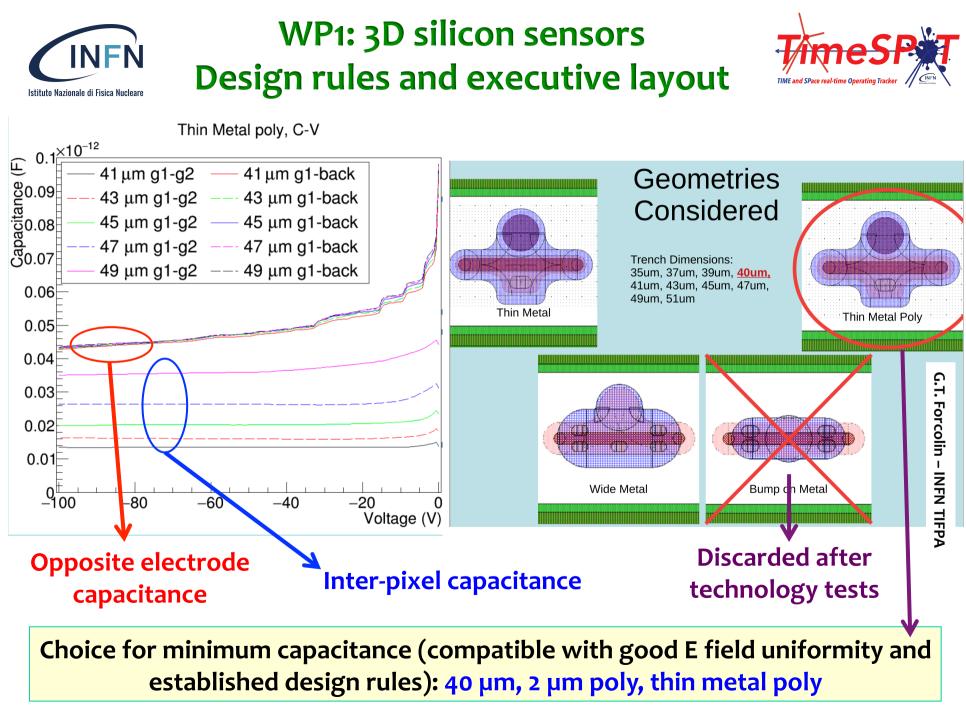

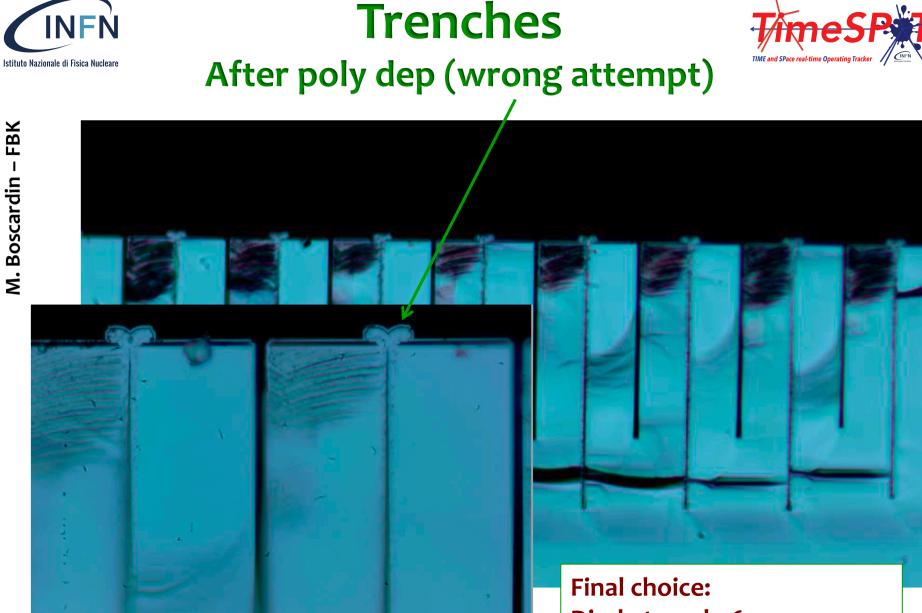

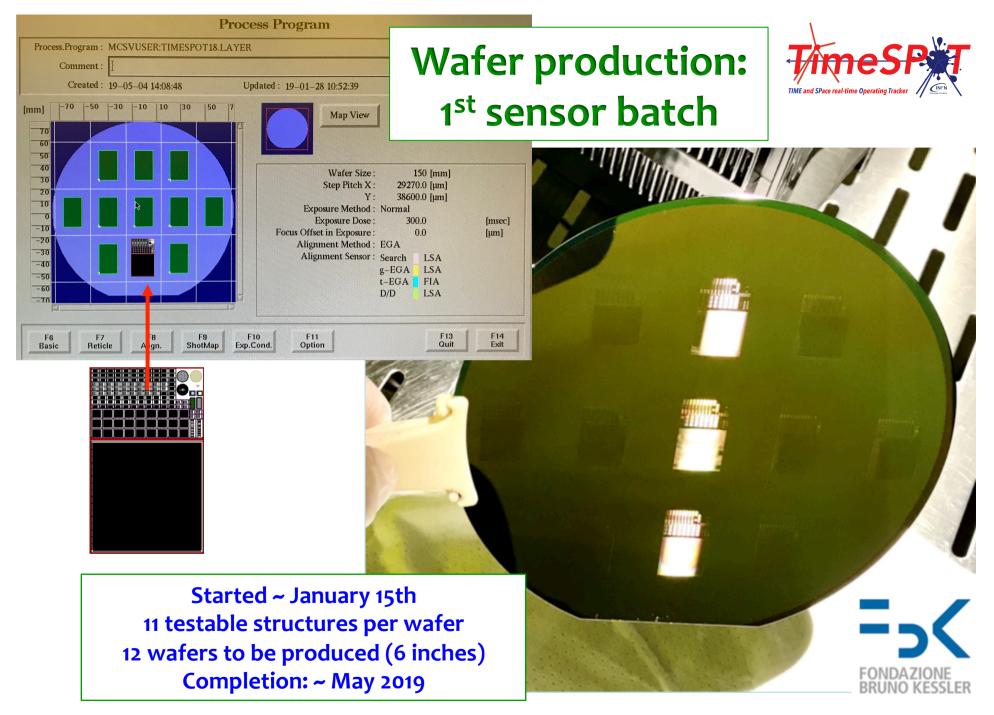

## 3D silicon sensors

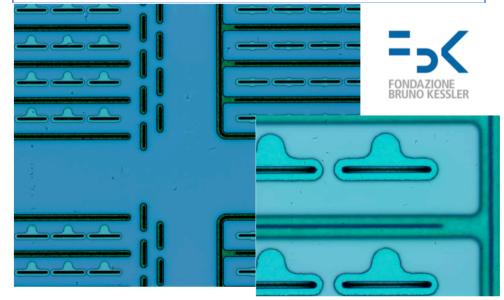

#### **Fabrication: Technology tests at FBK**

# **3D trenched geometry is a new technology !!!**Some attempts on hexagonal trenches ad CNM (2013)\*: ≈ Working, but very high leakagecurrent→ Tests @ FBK from July to December 2018.

#### "Simulation" of litho process

- 1. Oxidation

- 2. Definition and attack of ohmic trenches (Deep Reactive Ion Etching)

- 3. Deposition of poly-Si on ohmic trenches

- 4. Definition of poly-Si on ohmic trenches

- 5. Definition and attack of junction trenches (DRIE)

- 6. Deposition of poly-Si on junction trenches

- 7. Definition of poly-Si on junction trenches

- 8. TEOS deposition

- 9. Opening of contacts

- 10. Metal deposition and definition

\*A. Montalbano et al., NIMA 765 (2014), 23

#### Results

#### Litho trenches:

750 nm Oxide + 6 μm Vacuum bake Resist + DRIE: → yield 100%

**Optimized recipe:**

for DRIE: 160 μm (ohmic) and 135 μm (junction) for poly: 3000 nm

Diode trench: 6 µm x 135 µm Bias trench: 6 µm x 160 µm

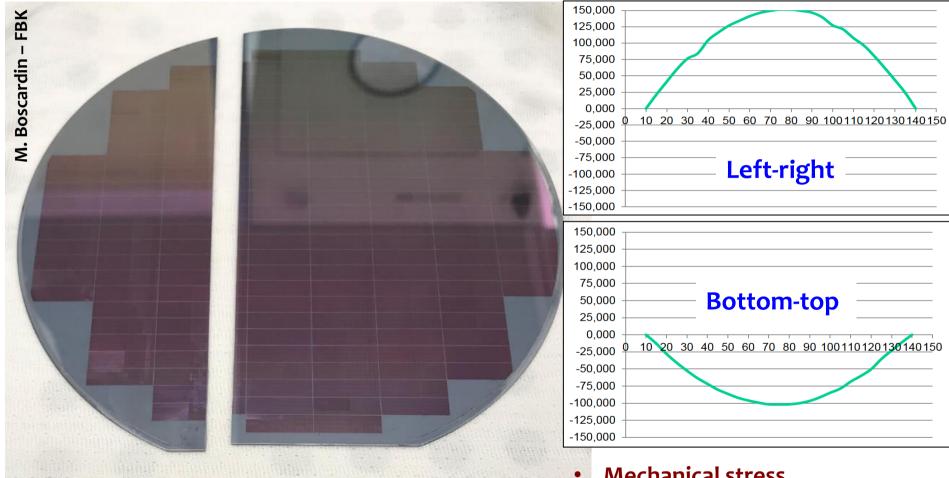

## 1<sup>st</sup> wafer prototypes and fabrication issues

#### Low mechanical yield Wafers tend to break !!

- Mechanical stress.

- Wafer bowing

- Frequent breaking after attack and filling of ohmic trenches

M. Boscardin – FBK

- Improved version (sparser modules)

- Not very suitable for mass production

| 150,000 —  |                                               |

|------------|-----------------------------------------------|

| 125,000 -  |                                               |

| 100,000 -  | Left-right                                    |

| 75,000 —   |                                               |

| 50,000 —   |                                               |

| 25,000 —   |                                               |

| 0,000 🕂    |                                               |

| -25,000 🗍  | 10 20 30 40 50 60 70 80 90 100110120130140150 |

| -50,000 —  |                                               |

| -75,000 —  |                                               |

| -100,000 — |                                               |

| -125,000 + |                                               |

| -150,000 ⊥ |                                               |

|            |                                               |

#### New strategy for wafer layout

Wafer bowing

highly mitigated

After fabrication of test structures, the 1<sup>st</sup> batch run (12 wafers) has started mid of January

| 150,000 $_{ot}$  |                                               |

|------------------|-----------------------------------------------|

| 125,000 +        | <b>D</b> = 11 = 1 = 1                         |

| 100,000 +        | Bottom-top                                    |

| 75,000 +         |                                               |

| 50,000 +         |                                               |

| 25,000 +         |                                               |

| 0,000 🕂          |                                               |

| -25,000 💾        | 10 20 30 40 50 60 70 80 90 100110120130140150 |

| -50,000 +        |                                               |

| -75,000 +        |                                               |

| -100,000 +       |                                               |

| -125,000 +       |                                               |

| -150,000 $\perp$ |                                               |

|                  |                                               |

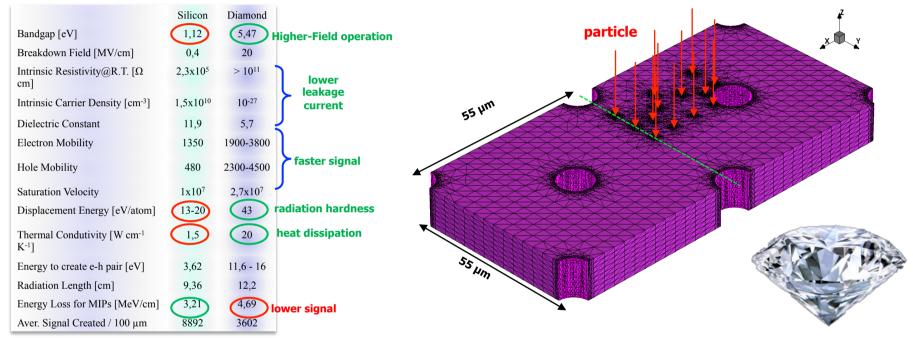

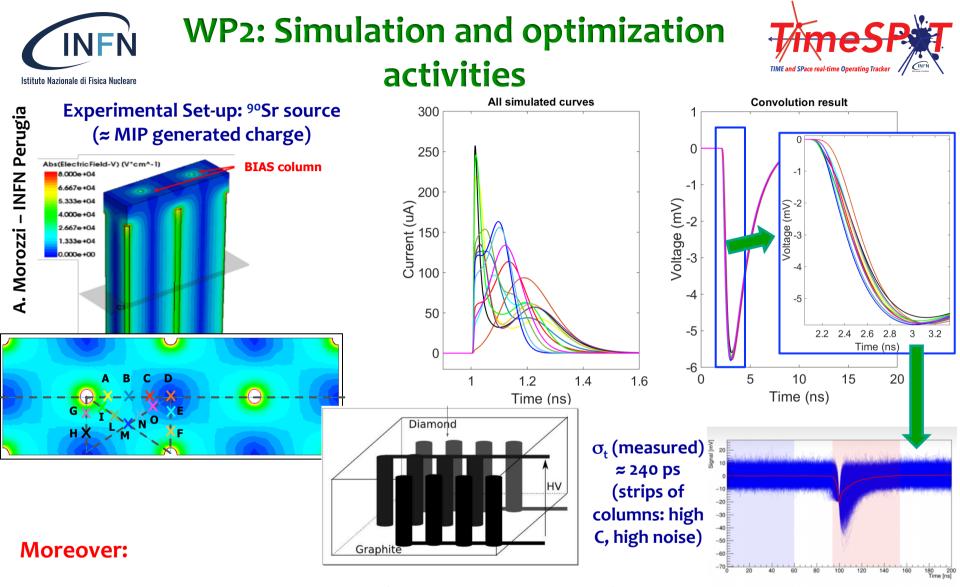

#### Firenze, Perugia

#### Silicon vs Diamond in radiation detection

Already realized with success for dosimetric applications (3Dose – CSN5)

- Very promising characteristics for timing

- Lower signal can be partially compensated by larger thickness

- S/N ratio still favourable

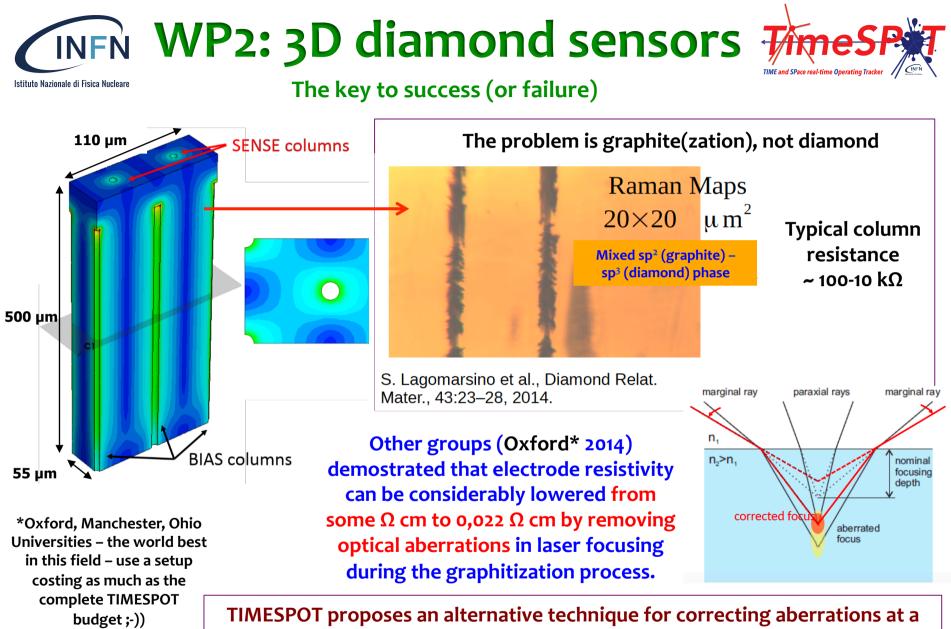

- 3D structure decreases collection time and capture probability by defects

TIMESPOT plan: Realize a silicon-geometry-compatible device and read-out it with the same pixel electronics, changing only the very first stage (programmable impedance and gain)

- Optimization of column distribution (field uniformity and CCE)

- Optimization of column aspect ratio (R vs C trade-off)

- Optimization of sensor geometry (idea to realize trenches: post-poned to results on columns)

- Many inputs from Perugia to 3D Silicon modelization activities

TIMESPOT – A. Lai – Talk@Marseille March 25th 2019

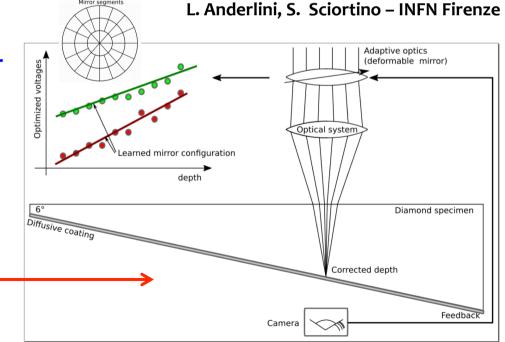

#### L. Anderlini – INFN Firenze

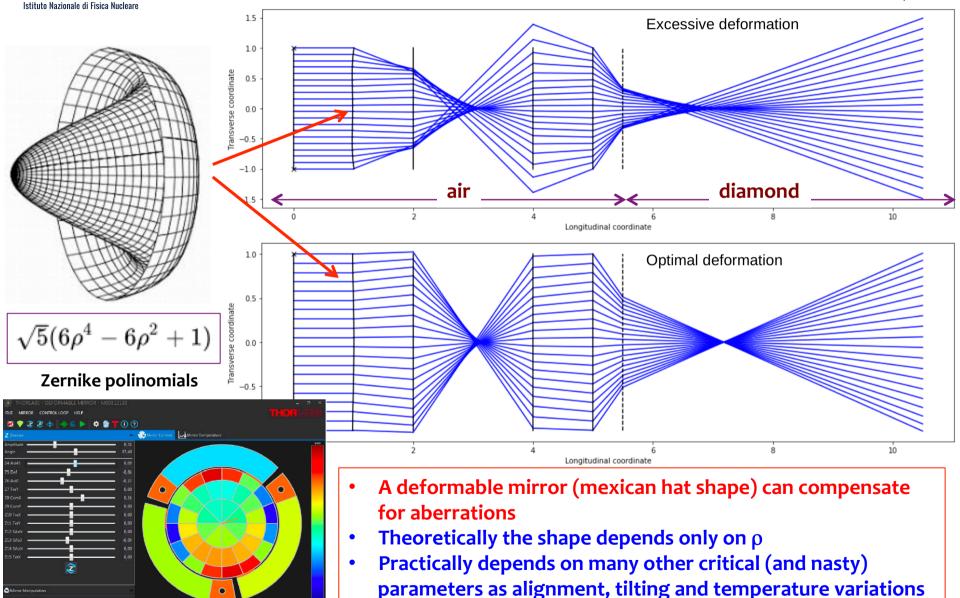

much lower cost than the real-time adapitive wave-front control

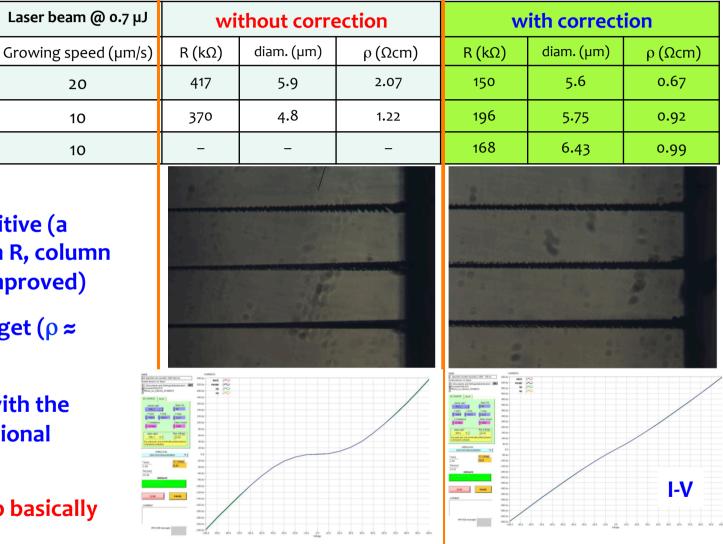

TIMESPOT starting point (April 2018): R = 53 k $\Omega$ ,  $\rho$  = 2.35  $\Omega$ cm

## WP2: Spherical aberration

TIMESPOT – A. Lai – Talk@Marseille March 25th 2019

INFŃ

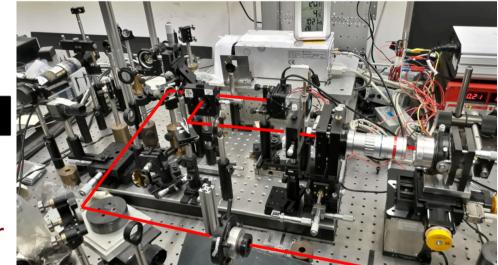

## WP2: Graphitization setup

New system (Nov 18) Deformable mirror  $f_1$   $f_2$   $f_1$   $f_1$   $f_2$   $f_1$   $f_1$   $f_1$   $f_2$   $f_1$   $f_1$   $f_2$   $f_3$   $f_1$   $f_1$   $f_2$   $f_3$   $f_1$   $f_1$   $f_1$   $f_2$   $f_3$   $f_1$   $f_1$   $f_2$   $f_3$   $f_1$   $f_1$   $f_1$   $f_2$   $f_3$   $f_1$   $f_1$   $f_2$   $f_3$   $f_3$   $f_1$   $f_1$   $f_2$   $f_3$   $f_3$  $f_$

INFŃ

Istituto Nazionale di Fisica Nucleare

50× objective, large NA (0.67), 4f system, PI linear stages, He-Ne laser pointer

- stabilization in temperature of the deformable mirror

- optimization of the deformable mirror configuration

- timing measurement setup (new boards with aperture)

- columns at different energy per pulse and focus displacement velocity

The optimal configuration of the mirror is "learned" on a diamond specimen of variable depth

## INFN WP2: Results on column R

Istituto Nazionale di Fisica Nucleare

L. Anderlini, S. Sciortino INFN Firenze

Results are very positive (a factor ~2 is gained in R, column quality has visibly improved)

Still far from the target (ρ ≈ 0.05 Ωcm)

Some gain margin with the present setup (additional factor 2-5?)

Is our low-cost setup basically inadequate?

- 1. Why 4D? Why timing?

- 2. Aim and Structure of the project: organization in Work Packages

- 3. Why 3D sensors?

- 4. 2018 activity and first results

a. Progress on sensor developments

b. Progress on front-end electronics

c. Progress on algorithms for real-time tracking

- 4. Perspective

- 5. Conclusion

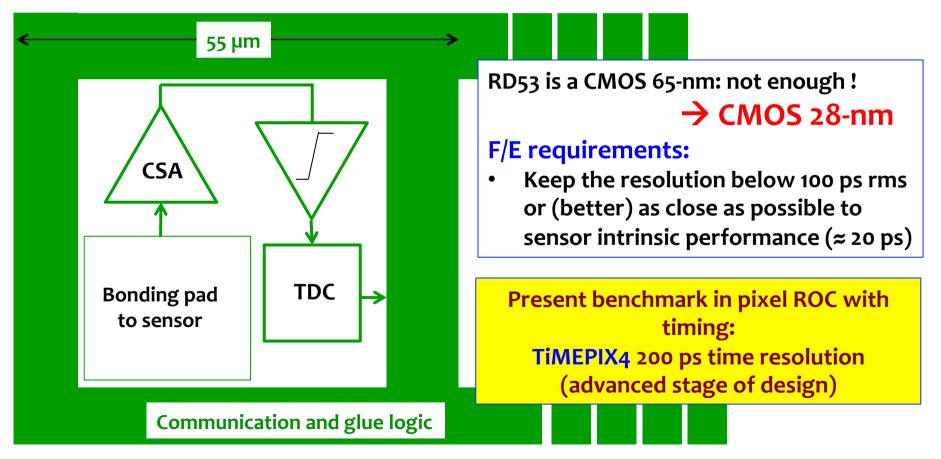

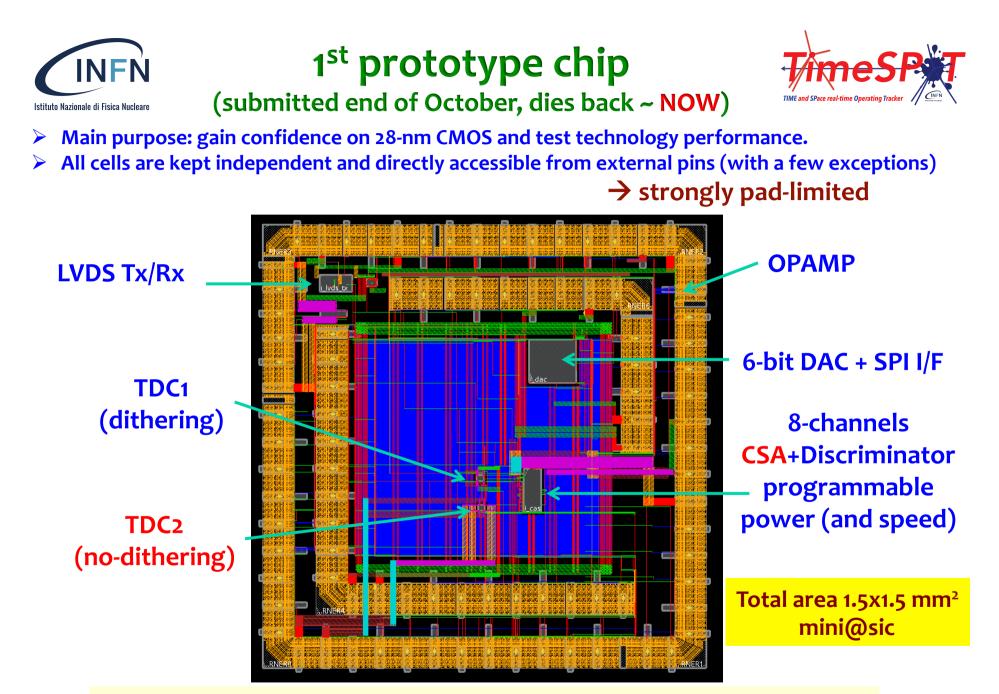

# **FILTURE ALLIGERE** Pixel read-out electronics

- Pixel ROC for 4D tracking require a binary readout (with high resolution in time) and one TDC per pixel (or group of pixels)

- The first approach is to rescale a classic circuit (CMS RD53 style) to our purposes, adding a TDC per pixel

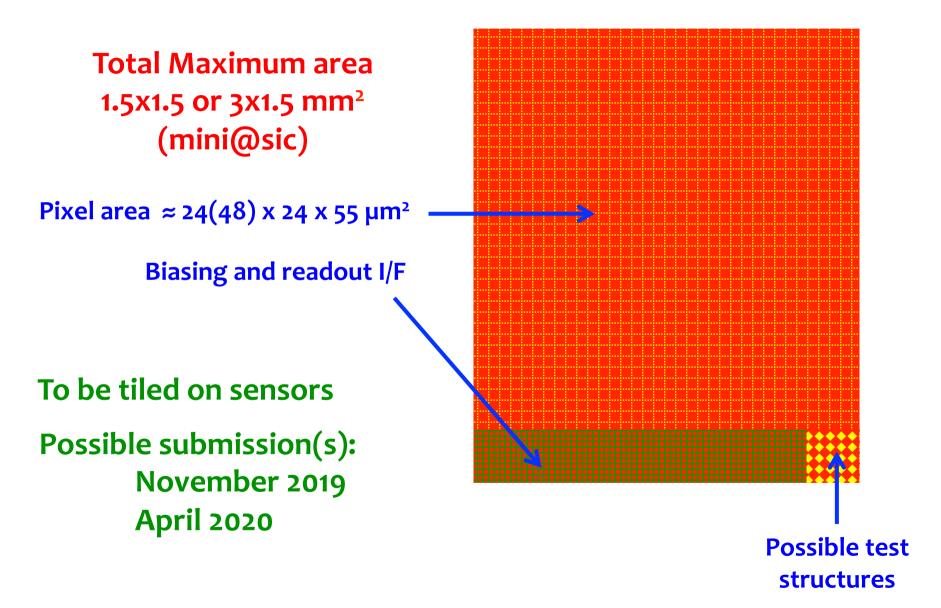

In the next version/submission a  $\approx$  20x20 matrix of pixel ROC is possible

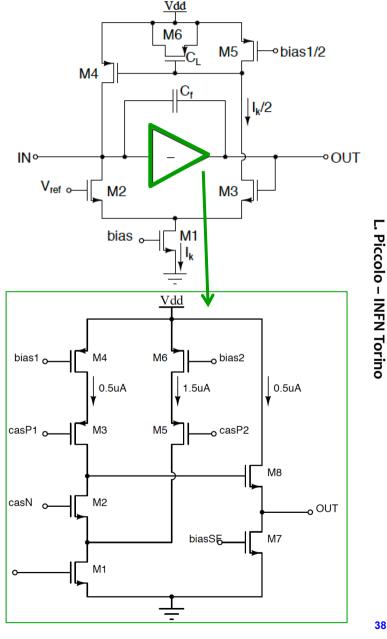

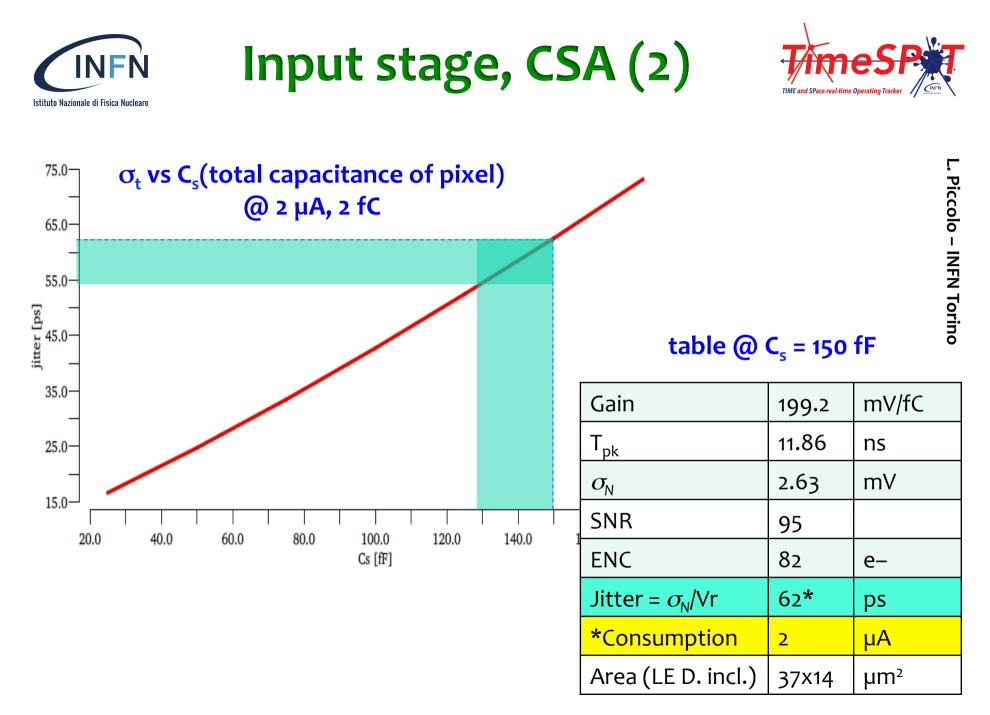

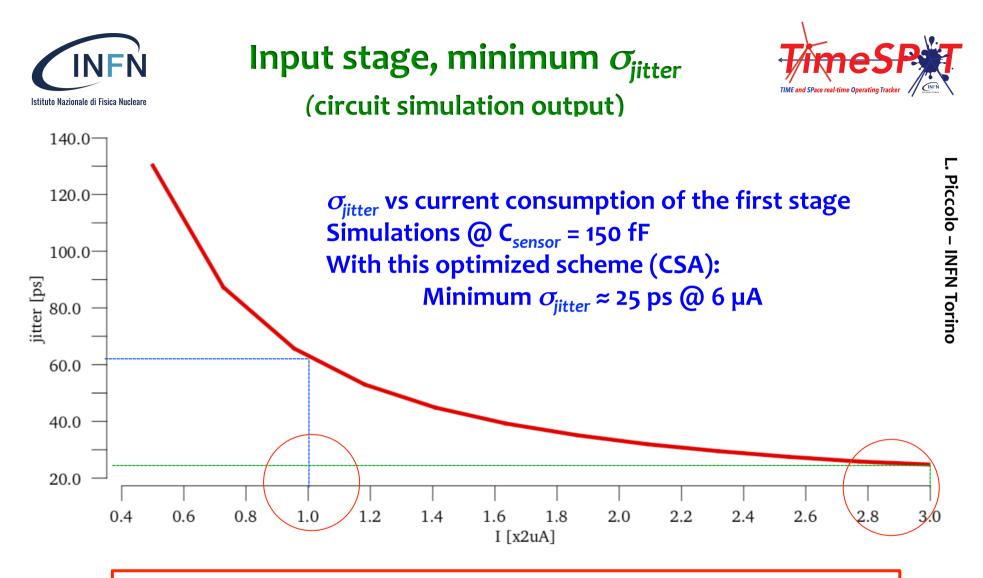

# Input stage, CSA (1)

- Output voltage proportional to input charge

- Constant peaking and falling times for better timing (no CR-RC<sup>n</sup> shaping)

- Low noise •

- Krummenacher (active) filter: DC current • compensation of input leakage current (critical?)

- **Programmable input MOST current (this prototype)** •

- Cascodes can be switched on/off to improve S/N ratio (this prototype)

38

In view of the submission of the next version, we are already studying other readout schemes than the CSA (transimpedance or non linear input stages)

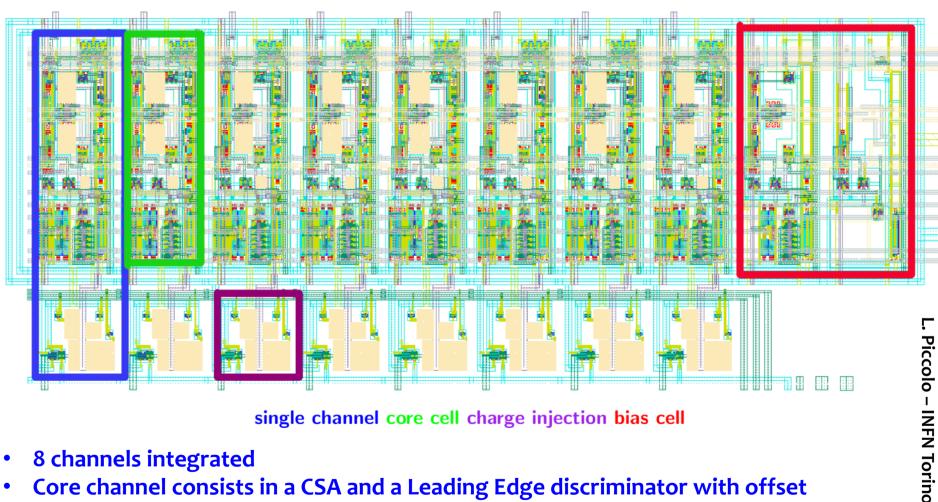

single channel core cell charge injection bias cell

- 8 channels integrated

- Core channel consists in a CSA and a Leading Edge discriminator with offset ٠ compensation

- Whole cell sizes  $60\mu m \times 150\mu m$  (core cell area = 14 x 37  $\mu m^2$  without special care on area ٠ optimization)

### **High-resolution TDC**

91 Out reg 20 out reg 51

- The (two) TDC designs are based on a "ALL digital fully-synthesizable design"\*

- The DCO is standard-cell based

- DCO is enabled only on the occurrence of a hit for lower noise and consumption

| A Baseline ▼= 0 Cursor-Baseline ▼= 298ns                                                                                                       |            | TimeA = 298ns                                                     | adeddu- I<br>the solute 155 4714 594 1 576 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                  |                |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------|----------------|

| Name<br>GResB<br>GResB<br>K<br>K<br>K<br>Sgn_in<br>K<br>K<br>K<br>C<br>C<br>C<br>K<br>K<br>K<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C | Cursor     | 280ns     290ns     300ns     310ns     320ns     330ns     340ns |                                                                                  | 2 15<br>2 2 15<br>2 2 1 1 mpl0 4 | INFN Cagliari  |

|                                                                                                                                                | 1          |                                                                   | Master Clk                                                                       | 40                               | MHz <b>Ξ</b> . |

| <b>ICI</b> P                                                                                                                                   | 0.00226▶ 👬 |                                                                   | Resolution (LSB)                                                                 | 50                               | ps             |

|                                                                                                                                                | 0 mW7 💥    |                                                                   | Resolution(rms)                                                                  | 15                               | ps             |

|                                                                                                                                                |            |                                                                   | NOB                                                                              | 10                               | bits           |

|                                                                                                                                                | 0 mW7 💥    |                                                                   | Area                                                                             | 20X15                            | μm²            |

|                                                                                                                                                | 0.00226 🖓  | -0.002                                                            | Power (conversion)                                                               | 1.9                              | mW             |

|                                                                                                                                                |            |                                                                   | Power (stand-by)                                                                 | 11                               | μW             |

\*S. Cadeddu et al., High Resolution Synthesizable Digitally Controlled Delay Lines, IEEE TNS vol 62 No. 6, Dec 2015

Ś

## Concept for a 2<sup>nd</sup> prototype

- 1. Why 4D? Why timing?

- 2. Aim and Structure of the project: organization in Work Packages

- 3. Why 3D sensors?

- 4. 2018 activity and first results

- a. Progress on sensor developments

- **b.** Progress on front-end electronics

- c. Progress on algorithms for real-time tracking

- 4. Perspective

- 5. Conclusion

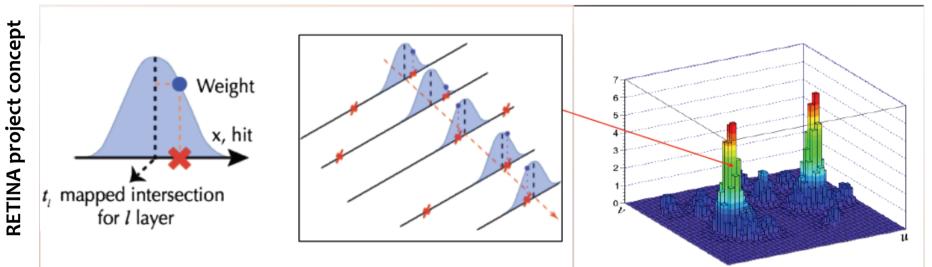

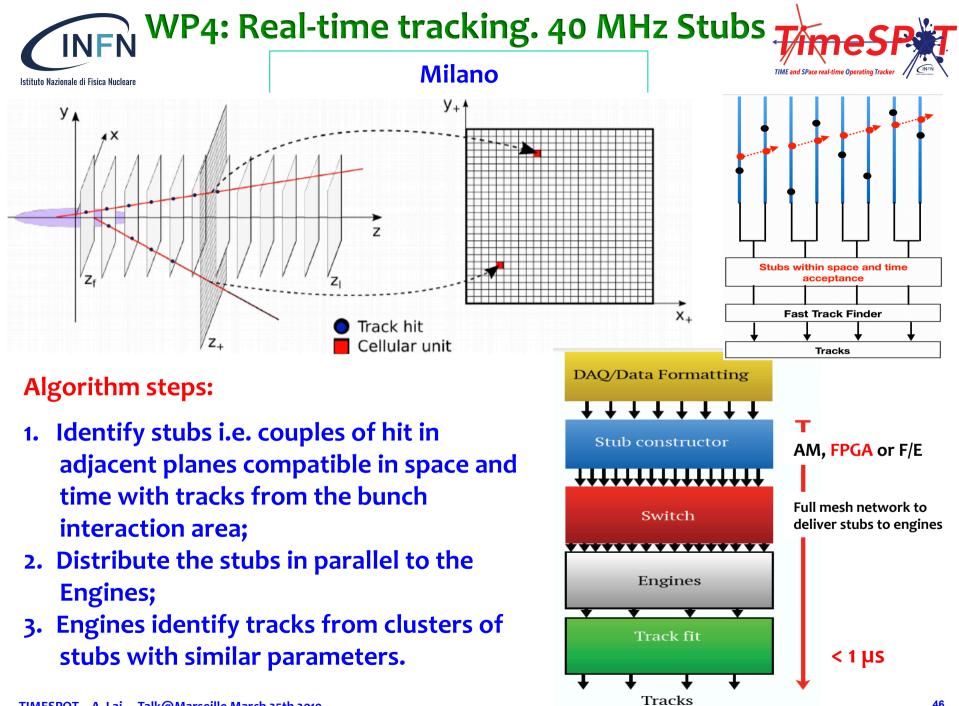

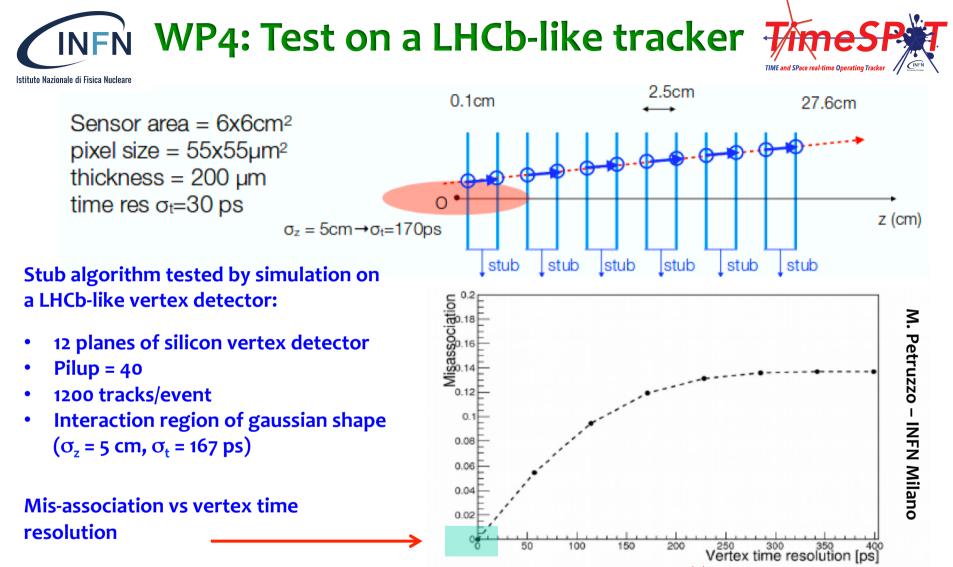

# Our strategy is to follow the RETINA project approach (1), adding time information into the algorithm structure (2)

**RETINA concept:** The detector geometry defines a set of possible tracks. A possible track corresponds to a cellular unit. Any point "seen" by the detector can be associated a weight, according to its distance from the track hypothesis. The algorithm finds tracks as maxima in weight in the track space.

TIMESPOT concept: track points are substituted by stubs.

Each cellular unit can be processed in parallel. The algorithm can also be executed on commercial (powerful) FPGA.

<sup>(1)</sup> A. Abba et al., Simulation and performance of an artificial retina for 40 MHz real time track reconstr., JINST 10 (2015) no 03, C03008 (2) Neri N. et al., 4D fast tracking for experiments at high luminosity LHC, JINST 11 (2016) no. 11, C11040

The 4D fast tracking algorithm has also been in FPGA on a custom board (1): Two Xilinx Virtex Ultrascale FPGAs High-speed optical transceivers → up to 1 Tbps input data rate per FPGA One Xilinx Zynq FPGA

(1) M. Petruzzo et al., A novel 4D finding system using precise space and time information of the hit , TWEPP 2018

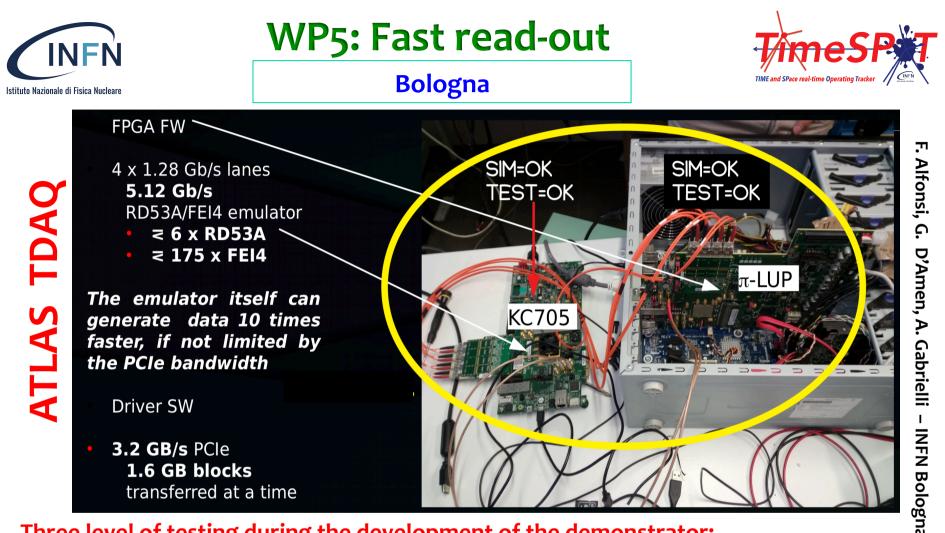

Three level of testing during the development of the demonstrator:

- Develop minimal read-out chains (from TDAQ architecture) for Low-performance testing 1.  $\rightarrow$  in preparation procedures (simple, low cost FPGA systems)

- 2. Use the ATLAS TDAQ emulator for RD53 to generate events with a realistic data format to test real-time algorithms  $\rightarrow$  on going with Milano

- Use the ATLAS TDAQ as a test-bench for the TIMESPOT prototypes 3.

$\rightarrow$  this year

## WP6: Test preparation in labs and test-beams

Cagliari, Genova, Padova (LNL), Trento...

Preparation of wafer tests in the labs (short term – Spring-Summer 2019):

- 1. <u>Trento</u>: first tests (automatic and manual tests) on 3D wafers

- 2. <u>Cagliari</u>: manual tests under probe station with IR laser and confocal microscope (devices already purchased, under preparation)

- 3. <u>Torino & Padova</u>: sharing of manual test under PS (setup ready)

- 4. <u>Cagliari & Genova</u>: preparation of active probe for pixel time response under laser scan

- 5. <u>Padova (LNL)</u>: use of µBeam facility for detailed pixel scan with 1.8 MeV protons (see next slide)

Preparation of device tests with MIPs under test beam (medium term – Fall-Winter 2019):

- Preparation of a time-tagger using MCP (almost completed in Cagliari, ~ 15 ps time resolution measured with cosmics).

- 2. Test-beam test of simple structure (wire bonding)

- 3. Bonding to TIMEPIX (ADVACAM?) or VELOPIX (LHCb) after temp metal removal → most sensor characteristics testable but timing

- 4. Test beam with telescope (PSI already booked October 2018)

- 5. Fermilab? DESY? (CERN is on shutdown!)

#### During 2019:

- Set-up of test-benches and tests on first prototypes (sensors and electronics)

- Test beams for complete characterization of devices

End 2019 – beginning 2020 Submission of second prototypes

During 2020: Set-up and tests of demo system

TIMESPOT is financed till the end of 2020. Clearly, three years will not be sufficient for a final answer. If TIMESPOT is "successful enough", a kind of TIMESPOT-II must be invented – hopefully at an international level

Summary

- The TIMESPOT project aims at realizing a complete demo-vertexdetector with time-resolved events and real-time reconstruction

- Results on developments concerning the activities of its first year (2018) have been illustrated

- Year 2019 will be a decisive year for TIMESPOT: results on its first prototype batches of sensor and electronics will be obtained and evaluated.

- In the meantime, we are already starting to envisage a possible extended prosecution of our project

#### THANK YOU