- 1. Principe

- 2. Statut du projet

- 3. CIC2

*L.Caponetto, G.Galbit, C.Guérin, B. Nodari, W.Tromeur, S.Viret*

*IPN Lyon*

→ Contexte:

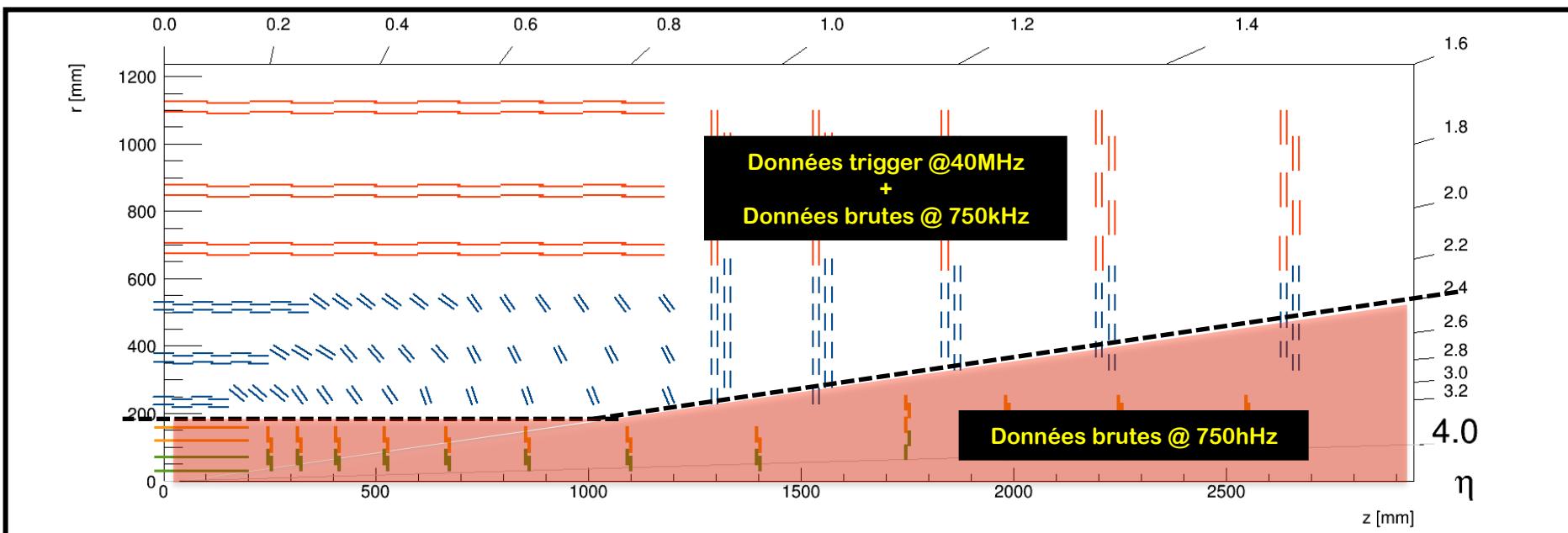

- Dans le détecteur actuel, seules les données brutes sont extraites à une fréquence de 100kHz.

- Dans le futur détecteur 2 types de données devront être extraits: **trigger à 40MHz, et brutes jusqu'à 750kHz**. Pour parvenir à cela, **une électronique de lecture entièrement nouvelle est développée**.

→ Le  $p_T$ -module, où comment extraire des informations du trajectographe à 40MHz?

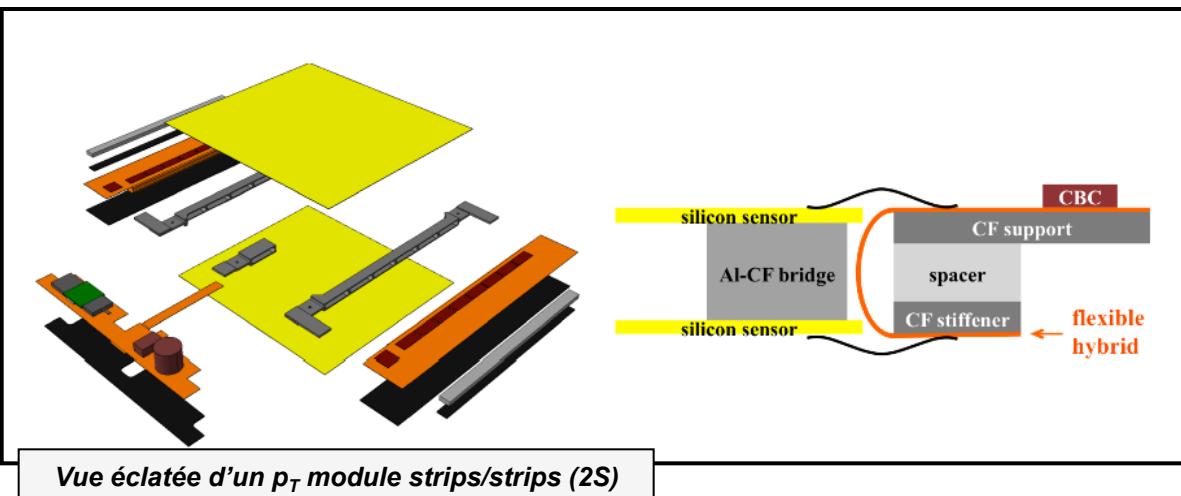

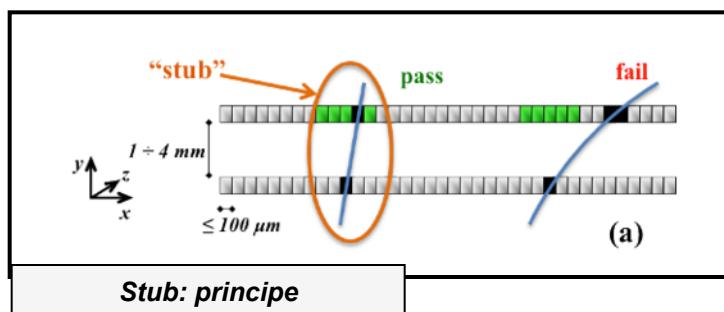

→ Les modules sont constitués de 2 couches de silicium séparées de qques mm.

→ Pour réduire la quantité de signal à extraire, on reconstruit seulement les coïncidences entre clusters correspondant à une trace de  $p_T$  élevé (**stub**).

→ Pour un  $p_T$  minimal de  $2\text{GeV}/c$ , le taux de réduction est d'environ 10. Suffisant pour sortir les infos.

→ Tout est fait au niveau du module. Implications importantes sur la mécanique, l'électronique,...

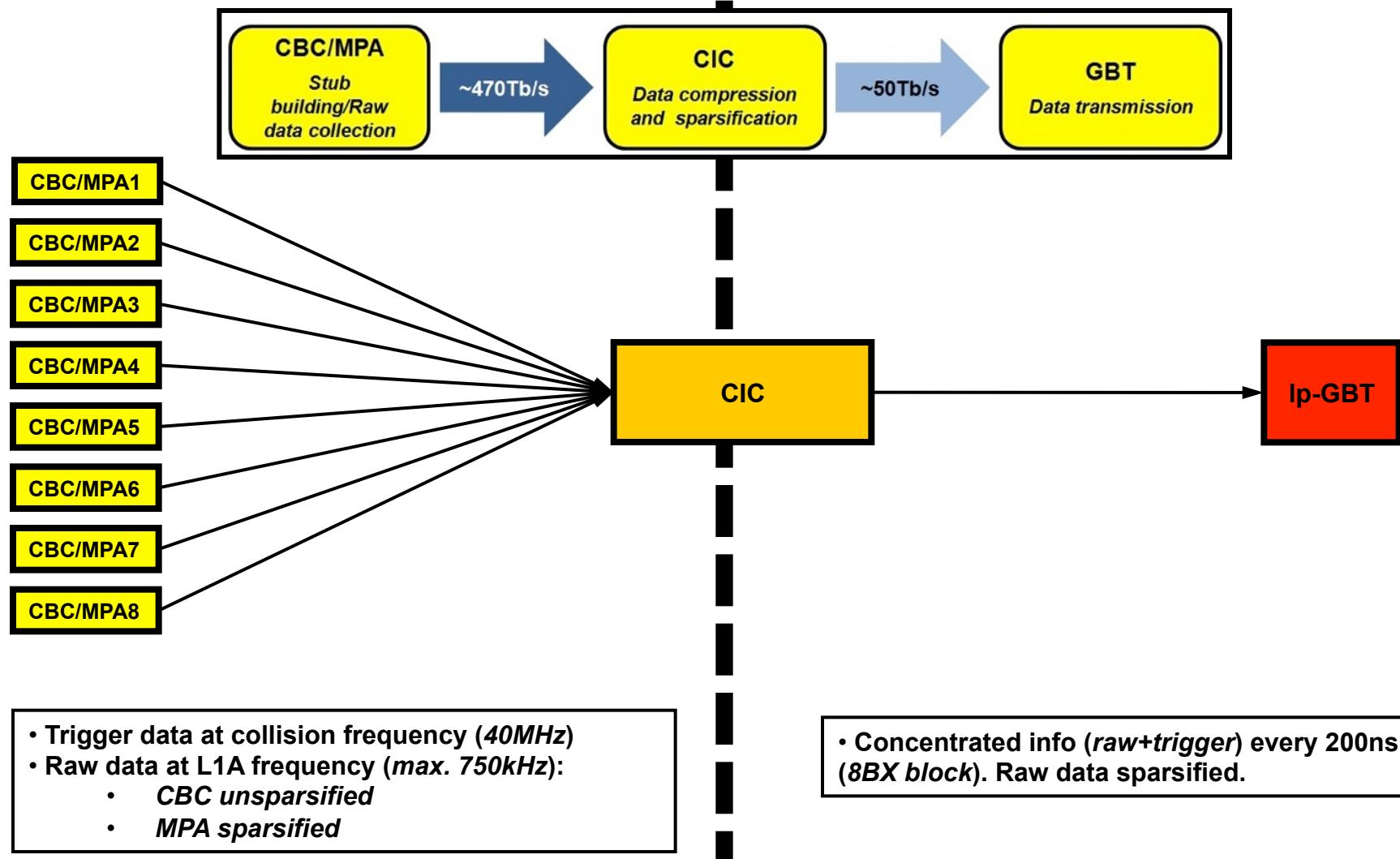

→ Le protocole d'extraction des données du futur tracker au niveau frontend:

→ Le cahier des charges du concentrateur:

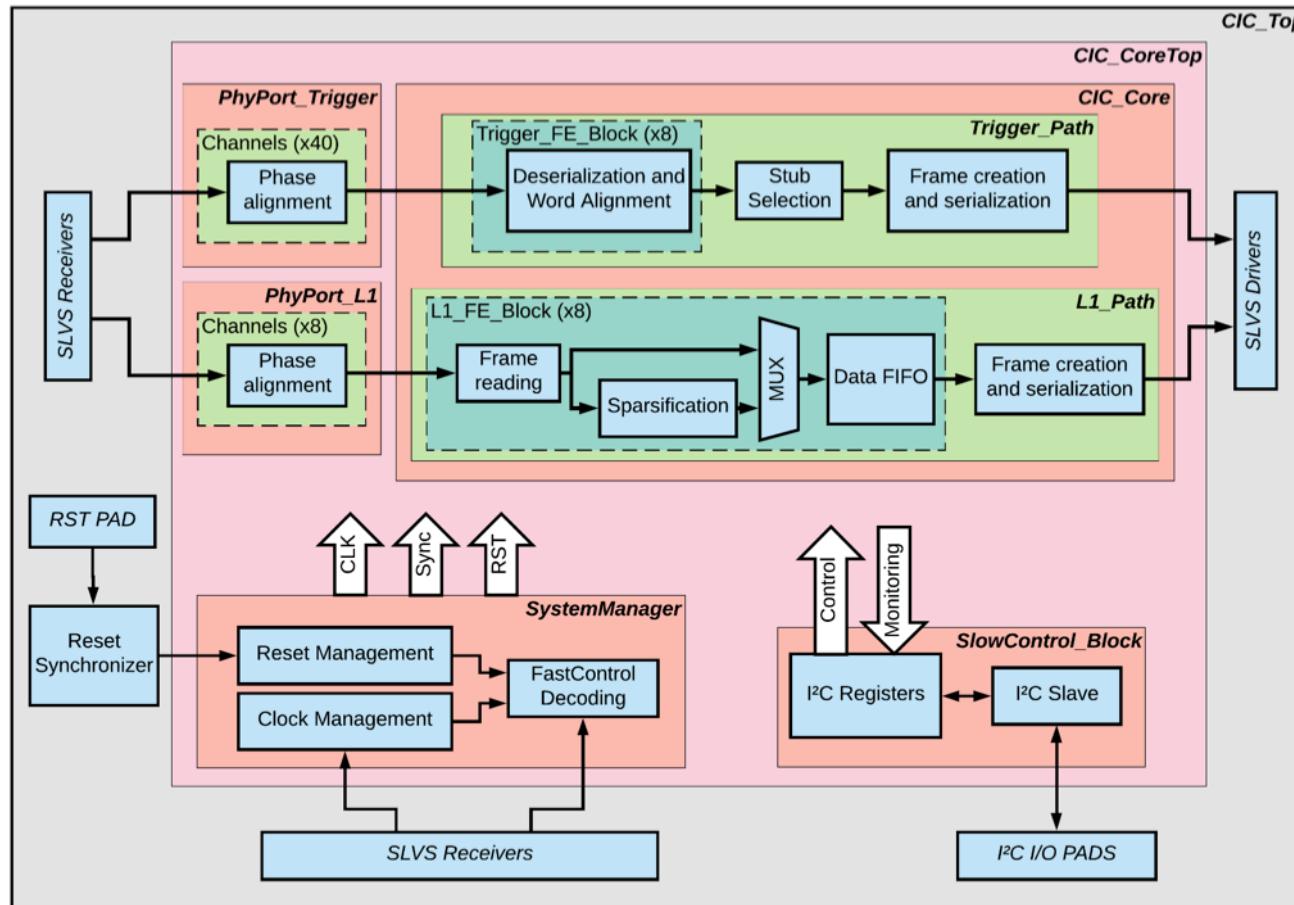

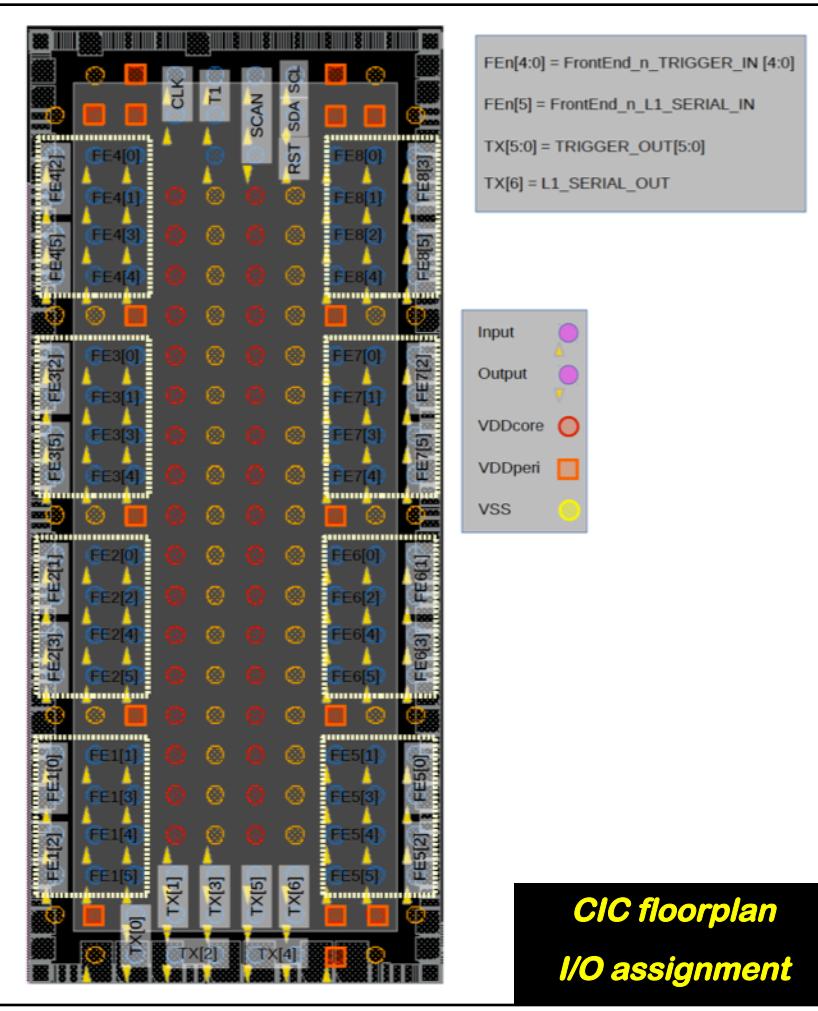

- Le CIC doit recevoir les données de 2 types d'ASICs différents (*MPA/CBC*) et doit fonctionner sur 2 hybrides différents

- **Technologie TSMC 65nm**

- Design digital-on-top, basé sur les cellules standard (*mis à part un bloc analogique en entrée (PHYport)*)

- 48 lignes à 320Mbps en entrée (*2 formats différents*)

- 7 lignes à 320/640Mbps en sortie, dans un format unique (**640 slt sur le CIC2**)

- Le coeur de l'ASIC doit pouvoir fonctionner à 2 tensions différentes: **1.0V** (PS) et **1.2V** (2S)

- **Design résistant aux radiations (*disponible seulement sur le CIC2*)**

- Corrige les problèmes potentiels des autres ASICs (*on arrive en dernier...*)

→ Modèle:

→ Le modèle a été entièrement revisité en 2017 afin de répondre correctement au cahier des charges. En particulier sur le traitement des horloges et des signaux de fast control (*resync, reset,...*)

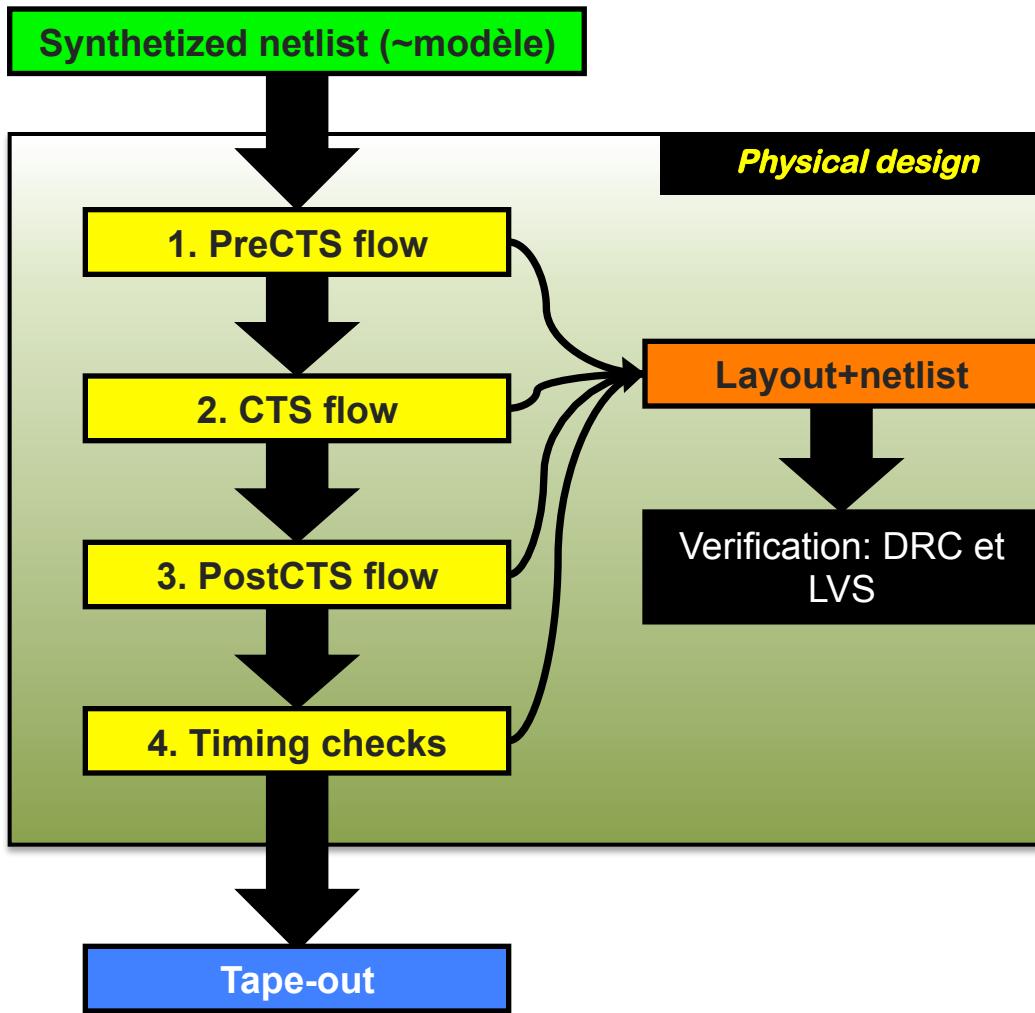

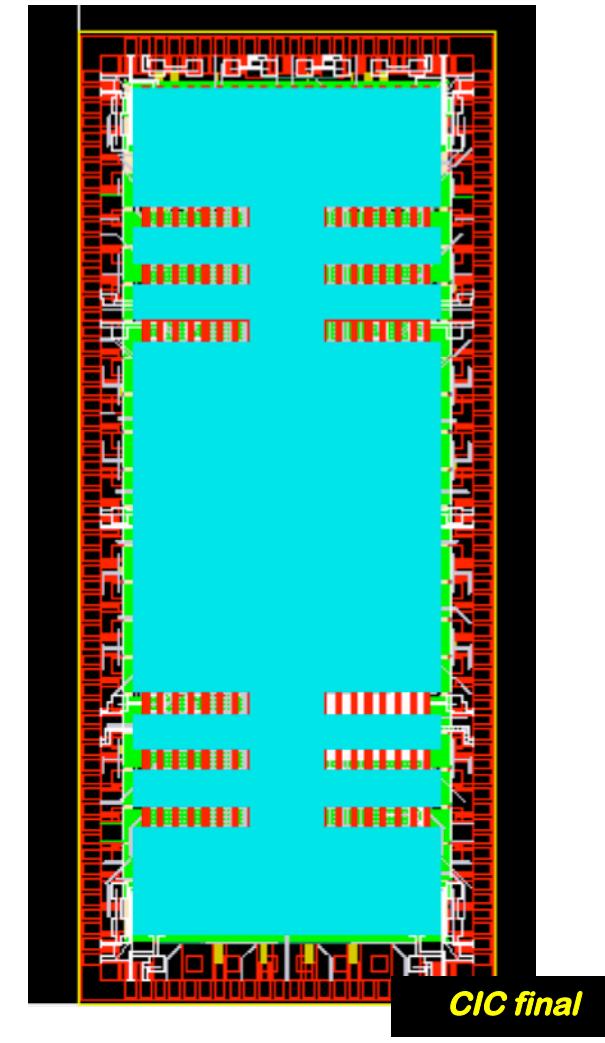

→ Design physique

L.Caponetto, B.Nodari

- Le processus de design du CIC est une suite d'étapes précisément définies (**flot de conception**)

- A chaque étape est produite une **netlist** qui est validée via un banc de test dédié (*IPNL et CERN*).

- **Le but du jeu est d'obtenir un design respectant les contraintes temporelles du chip.**

- Processus **long** (*pour le CIC la chaîne complète correspond à 1.5 jour de temps de calcul*) et **itératif** (*modifications*).

- Les différentes étapes du flot de conception ont été complétées au printemps 2018.

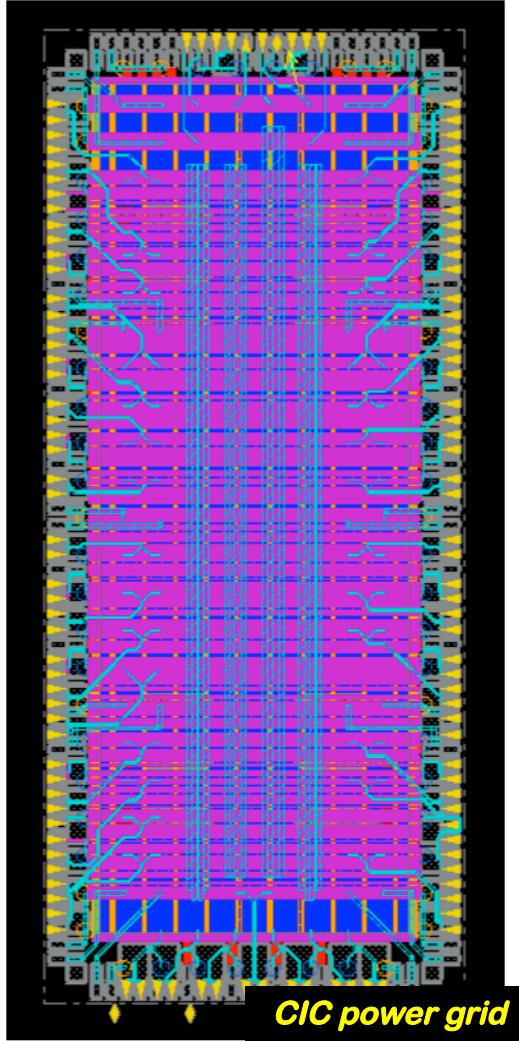

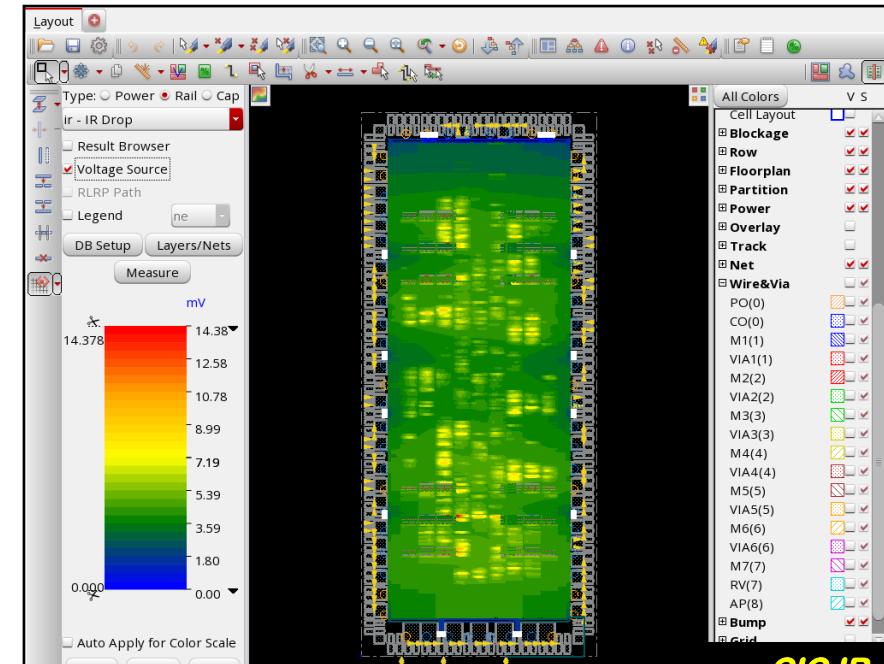

- Support important du CERN dans la dernière ligne droite (*cet été, 2FTE supplémentaires*) pour finaliser cette partie. Soutien également de Cadence (*via le CERN*) pour les études d'IR drop

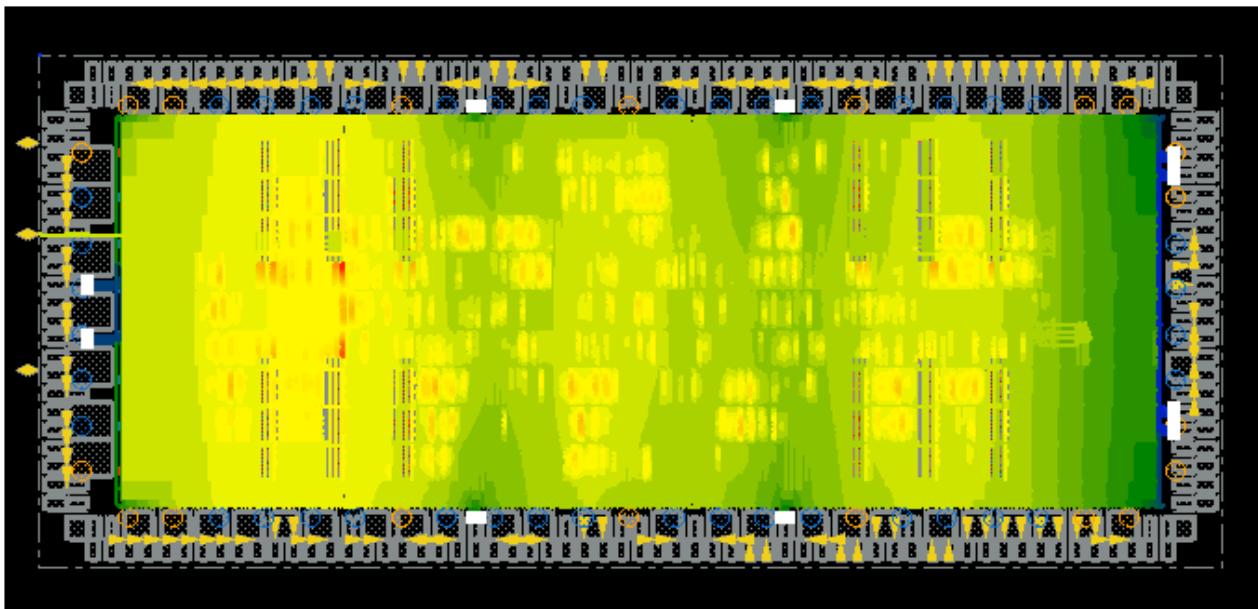

CIC IR drop

1. Principe

2. Statut du projet

3. CIC2

→ Design physique

L.Caponetto, B.Nodari

→ Statut du CIC1:

- Les dernières étapes (*DRC et LVS*) requièrent des modifications qui peuvent être complexes à implémenter (*eg modification du code rtl de base*). Ces étapes ont donc logiquement pris plus de temps que prévu (*le planning du CIC1 était relativement agressif*).

- **Le CIC1 a finalement été soumis à IMEC le 24 Septembre 2018.**

- Nous devrions recevoir ~100 ASICs d'ici la fin de cette semaine. Les ASICs partiront alors chez Novapack pour être connectés aux cartes de tests (*wirebonding*)

- Les premiers tests devraient avoir lieu (*si tout va bien*) juste avant Noel

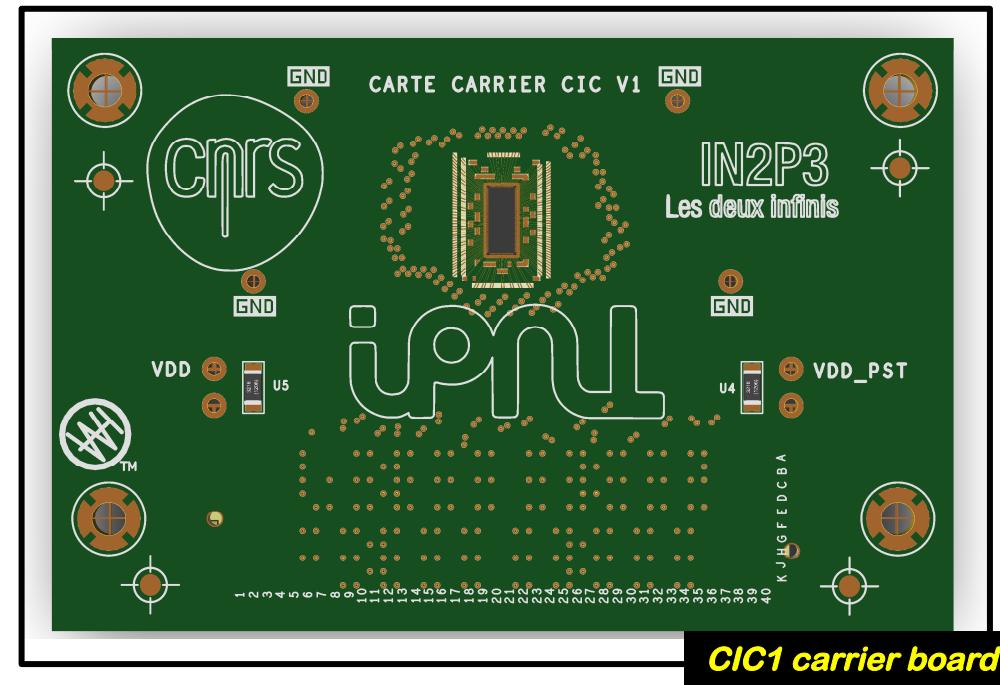

CIC1 carrier board

L.Caponetto, G.Galbit, C.Guerin, W.Tromeur

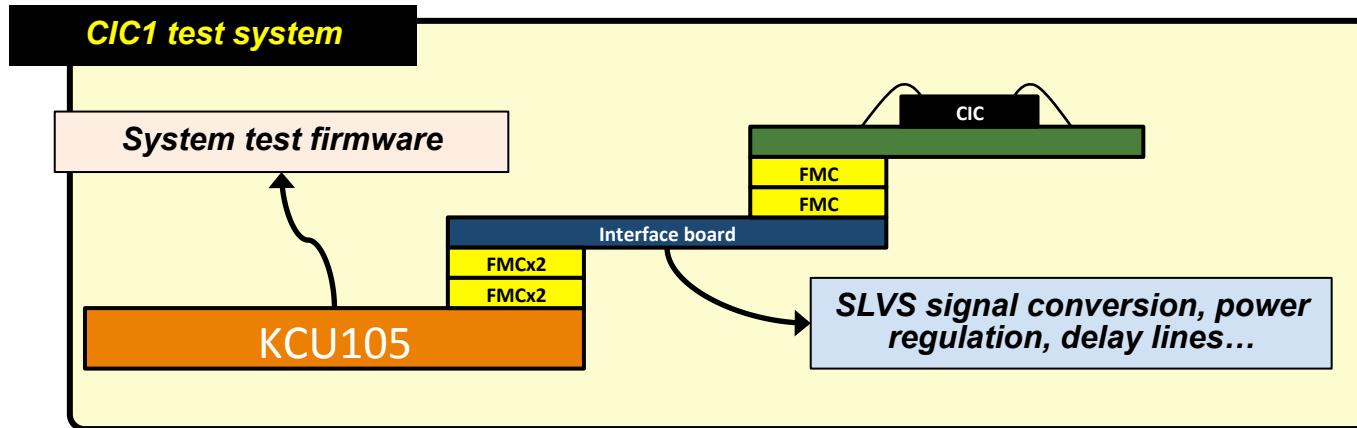

→ Système de test pour le CIC1:

→ Système pour le test de l'ASIC seul, l'intégration dans la chaîne de DAQ est testée au CERN

→ Basé sur 3 cartes:

1. **Carte support CIC1 (IPNL)**: système passif (30 cartes disponibles)

2. **Carte d'interface (IPNL)**: conversion des signaux, ajout de délais, alim (2 cartes à l'IPNL, 5 au CERN)

3. **Carte de pilotage (Xilinx KCU105)**: firmware de test

→ Le système est décrit en détails dans cette présentation de Juillet 2018:

[https://indico.cern.ch/event/746617/contributions/3086538/attachments/1692810/2723987/CIC\\_test\\_250718.pdf](https://indico.cern.ch/event/746617/contributions/3086538/attachments/1692810/2723987/CIC_test_250718.pdf)

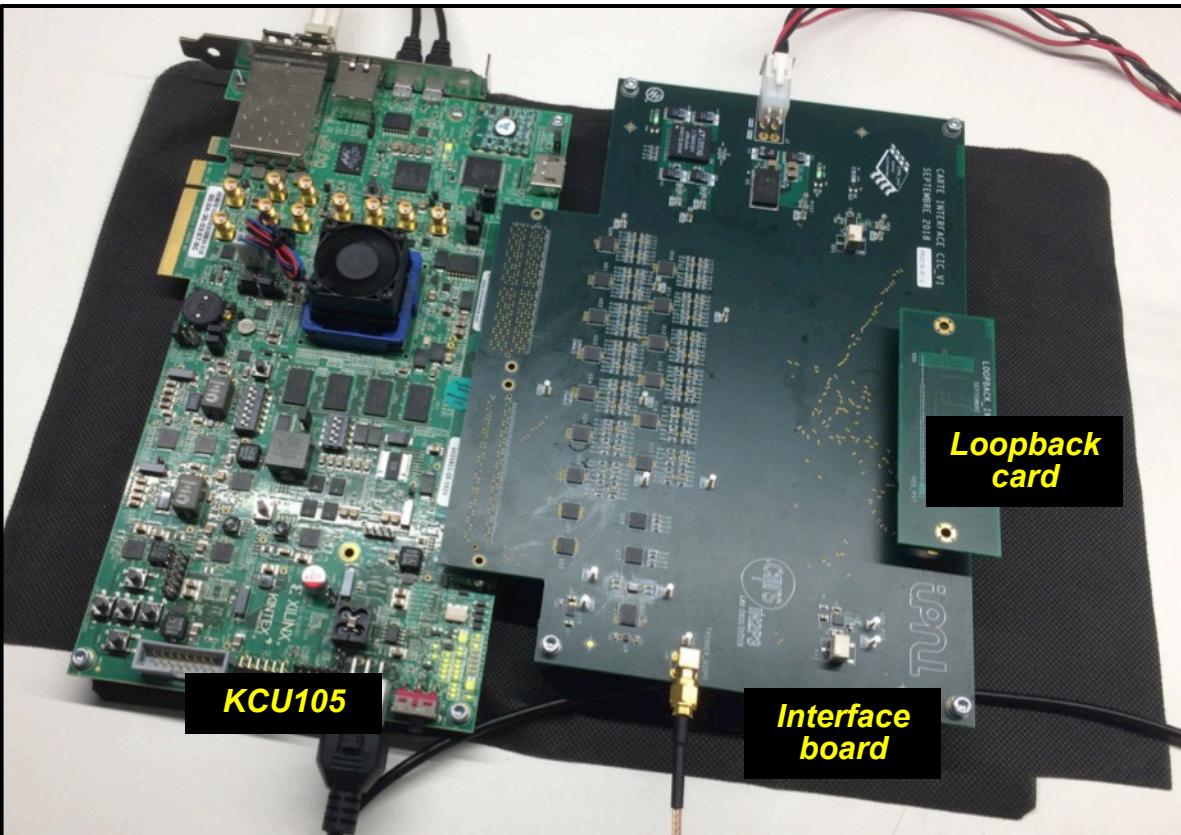

→ Statut du système:

G.Galbit, B.Nodari, W.Tromeur

- Les cartes ont été reçues fin octobre

- La carte d'interface a pu être débuggée avant d'avoir le CIC grâce à un connecteur de loopback développé pour l'occasion.

- La majeure partie du firmware a ainsi pu être testé en amont.

- Il ne reste plus qu'à développer l'interface software entre ce banc de test et celui utilisé pour tester le modèle du CIC1.

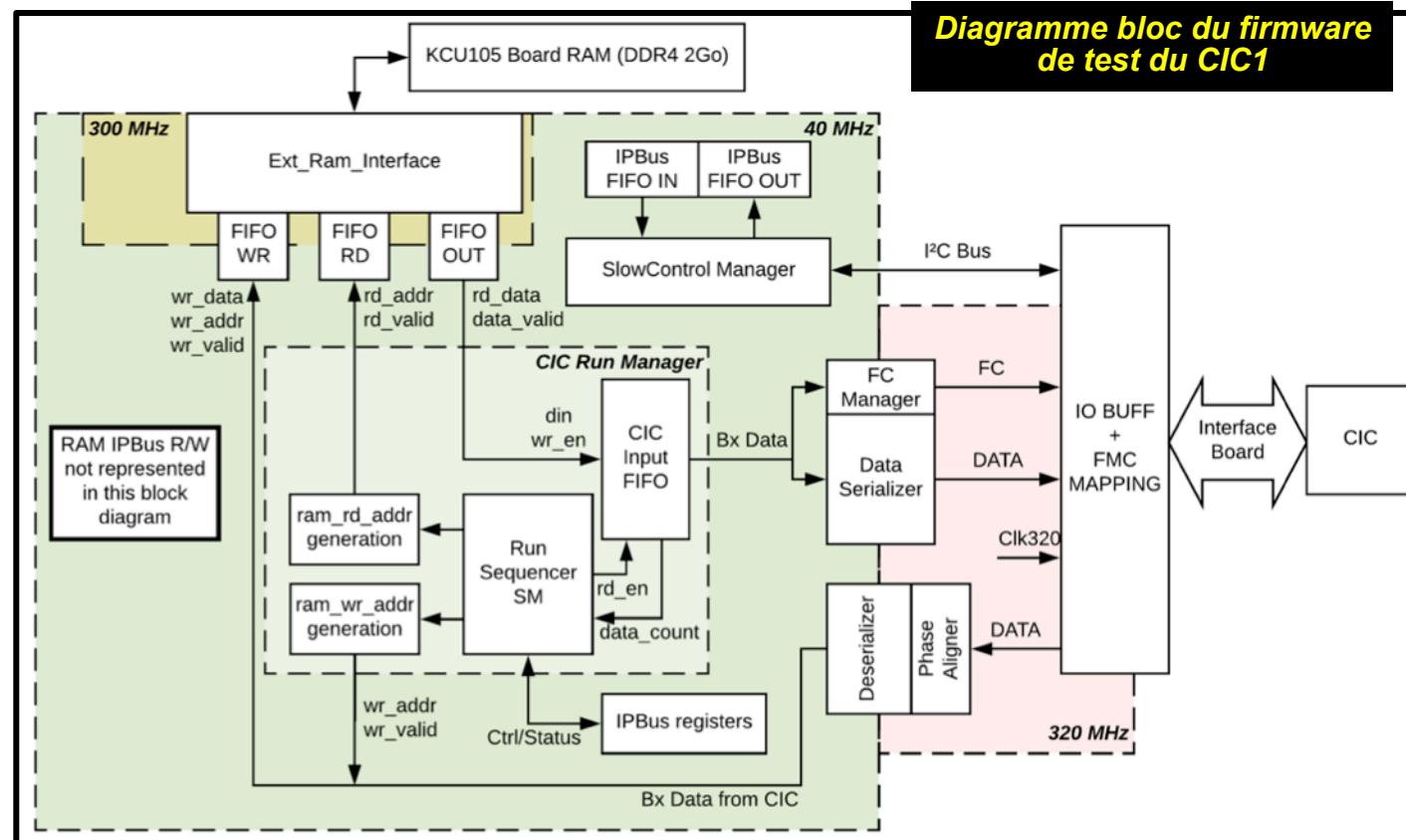

→ Firmware dédié:

→ Ce firmware s'inspire de celui développé pour le track trigger (*test des puces AM*). Beaucoup de blocs ont pu être réutilisés

→ Tout est prêt pour tester le CIC1 (*manque juste l'ASIC...*)

→ Le planning CIC1

- Si tout ce déroule comme prévu, les cartes équipées seront disponibles à partir du 17/12

- Quelques premiers tests pourront être faits avant Noël, mais les vrais tests débuteront en Janvier 2019. A partir de là, il y en aura pour environ 3~4 mois.

- **Ces tests devront se faire en parallèle avec les développements du CIC2.** Une post-doctorante va rejoindre le groupe en Janvier pour 2 ans, en partie pour renforcer cette activité.

→ CIC2

- Le projet (*au moins le planning*) est désormais géré par le groupe du CERN.

- Le travail a débuté dès Octobre par la triplication du modèle du CIC1 (*sauf la partie L1 qui doit être modifiée*)

- Les modifications de la partie L1 (**Geoffrey**) sont en cours (*le banc de test CIC1 étant prioritaire*)

- Des premiers tests de synthèse/placement (**Benedetta/Luigi**) ont été effectués (*une grande partie du flot de conception du CIC1 peut-être ré-utilisé*)

- Le planning du CERN annonce une fonderie CIC2 en Juin 2019. Compte-tenu des tests du CIC1 et du travail restant à faire sur le modèle (*triplication, reduction de la conso,...*) c'est très optimiste (*success-oriented si on veut utiliser le nouveau terme à la mode...*).

- Le CIC1 a finalement vu le jour, **c'est le premier ASIC complet en technologie 65nm réalisé à l'IN2P3.**

- Nous saurons dans quelques mois si c'est le premier ASIC complet **et fonctionnel...**

- Le développement du CIC2 a déjà commencé. Même si le CIC1 fonctionne parfaitement, les améliorations/modifications à fournir ne sont pas négligeables. A suivre...