- 1. Principe

- 2. Statut du projet

- 3. Futur proche et moins proche

***L.Caponetto, G.Galbit, B. Nodari, S.Scarfi, S.Viret***

*IPNL, CERN*

→ Le futur détecteur de traces de CMS :

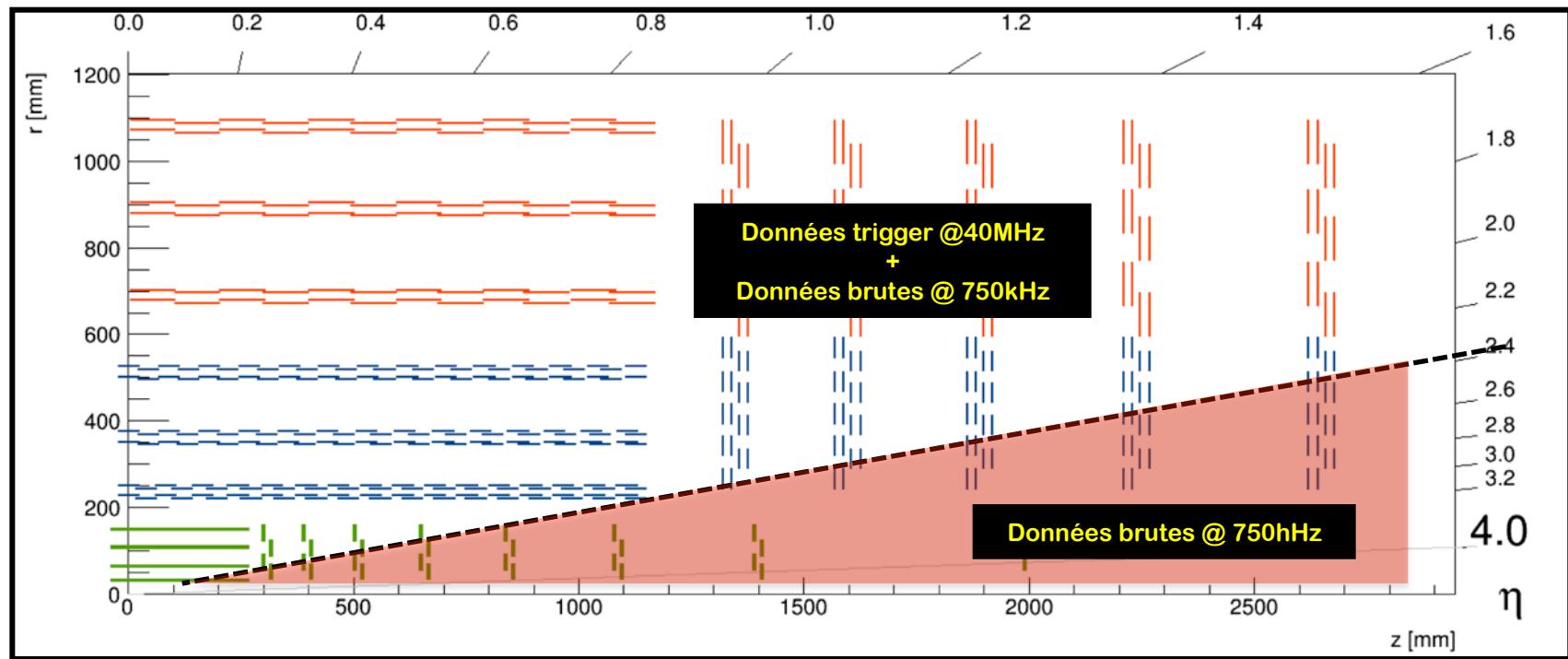

→ Dans le détecteur actuel, seules les données brutes sont extraites à une fréquence de 100kHz.

→ Dans le futur détecteur 2 types de données devront être extraits: **trigger à 40MHz, et brutes jusqu'à 750kHz**. Pour parvenir à cela, **une électronique de lecture entièrement nouvelle doit être développée**.

## 1. Principe

## 2. Statut du projet

## 3. Futur proche et moins proche

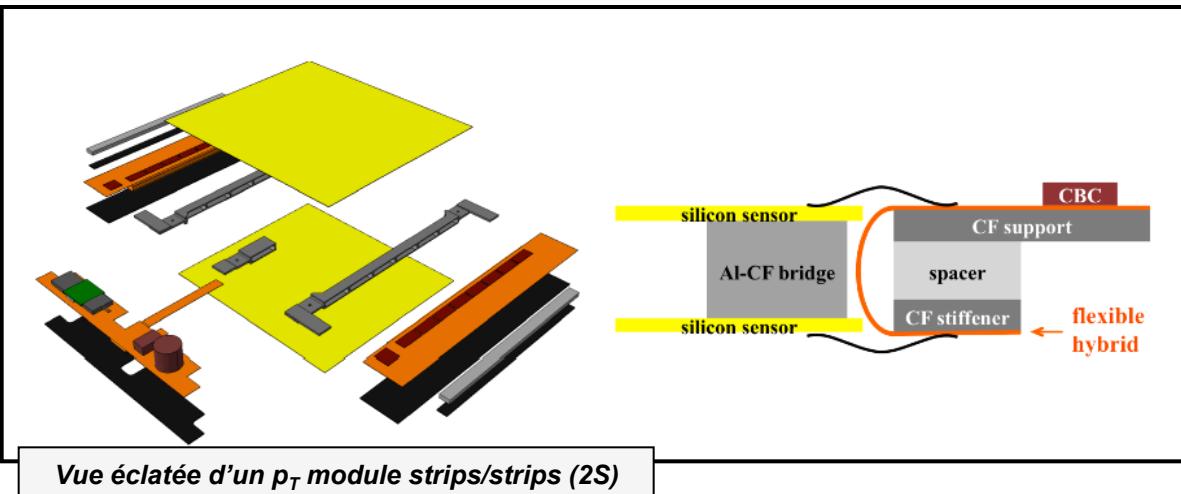

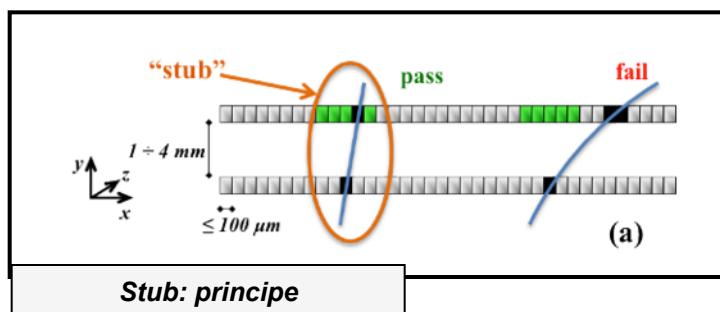

### → Le $p_T$ -module, où comment extraire des informations du trajectographe à 40MHz?

→ Les modules sont constitués de 2 couches de silicium séparées de qques mm.

→ Pour réduire la quantité de signal à extraire, on reconstruit seulement les coïncidences entre clusters correspondant à une trace de  $p_T$  élevé (**stub**).

→ Pour un  $p_T$  minimal de 2GeV/c , le taux de réduction est d'environ 10. Suffisant pour sortir les infos.

→ Tout est fait au niveau du module. Implications importantes sur la mécanique, l'électronique,...

1. Principe

2. Statut du projet

3. Futur proche et moins proche

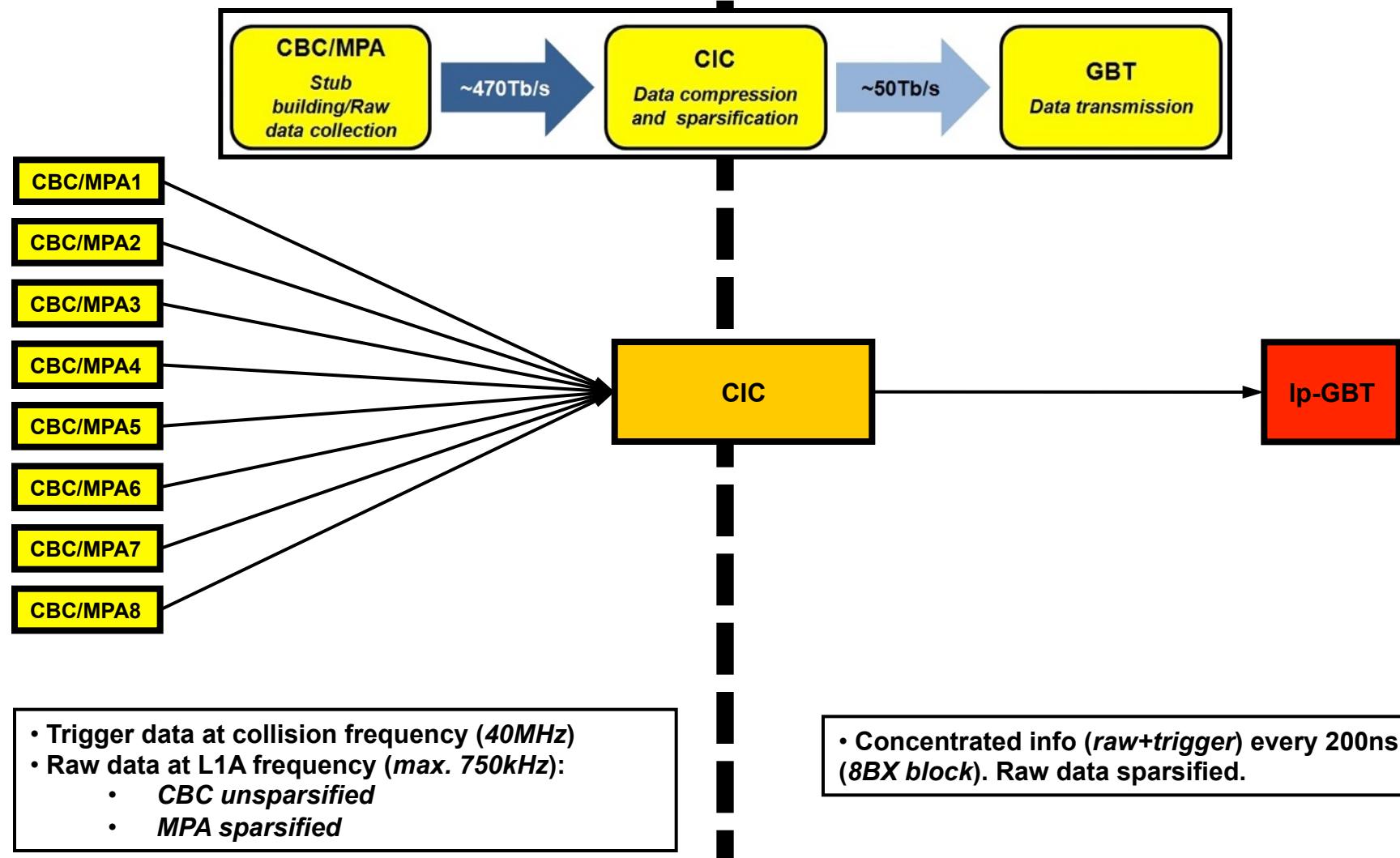

→ Le protocole d'extraction des données du futur tracker au niveau frontend:

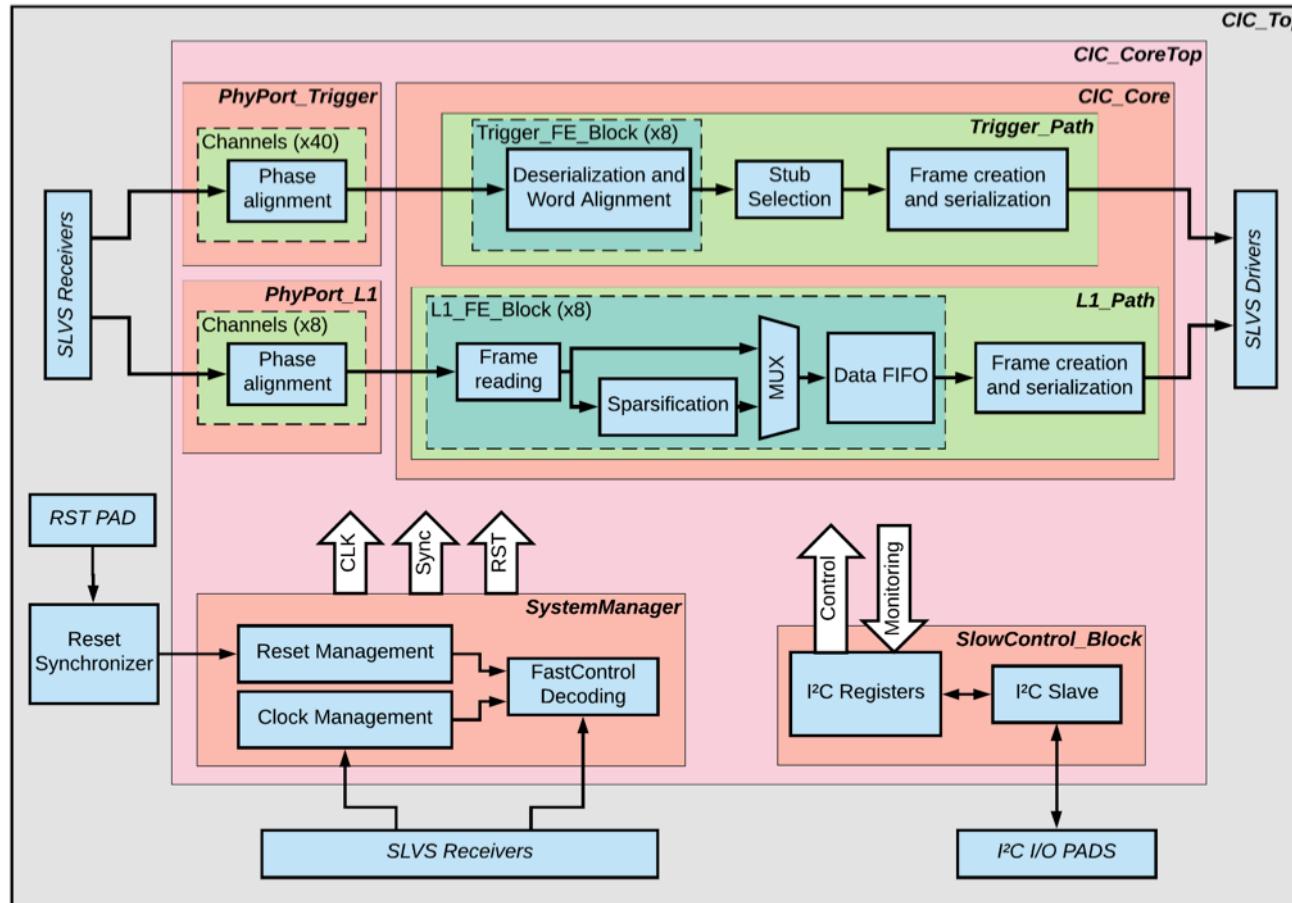

→ Le cahier des charges du concentrateur:

- Le CIC doit recevoir les données de 2 types d'ASICs différents (*MPA/CBC*) et doit fonctionner sur 2 hybrides différents

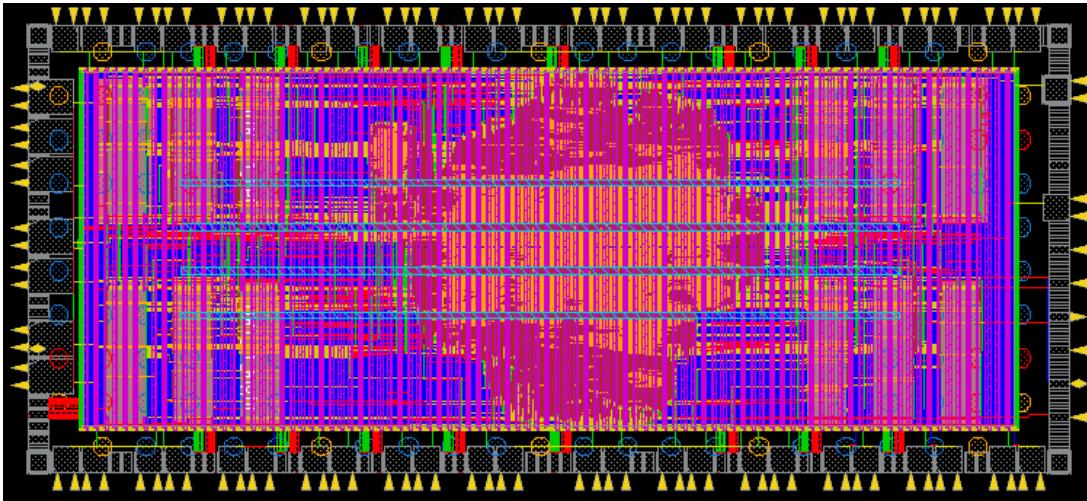

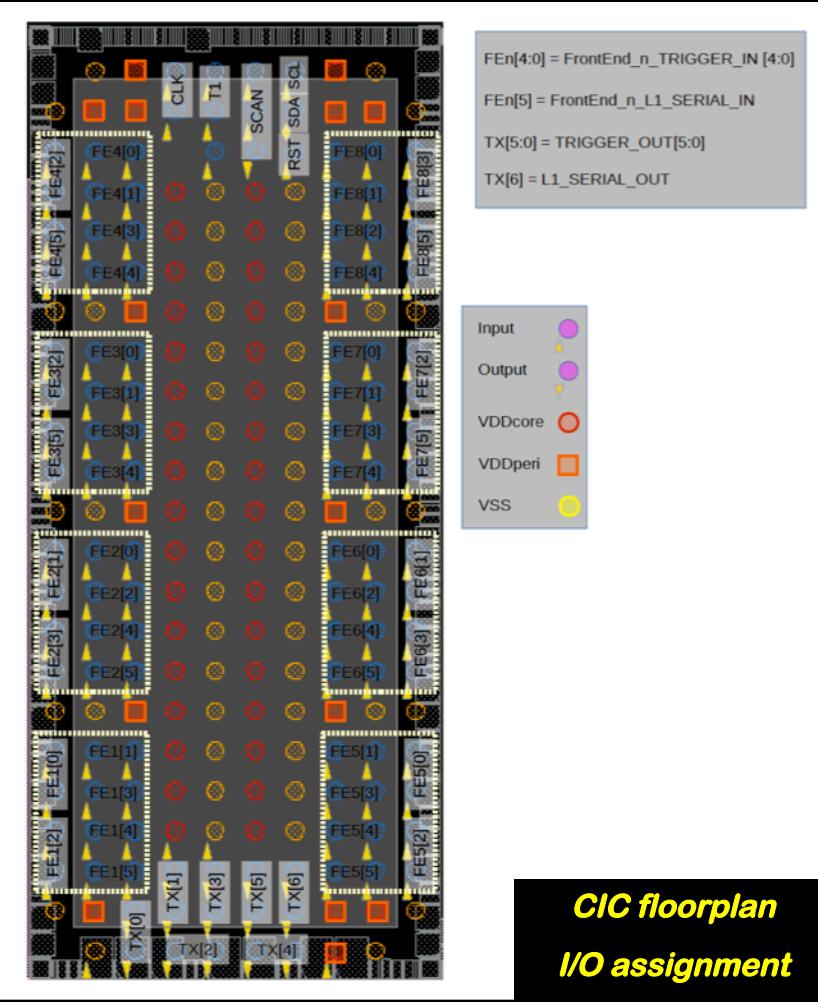

- **Technologie TSMC 65nm**

- Design digital-on-top, basé sur les cellules standard (*mis à part un bloc analogique en entrée*)

- 48 lignes à 320Mbps en entrée (*2 formats différents*)

- 7 lignes à 320/640Mbps en sortie, dans un format unique

- Le coeur de l'ASIC doit pouvoir fonctionner à 2 tensions différentes: **1.0V (PS)** et **1.2V (2S)**

- **Design résistant aux radiations (*disponible seulement sur le CIC2*)**

- Corrige les problèmes potentiels des autres ASICs (*on arrive en dernier...*)

→ Modèle:

→ Le modèle a été entièrement revisité en 2017 afin de répondre correctement au cahier des charges

→ **Modèle:**

- Le projet a été présenté en détails au cours d'une **revue de design externe en Décembre 2017**. Cette revue a permis de valider le modèle développé en 2017, mais a mis en évidence des imprécisions dans la définition des interfaces (*communication entre les ASICs, procédures de démarrage et de calibration,...*)

- Les six derniers mois ont été consacrés à la prise en compte de ces problèmes dans le modèle du CIC (*les autres ASICs étant déjà réalisés, le CIC est le seul point où ils peuvent être encore réglés*). Cela a induit un retard sur le projet, mais il est important de signaler que ce retard n'est pas intrinsèque au CIC.

- La majeure partie de ces modifications a été effectuée, on peut désormais considérer que le modèle est terminé (*sauf si le cahier des charges change à nouveau....*)

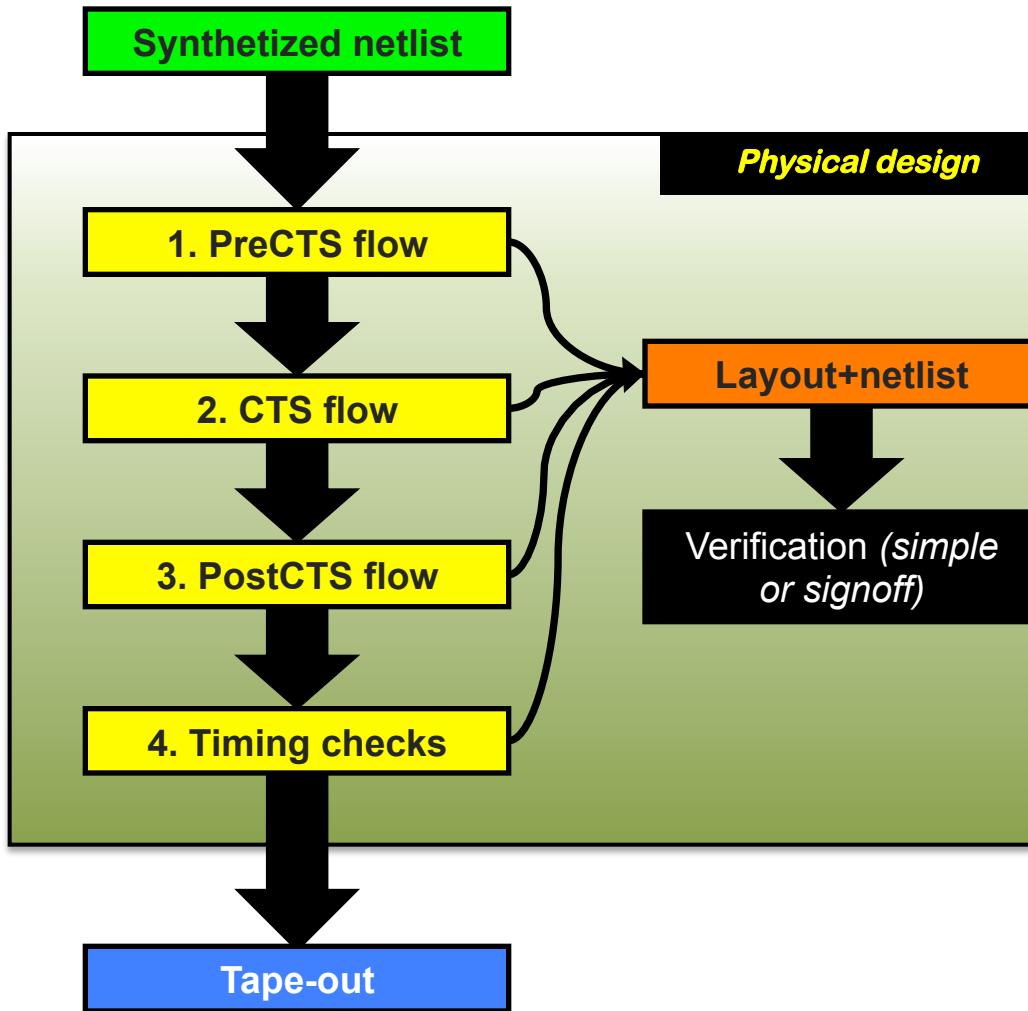

→ Design physique

- Le processus de design du CIC est une suite d'étapes précisément définies (**flot de conception**)

- A chaque étape est produite une **netlist** qui est validée via un banc de test dédié.

- **Le but du jeu est d'obtenir un design respectant les contraintes temporelles du chip.**

- Processus **long** (pour le CIC la chaîne complète correspond à 1.5 jour de temps de calcul) et **itératif** (modifications).

→ Design physique

- Les différentes étapes du flot ont été implémentées.

- Le modèle final a été testé jusqu'à l'avant dernière phase (*post-CTS*). Pas de problèmes majeurs jusqu'à présent, c'est plutôt encourageant.

- La finalisation du processus dépend de la réalisation des jalons suivants:

- Disponibilité de protections ESD pour le CIC (fournies par le CERN)

- Validation du routage de l'hybride de front-end des modules PS (CERN)

→ **Développement du CIC1 et du CIC2**

→ L'objectif actuel est une fonderie en Juillet 2018 et une caractérisation pour la fin de l'année.

- Cet objectif dépend fortement des contraintes extérieures mentionnées précédemment, contraintes qui ont déjà engendré d'important retards sur le projet. Mais jusqu'ici tout va bien...

- Une fois le modèle du CIC1 terminé, les modifications nécessaires pour le CIC2 (***triplication***) seront implémentées. Ce travail se fera en parallèle avec la caractérisation du CIC1, afin d'avoir une transition rapide (***~1an***) entre CIC1 et CIC2.

- **Le CIC2 pourra être considéré comme un ASIC de préproduction**, et être utilisé pour le développement et le test des premiers modules. Le CIC1 également (*même pinout*) mais dans une moindre mesure (*pas de testbeam possible*)

→ Production du CIC

- L'ASIC final sera produit en technologie TSMC65, et sera billé (*flip-chip*)

- **Tester une production de chip de ce type est complexe**, et la procédure n'est pas encore clairement définie. Le CERN ayant les mêmes contraintes, nous allons nous baser sur le protocole qu'ils mettront en place.

- Le coût de cette phase est donc difficile à évaluer, mais nous pouvons anticiper le besoin d'un ou deux AI pour prendre part à la campagne de validation des 30000 CICs.

→ **Dans tous les cas ce projet doit être terminé en 2022.**

→ **Besoins physiciens**

- Je vais continuer à encadrer ce projet, à plein temps jusqu'à la réalisation du CIC2 (*fin 2019*).

- A partir de là il y aura besoin d'un encadrement moins important (*0.5FTE suffiront*), que je continuerais à assurer en parallèle de mon activité post-CMS. **Dans tout les cas, je m'engage à ne pas quitter ce projet tant qu'il ne sera pas livré.**

- C'est un projet très technique, mais un post doc physicien serait très utile (*entre 2019 et 2021*) pour participer aux test de caractérisation de l'ASIC (*tests en faisceau, tests de base,...*)

→ Aspects budgétaires

→ Ces chiffres sont encore préliminaires, surtout les aspects non-core (*procédure de test des ASICs finals pas encore définie*)

| Institut                                      | WBS      | 2018     |     |      | 2019     |     |       | 2020     |        |        | 2021     |      |      | 2022     |      |      | Total par categorie |       |         |           |

|-----------------------------------------------|----------|----------|-----|------|----------|-----|-------|----------|--------|--------|----------|------|------|----------|------|------|---------------------|-------|---------|-----------|

|                                               |          | Non CORE | CDD | CORE | Non CORE | CDD | CORE  | Non CORE | CDD    | CORE   | Non CORE | CDD  | CORE | Non CORE | CDD  | CORE | Non CORE            | CDD   | CORE k€ | CORE kCHF |

| IPNL                                          |          | 45,0     | 0,0 | 0,0  | 15,0     | 0,0 | 180,0 | 15,0     | 38,2   | 1090,0 | 15,0     | 76,3 | 10,0 | 10,0     | 38,2 | 10,0 | 100,0               | 152,7 | 1290,0  | 1573,8    |

| Design of first CIC proto                     | 2.1.2.7  | 10,0     |     |      |          |     |       |          |        |        |          |      |      |          |      |      |                     |       | 0,0     | 0,0       |

| First CIC proto validation                    | 2.1.2.9  | 25,0     |     |      | 5,0      |     |       |          |        |        |          |      |      |          |      |      |                     |       | 0,0     | 0,0       |

| CIC final proto design                        | 2.1.2.10 |          |     |      |          |     | 150,0 |          |        |        |          |      |      |          |      |      |                     |       | 150,0   | 183,0     |

| CIC final proto validation                    | 2.1.2.12 |          |     |      |          |     | 20,0  |          |        | 15,0   |          |      |      |          |      |      |                     |       | 35,0    | 42,7      |

| CIC/MPA/SSA wafer UBM and dicing, CIC testing | 2.1.2.16 |          |     |      |          |     |       | 38,2     | 1050,0 |        | 76,3     |      |      |          | 38,2 |      |                     |       | 1050,0  | 1281,0    |

| CIC test line at IPNL                         |          |          |     |      |          |     | 10,0  |          |        | 25,0   |          | 10,0 |      |          | 10,0 |      |                     |       | 55,0    | 67,1      |

| Missions                                      |          | 10,0     |     |      | 10,0     |     |       | 15,0     |        |        | 15,0     |      | 10,0 |          |      |      |                     |       | 0,0     | 0,0       |

→ Beaucoup de dépenses CORE d'ici à 2020.

- Le projet CIC commence enfin à sortir la tête de l'eau, grâce au **travail remarquable des ingénieurs de l'IPNL depuis 2017**.

- Les retards actuels ne sont pas imputables à des problèmes internes, mais plutôt dus à des modifications tardives du cahier des charges de l'ASIC et à la non-disponibilité d'informations nécessaires à la réalisation du chip

- Compte-tenu de la pression importante exercée sur le projet pour la réalisation du CIC1, il est assez complexe de se projeter au-delà (*production et validation*) pour le moment, d'où la relative imprécision de nos demandes.