# Retriggering analysis (etc.)

Y. Miura, T. Suehara (Kyushu University)

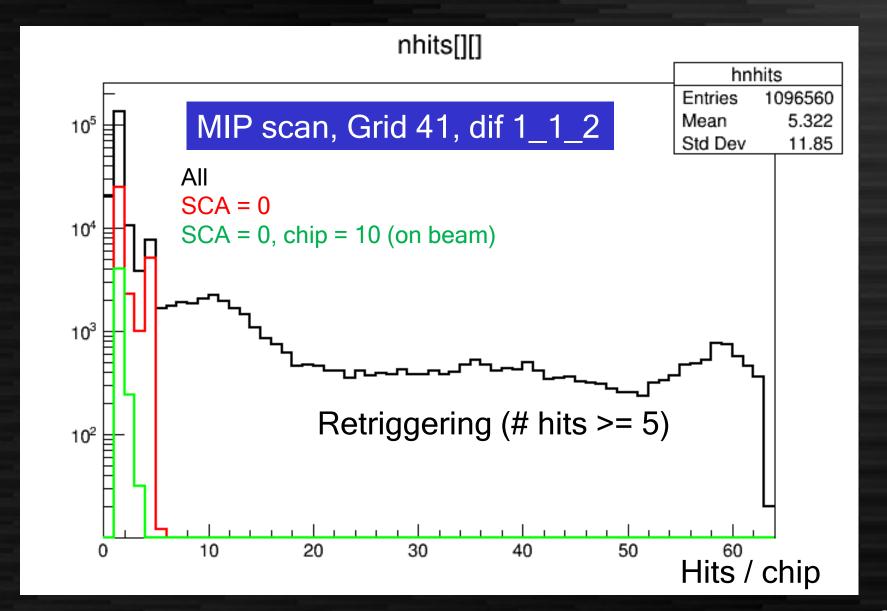

#### # of hits

## # of events (Grid 41, dif 1\_1\_2)

|                          | All events        | SCA = 0 | Chip 3 or 10 (on beam) | Other chips (not on beam) |

|--------------------------|-------------------|---------|------------------------|---------------------------|

| Empty event (0 hits)     | 20509<br>(9.5%)   | 10      | 13824<br>(11.7%)       | 6685<br>(6.8%)            |

| Normal event (1-4 hits)  | 157589<br>(72.8%) | 33595   | 102152<br>(86.8%)      | 55437<br>(56.1%)          |

| Retriggering (>= 5 hits) | 38517<br>(17.8%)  | 20      | 1756<br>(1.5%)         | 36761<br>(37.2%)          |

| Total                    | 216615            | 33625   | 117732                 | 98883                     |

Chip 3/10 are full at around 1 - 1.5 cycle (4000-6000 bx) Normal: Empty around 8:1 (not dependent on beam) Retriggering occurs more in no-beam chips (probably due to longer live time)

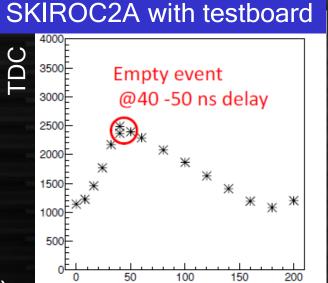

## **Empty event**

Empty event occurs at the edge of BX clock

- "Trigger high" remains at the next BX → triggering at BX and BX+1

- Confirmed at testboard by variable delay (~10 ns range with SKIROC2A)

bunch clock delay [ns]

Practically OK for real ILC detector since we do not expect hits just before next BX

### Retriggering

- Many hits at BX+2, +3, ...

- With usually no ADC fluctuation (only trigger is affected)

- Sometimes continue 5-10 SCAs

- → consumed up most of SCAs... harmful in real ILC

- Must be an issue to solve in ASIC or PCB

- Should identify and improve in the next version

- Much better than FEV8

- In FEV8 SCA>0 are hardly usable due to retriggering

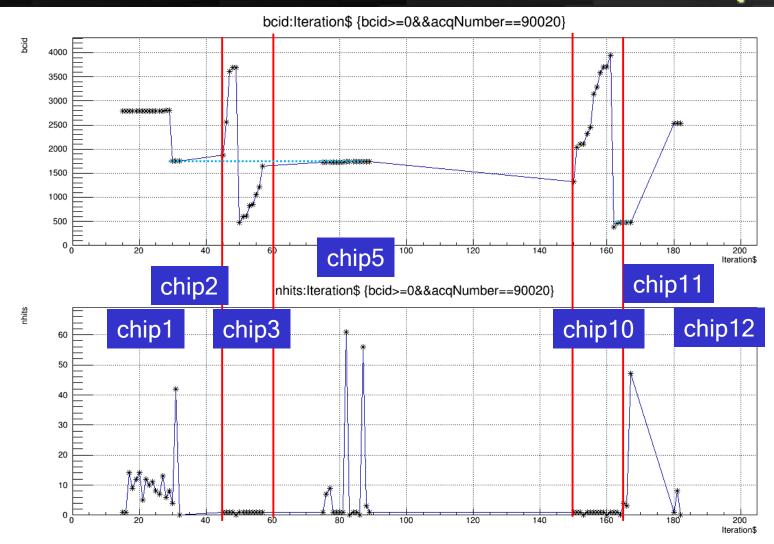

#### BX distribution on each chip

Relation on chip 2-5, 10-11?

Iteration = chip \* 15 + SCA

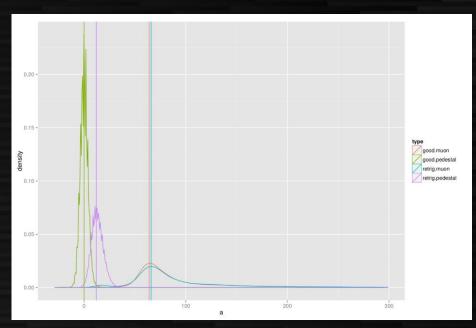

## Retriggering and double pedestal

Well known issues in BT2015 (V. Balagura, 21 Jan. 2016)

What causes "mode change" to right pedestal (then retrig.) is totally unknown

We have "double pedestal" in some of channels

What we found:

Retriggering must (100%!) occur after the "right pedestal"

Retriggering must not (100%!) occur after the "left pedestal" except "empty event" occurs

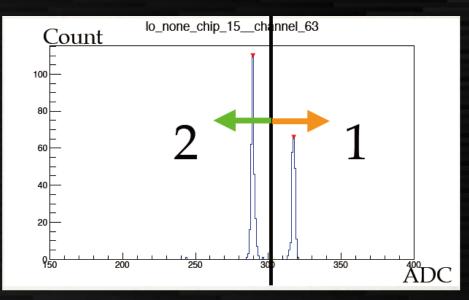

### Reminder: double pedestal

Low gain: separation is clear (at least in SCA 0)

High gain: separation is not clear

Difference on ADC at two peaks are similar in low and high gain

Difference on ADC by channels varies (0-30 ADC count)

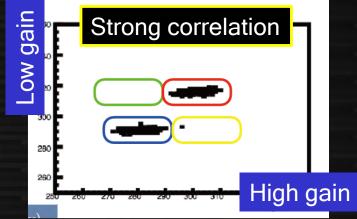

#### Reminder: double pedestal

Pedestal position (L/R) inside the chip is highly correlated but no strong correlation seen among different chips

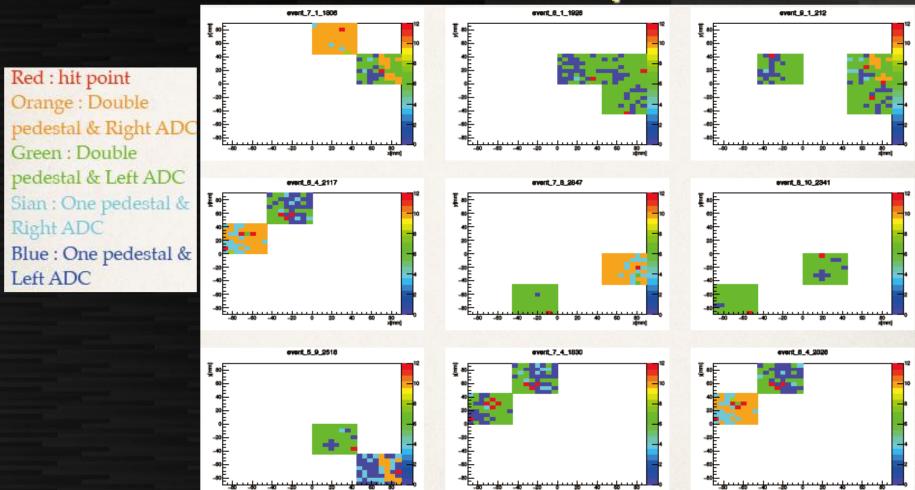

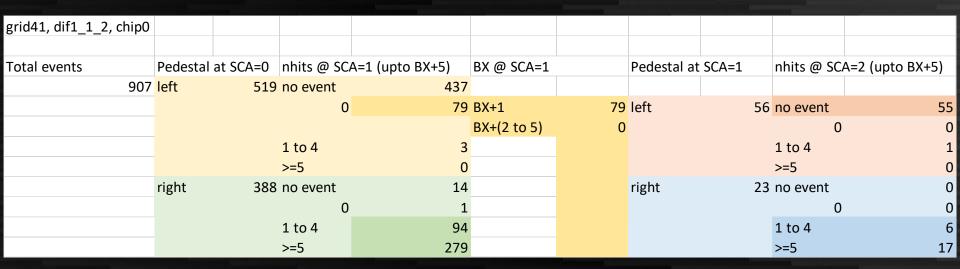

# Retriggering and empty event

- Chips not on beam (to get more "right" pedestal)

- "Left" pedestal at SCA=0: mostly no event and empty event

- "Right" pedestal at SCA=0: mostly retriggering (have to check the 15 events without retriggering)

- 30% of empty events go to "right" pedestal at SCA=1

- "Left" pedestal at SCA=1: no event (except 1)

- "Right" pedestal at SCA=1: retriggering at SCA=2

Empty event can change the pedestal state

Taikan Suehara et al., SiW-ECAL TB analysis meeting, 3 Aug. 2017 page 10

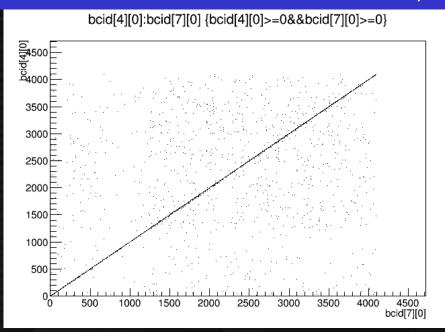

#### Additional: correlation with others

Grid 41, DIF 1\_1\_4

Correlation is weaker in other DIFs, but still exists

Bcid[4][0] and [7][0] are highly correlated

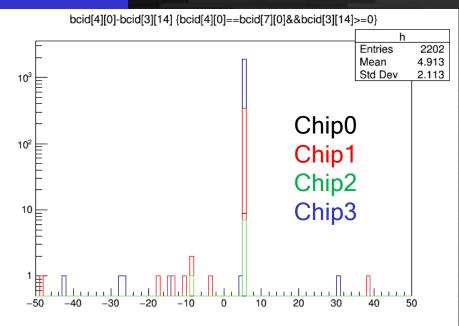

Correlation between bcid[][14] and bcid[4][0] (==bcid[7][0])

Chip 4 and 7 are often fired 5 BX after some chip comes to full

→ "busy" may cause some effect

### Summary & plan

- Understanding what causes retriggering (and mode change of pedestal) is essential

- To fully activate DAQ during beam in ILC

- Empty event can cause mode change (but other reason also exists)

- If we got some idea on the cause we can try to improve PCB or ASIC on the next version

- We have very little manpower until September.

I can do a little amount of work (~10% FTE)

Yu will come back just before CALICE. Some fraction of his time can be used for additional analysis.

- We may be able to invite some undergraduate students for analysis (if they're interested in) from October.

- Talk on CALICE and LCWS: both Yu and I are available