# Le système de "readout" de l'expérience LHCb

### **Sommaire**

- Nouvelle architecture du système de lecture LHCb.

- Carte prototype PCIe40

- Architecture globale

- Conception

# Architecture générale

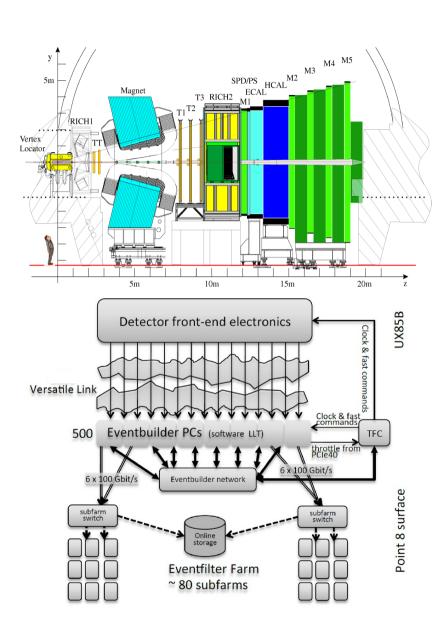

- Système de lecture en surface

- → Distance ~350m entre FE & RO

- ~ 1500 liens optiques

- ~ 500 cartes de lecture

- ~ 24 liens optiques / carte

- ~ 100 Kbytes par événement

- ~ 32 Tb/s totale de bande passante

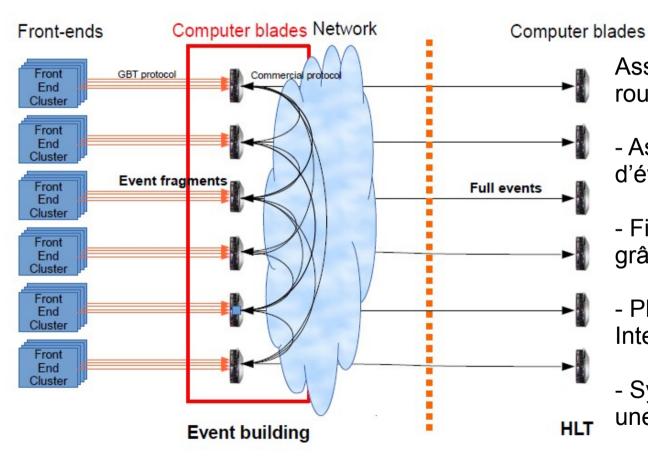

# **Architecture initiale pour LHCb**

Chaque fragment d'événement est routé <u>sans filtrage</u> « Hardware » à travers le système de lecture vers un CPU de la ferme de serveurs.

Basé sur l'ATCA

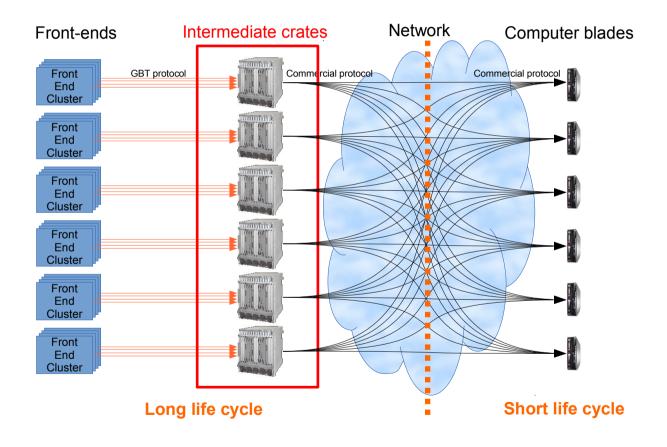

### Nouvelle architecture lecture données

#### Les cartes de lecture sont directement placées dans les serveurs existants

► Tirer avantage des nouvelles architectures CPU!

Assemblage de l'événement /serveur routage des fragments d'événement.

- Assemblage & reconstruction d'événement en temps réel.

- Filtrage « software » d'événement grâce aux nouvelles architectures CPU.

- Plus d'étage d'acquisition Intermédiaire

- Système acquisition basé sur une carte de type PCIe.

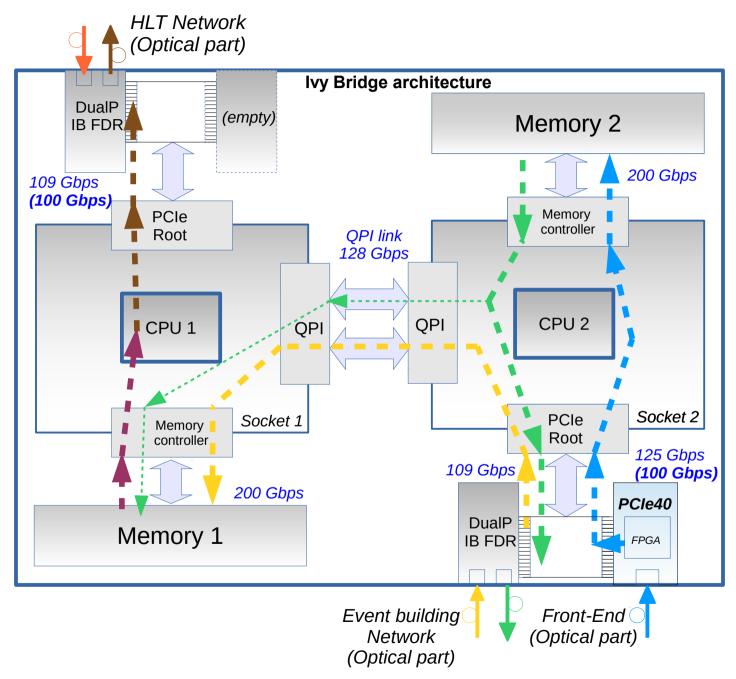

### Chemin des données dans le serveur

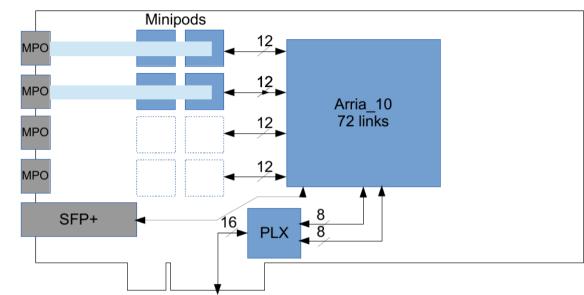

# PCIE40 Schéma synoptique

48 liens optiques en E/S jusqu'à 10 Gbps

Lien optique bidirectionnel Pour l'interface TFC

Bande passante ~100 Gbps en PCle Gen3 x16

- PCIE40 => carte générique configurable en:

- Acquisition des données du FE (@100Gbps)

- Supervision de la distribution du TFC.

- Distribution du TFC et ECS vers les cartes FE.

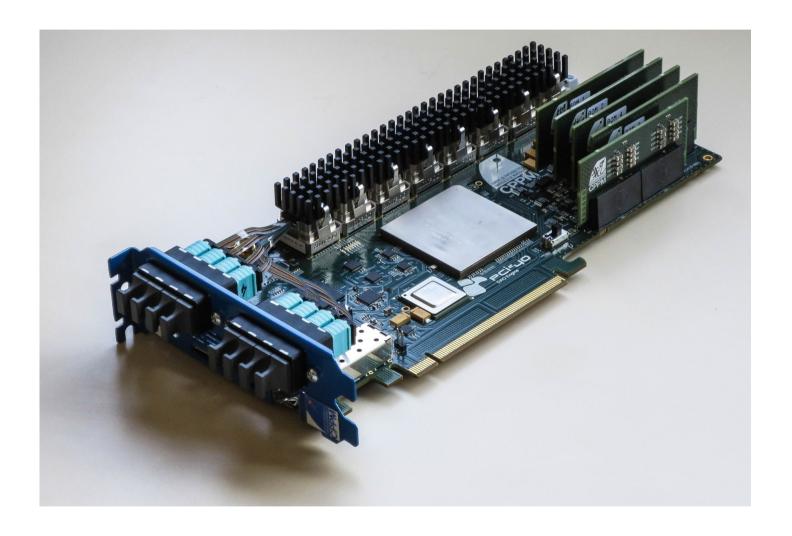

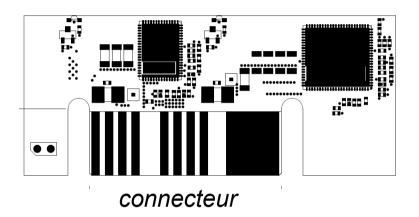

# **Prototypes PCIE40**

2 prototypes réalisés: Equipés avec Arria10 ES1 & ES2

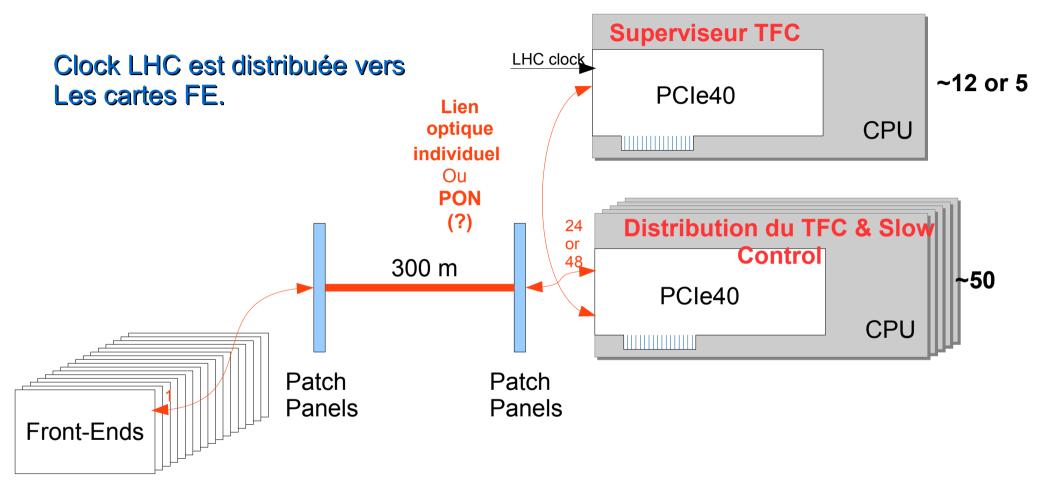

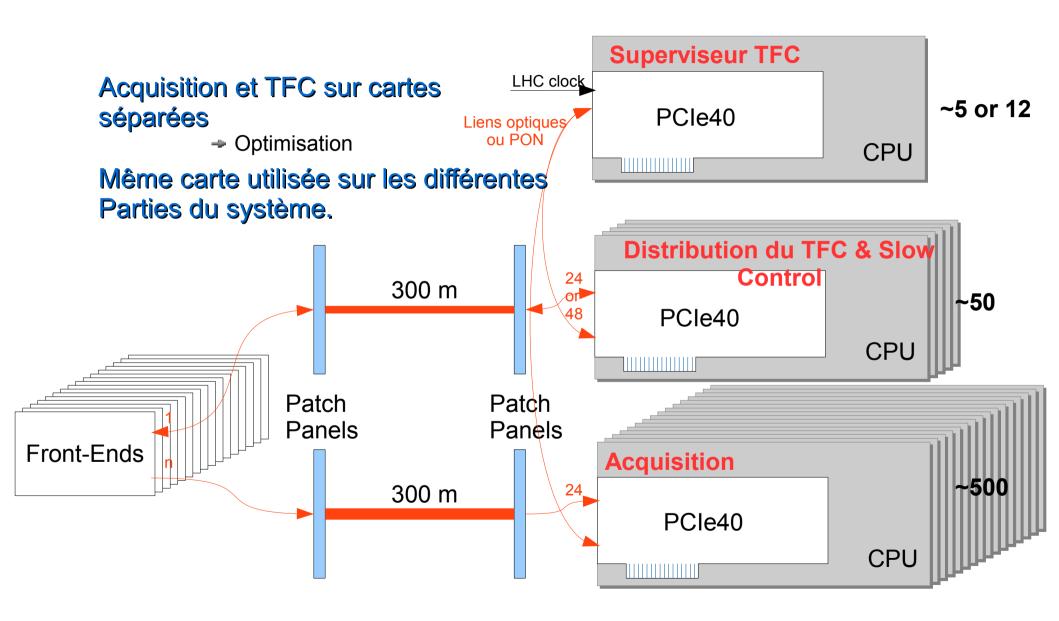

# **Architecture globale**

# **Architecture globale**

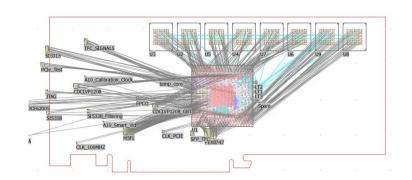

# **Conception CI**

### Challenge!

- 114 Liens séries rapides jusqu'à 10 Gbps incluant le PCI Express GEN3x16.

- Mise en œuvre d'un des plus gros FPGA ALTERA

- 1.15 million cells (Arria10 10AX115S4F45E3SG)

- Version "engineering sample" (ES1 & ES2)

- Carte pouvant dissiper jusqu'à 160W de puissance

- Mise en œuvre d'une dizaine de tensions différentes.

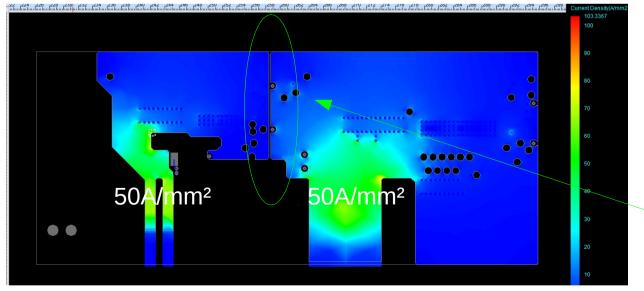

- Courants (50A/0.9V) pour le core du FPGA.

(Risque de délamination du Cl par effet thermique).

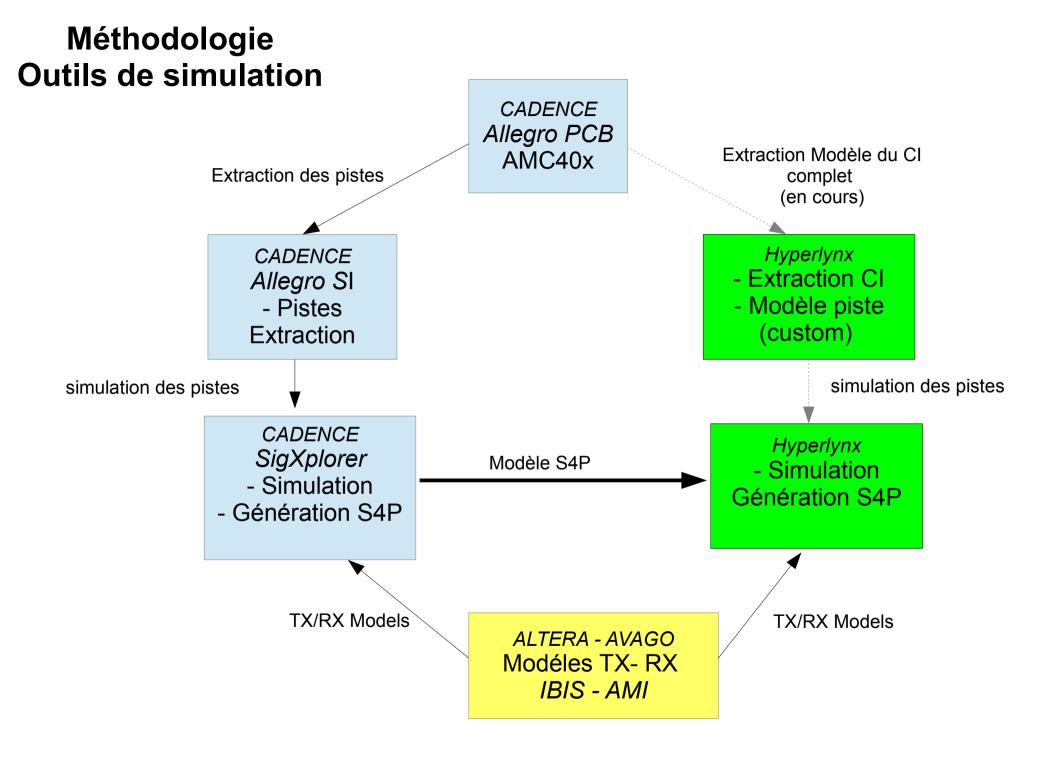

# **Conception CI - Outils**

### Schématique:

> Allegro Design + FSP (FPGA System Planner).

### Conception CI - Simulation:

- Liens rapides

- SigXplorer, Sigrity (System Serial Link), Hyperlinx, JNEye.

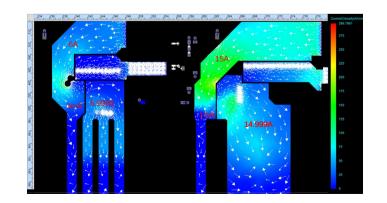

- Distribution de puissance

- Sigrity (Power Integrity):

- Identifier les points chauds (pannes!)

- Répartition du courant dans les plans.

- Évaluer les pertes en tension.

- → Évaluer la qualité de la dissipation thermique.

- Découplage des alimentations Sigrity

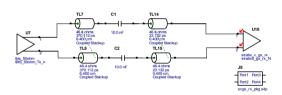

# Conception CI - Risque panne

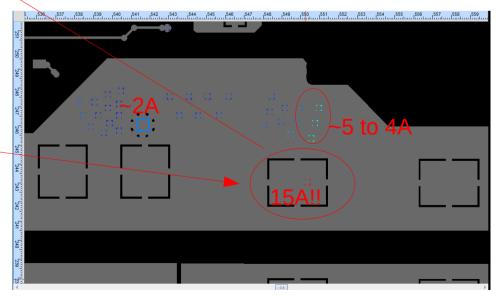

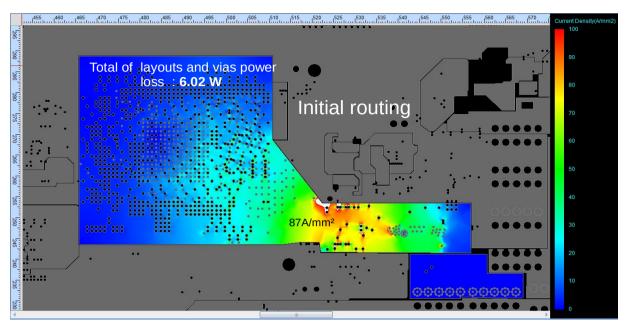

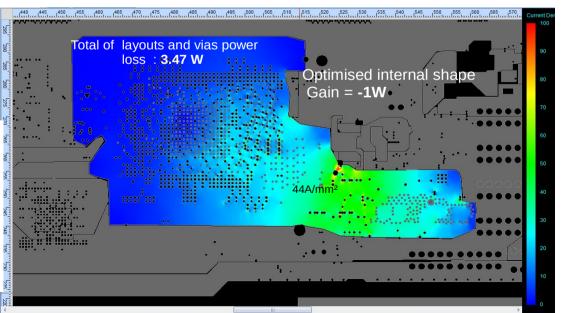

#### **Carte alimentation PCIE40**

Routage initial

Routage Final

Très haute densité de courant À travers les pins du Connecteur (150A/mm²)

Solution: Mettre 2 plans de Masse séparés

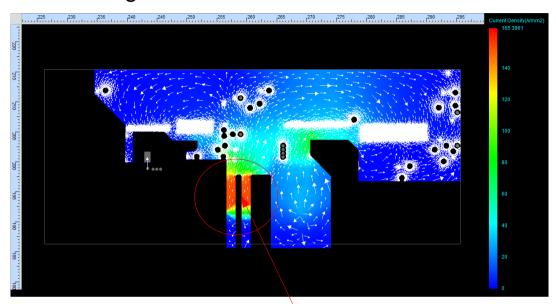

# Conception CI - Risque panne

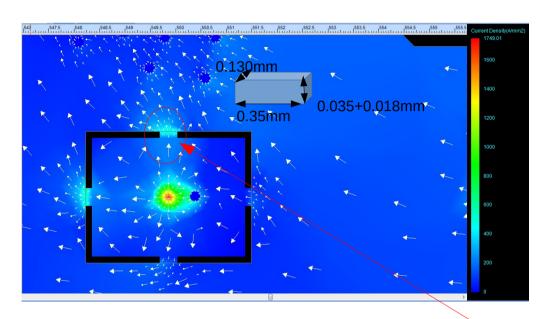

- Détection des points chauds& Effet Fusible possible

- Evaluation de la chute de Tension à travers les couches & Vias.

$30A => 450A/mm^2$

=> 8.34A!! risque d'effet fusible si >7.5A

#### **Problèmes:**

Via stressées 15A!

Forte densité de courant sur freins thermiques

## Conception CI Optimisation

### - Amélioration du design

- Éliminer points chauds

- Réduire les pertes & échauffement du PCB.

### 60A/0.9V FPGA - Core

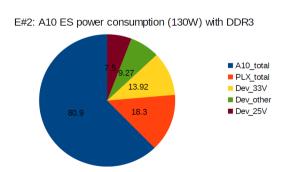

Power consumtion estimation 100 % logic cells, 50 % toggle rate, 250 MHz operation ES chip

# Conception CI Partie Thermique

Exemple de simulation (60A/0.9V)

- Échauffement du CI sous le FPGA

- Dimensionnement du radiateur

## PCIe40 Résultats - Thermique

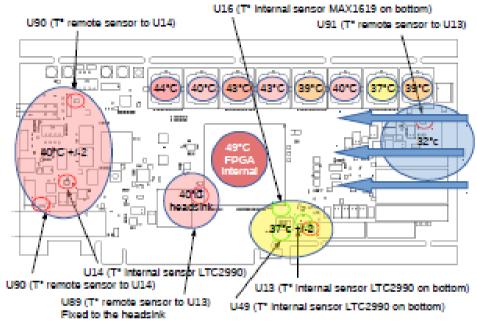

#### PCle 40 Temperature sensors location

100 -Custom heat sink nternal A10 Temperature Arria 10 ES2 **PRELIMINARY** 60 40 Mesure de T° en fonction de la FAN 25% Puissance consommée par le FPGA & ← FAN 50% La vitesse de ventilateurs 20 FAN 75% FAN 100% 0 20 40 60 80 100 A10 Power [W]

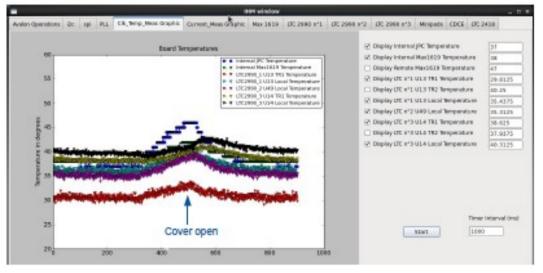

- Mesure de la T° en différent point de la carte.

- Mesure des tensions et courants.

- => Bonne connaissance de la température de La carte en fonctionnement.

- => Dimensionnement du radiateur fonction De la capacité de refroidissement dans le serveur

Mesures de T° en différent Point de la carte fonction du Temps.

# **PCIe40 Solutions Thermiques**

- Test en cours avec différents types de radiateur

- Radiateur standard avec un ventilateur

- Radiateur passif custom

- · Système de refroidissement liquide

- Choix de la solution finale après des tests plus approfondis

Radiateur avec ventilateur

Radiateur passif custom

Radiateur avec refroidissement liquide

### Conclusion

Le concept de la PCle40 devient le système de lecture de l'expérience LHCb.

2 cartes PCle40 (ES1 & ES2) sont actuellement complètement opérationnelles

19 cartes sont en préparation de câblage (Livraison FPGA) -

► Nouvelle version (PCle40v1a) avec ES3 en câblage actuellement!

La conception d'une carte comme la PCle40 est un challenge, de nombreux outils de simulation sont nécessaires pour mener à bien ce type de réalisation.

Échéance: Production de ~ 500 cartes PCle40 pour 2017/2018

# Extra slides

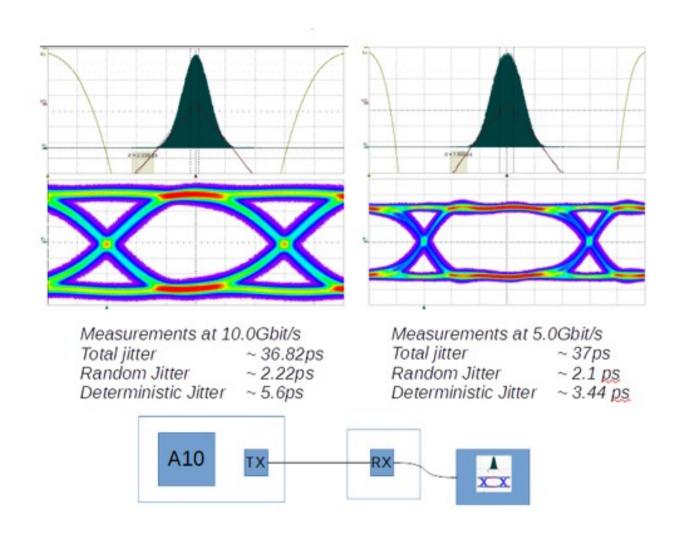

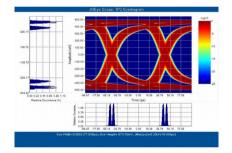

# PCle40 Liens rapides – Diagrammes de l'œil