F. Crescioli for the AMchip Team

IPHC Strasbourg - 01-06-2016

### Outline

Introduction to the Associative Memory

▲□▶ ▲□▶ ▲ □▶ ▲ □▶ ▲ □ ● ● ● ●

- Design approach

- Remarks on the flow

- Conclusions

### Associative Memory

- The Associative Memory is an original computing device first conceived for realtime reconstruction of the trajectories of charged particles (tracking) at the CDF experiment of the hadron collider Tevatron

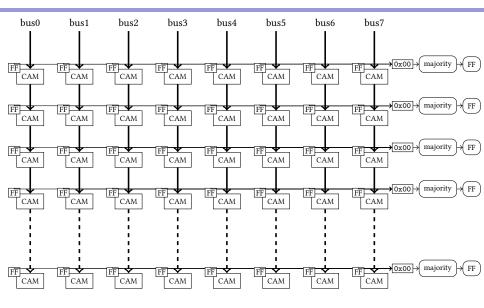

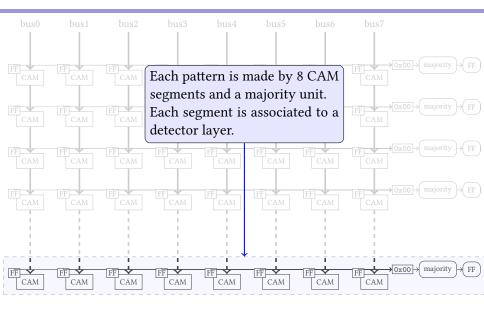

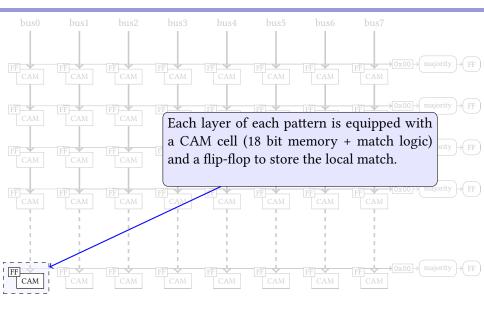

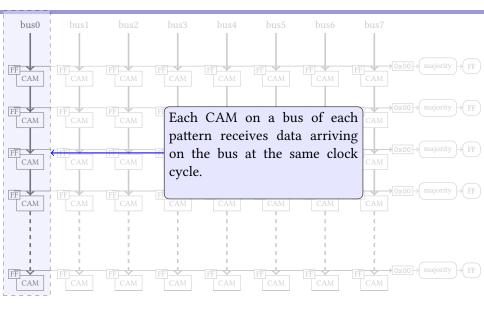

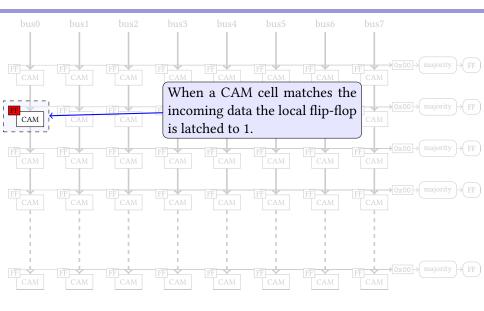

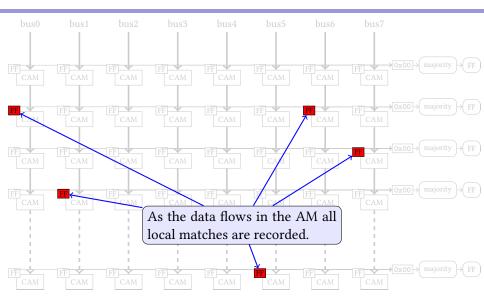

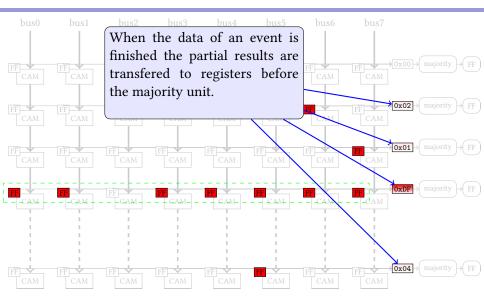

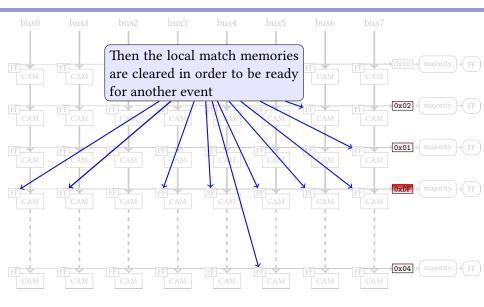

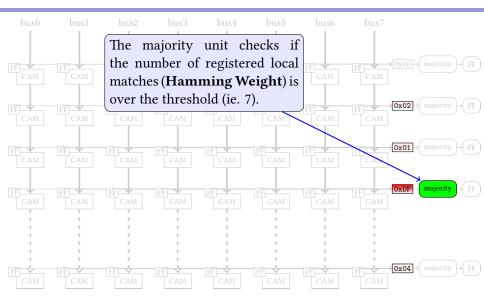

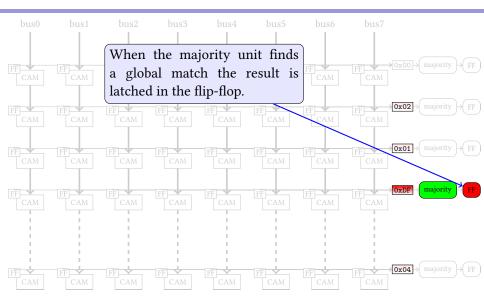

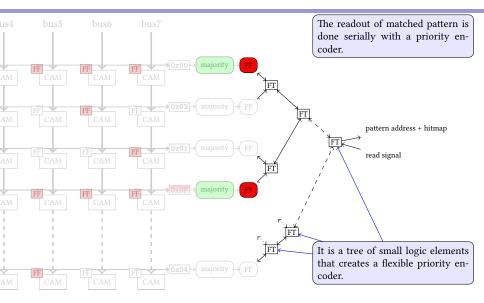

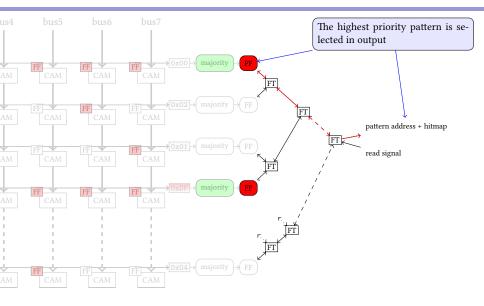

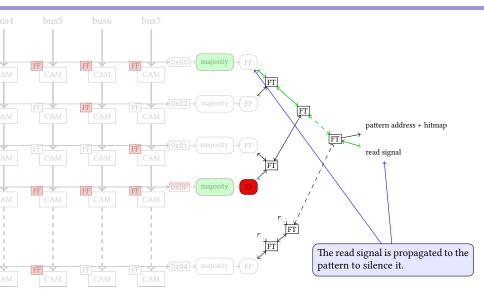

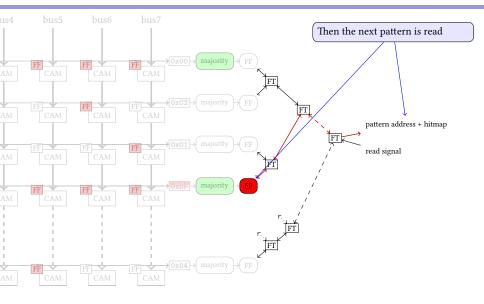

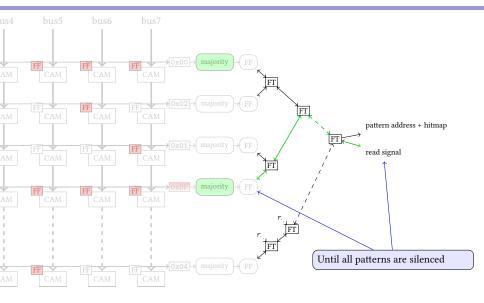

- The Associative Memory finds all matches between all combinations of input data and a pre-loaded database of patterns. It is a combinatorial pattern recognition engine.

- The AMchip, the ASIC that implements the Associative Memory function, is currently at the AMchip06 version (TSMC 65 nm) developed for ATLAS FTK

- AMchip06 has been developed by INFN (Milano, Frascati, Pisa) and LPNHE (Paris)

# Design Approach

#### —Design approach

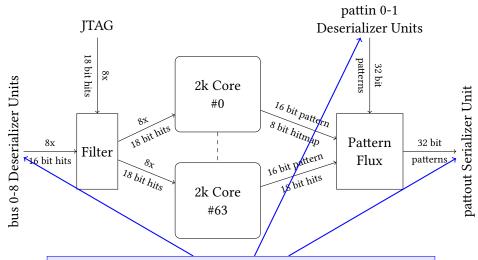

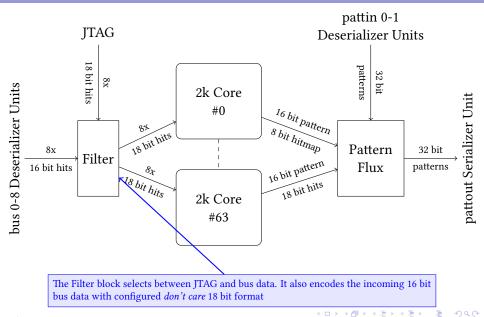

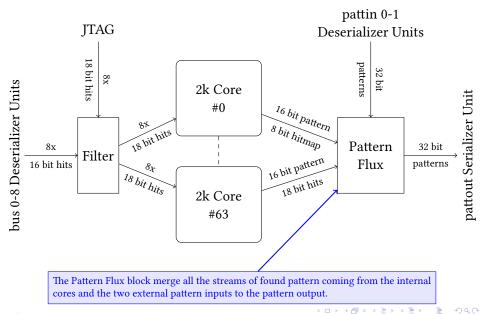

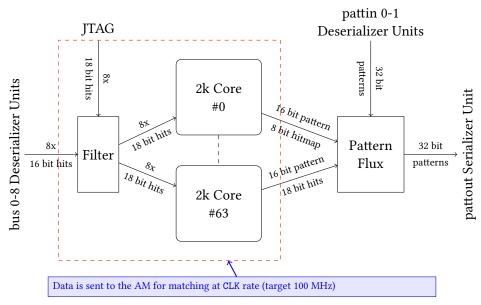

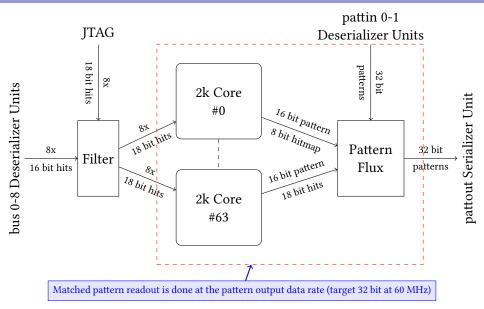

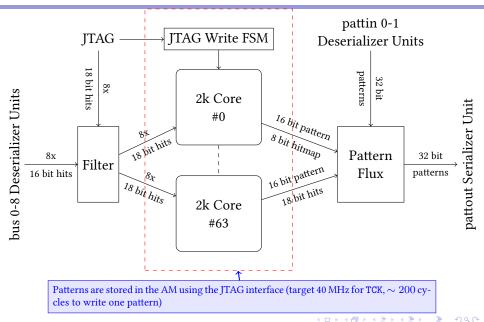

The Serializer and Deserializer units are interfaces between the serial link Hard IPs, 8b/10b decoders, data stream decoders and the main AM logic. Each Hard IP produces its own clock and a FIFO is used to cross to the main clock domains.

# Remarks on the flow

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ のへぐ

### Flow

- Based on Foundation Flow from Cadence

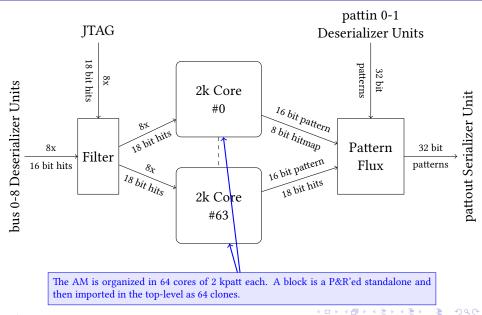

- ▶ NOT a partitioned/hierarchical flow, but two "nested" flat flows

- 2k block

- Top level with 64x cloned 2k blocks

- Full flow up to (not closed) signoff took about 24h on at least

64 Gb RAM machine

- Final signoff timing closure optimizations were very hard to perform

▲□▶▲□▶▲□▶▲□▶ □ のQで

- Many iterations Tempus to Encounter

- ► Need to run on >128 Gb RAM

### AMchip06

### AMchip06 specs

| Technology    | TSMC 65 nm           |

|---------------|----------------------|

| Area          | $\sim 168 \rm{mm}^2$ |

| Patterns      | 131072               |

| Inputs (hit)  | 8x max 2 gbps        |

| Inputs (patt) | 2x max 2.4 gbps      |

| Output (patt) | 1x max 2.4 gbps      |

| Core voltage  | 1 V to 1.2 V         |

| Main clock    | 100 MHz              |

### Conclusions

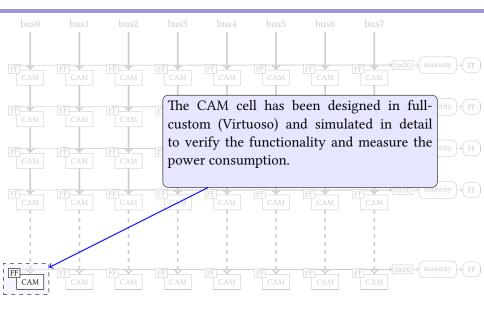

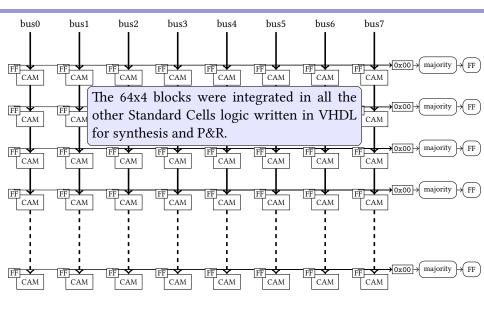

- ► The mixed full-custom / standard cells approach proved again to be very effective in designing large area and complex chips with area/power optimization

- ▶ We used it since AMchip04, our first 65 nm prototype

- $\blacktriangleright \sim 168~{\rm mm}^2$  proved to be very hard to handle especially at signoff timing closure

- We lost a lot of time before gathering enough computing resources to complete the final step

- The chip works withing specifications and we are finding 84% yield for zero-defect chips (preliminary)

- ▶ We are going to use it soon in FTK!

- Many thanks to all the supporting institutions

- Many thanks to the microelectronics experts from CERN and the many reviews, it was a precious input!