Institut de recherche sur les lois fondamentales de l'Univers Institute of Research into the Fundamental Laws of the Universe

# OWB-1: ADC 13-bits 32 voies pour les applications spatiales

# Florent Bouyjou

### Contexte

# Ce que nous avons fait à l'IRFU

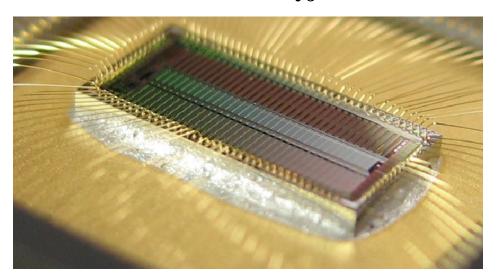

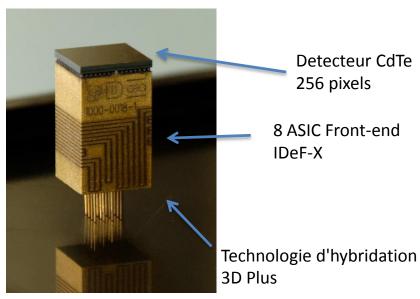

#### Camera gamma Caliste:

- Densité très élevée de pixels (600 μm)

- Très haute résolution spectrale (<1 keV at 60 keV)</li>

- Très faible consommation (800 μW/voie)

- Qualifiée spatiale

# **Etapes suivantes**

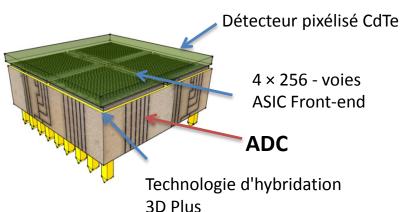

### Nouvelle micro caméra Gamma <u>numérique</u> :

#### Concevoir un ADC flexible:

Adaptés à chaque type d'architecture d'ASIC Front-end :

- Utilisable dans l'environnement spatial

- Haute résolution (typiquement 13 bits)

- Très bonnes performances en linéarité

- Faible consommation (<5mW / voie)</li>

- Temps de conversion 1-10µs max

Nous avons choisi l'architecture Wilkinson

# Multi channel ADC Design

# Pourquoi utiliser un Wilkinson ADC?

- Haute résolution

- Haute linéarité

- Adaptable pour les architectures multi-canal

- Très mauvais en rapidité

À améliorer ?

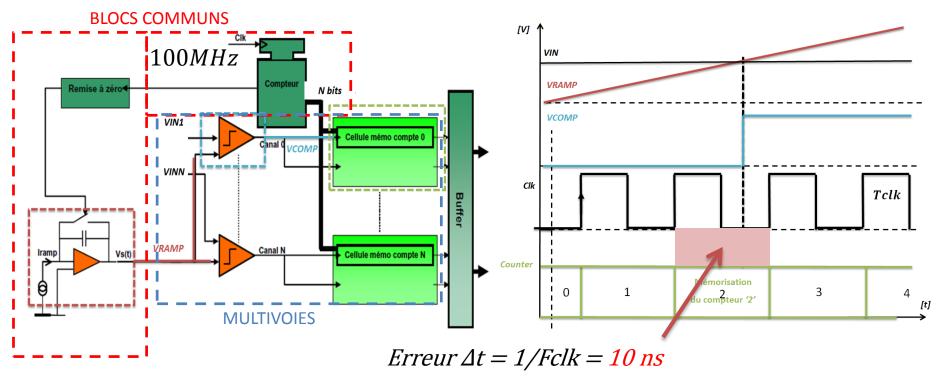

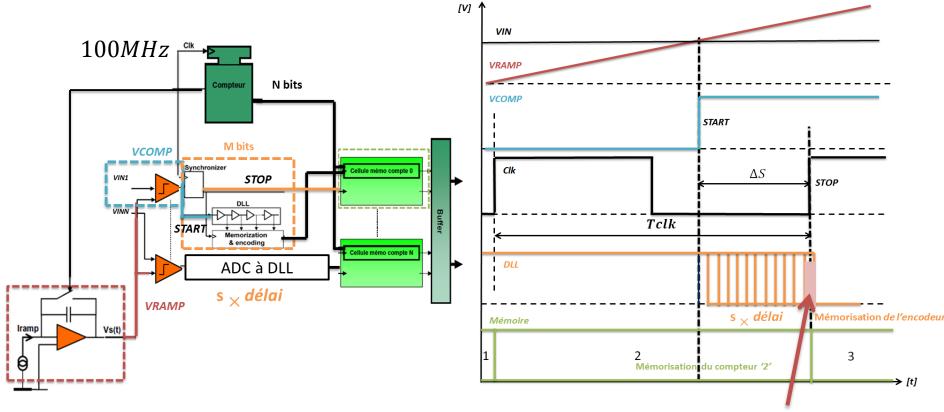

#### Architecture d'ADC Wilkinson + DLL

WILKY ASIC: 12-bit single ramp DLL ADC (4 channels) [1]

# Défis: Conception d'un nouveau ADC multi-canal pour applications spatiales

- 8 fois plus de canaux

- 13 bits au lieu de 12

- DC shifter en entrée

- Compensation de température automatique

- Durcicement au rayonnement par design

- Clock : PLL x 100 [100 MHz]

[1] Delagnes, E.; Breton, D.; Lugiez, F.; Rahmanifard, R., "A Low Power Multi-Channel Single Ramp ADC With Up to 3.2 GHz Virtual Clock," in *Nuclear Science, IEEE Transactions*, Oct. 2007

# L'ADC à intégration

Wilkinson à simple rampe : Pour mesurer un temps sur une plage de 2, 56 μs

Plus de précision = augmenter Fclk ...

$Tconversion \times Fclk = 2,56 \,\mu s \times 100 \,MHz = 256 \,soit \, 8 \,bits$

# L'ADC à intégration + DLL

**DLL (Delay-locked loop)**

<u>Wilkinson à simple rampe + DLL</u>: Pour mesurer un temps sur une plage de  $2,56 \mu s$

$Tconversion \times F_{DLL} = 2,56 \ \mu s \times 3,2 \text{GHz} = 8192 \text{ soit } 13 \text{ bits}$

Wilkinson → Wilkinson + DLL

8 bits → 13 bits : 32 x plus précis!

Erreur  $\Delta t = 1/FDLL$ = 312,5 ps

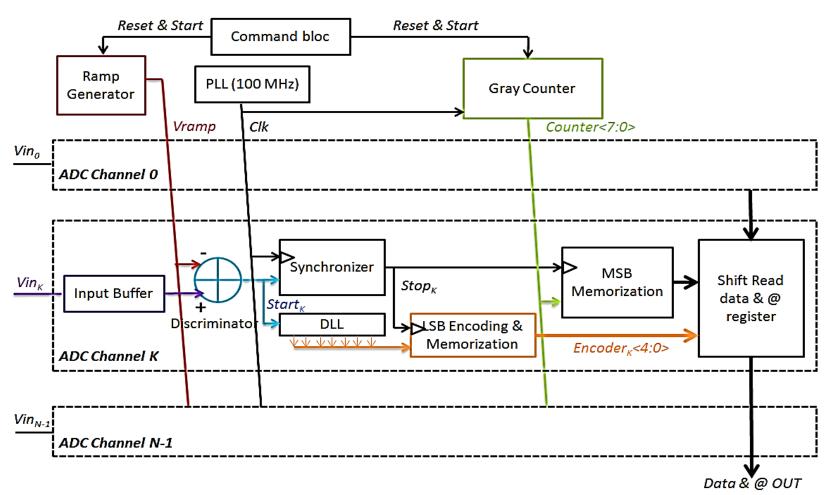

# Architecture d'OWB-1

• Pour gagner 1 bit : optimisation du discri et du générateur de rampe

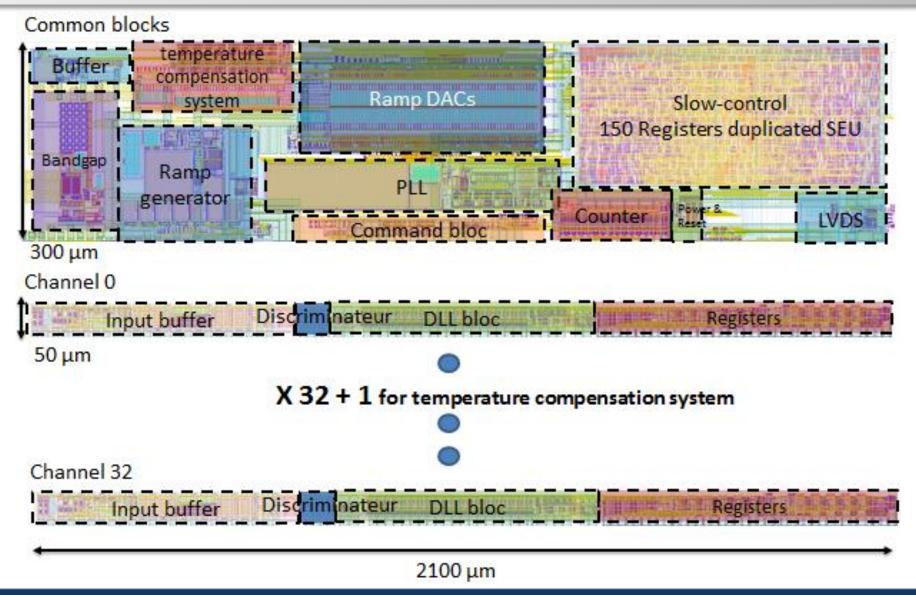

# **OWB-1 Layout**

# **OWB-1**: Caractéristiques principales

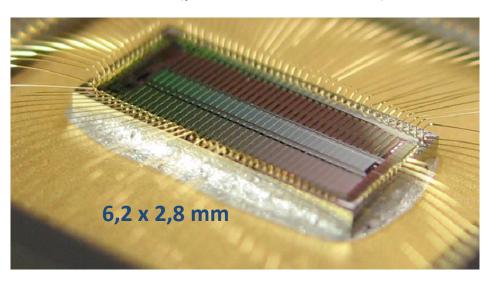

#### ASIC OWB-1: ADC 13-bits 32 voies

Technologie : CMOS AMS 0.35 μm Dimension d'une voie : 50 \*2000 μm

Surface totale: 18 mm<sup>2</sup>

RHBD : Radiation hardened by design Consommation : < 1mW / channel Consommation totale : 36,6 mW

Vitesse: 370 kHz (pour 32 conversions //)

#### Slow-control

SPI: 150 registres

#### **Configuration modes**

Data read: // and serial

Alim-on or off

Mask channel

Asjustable Ramp: DAC

Adjustable ADC resolusion: 13 to 10 bits

Input DC shifter

Temperature compensation system

PLL (1MHz->100MHz)

•••

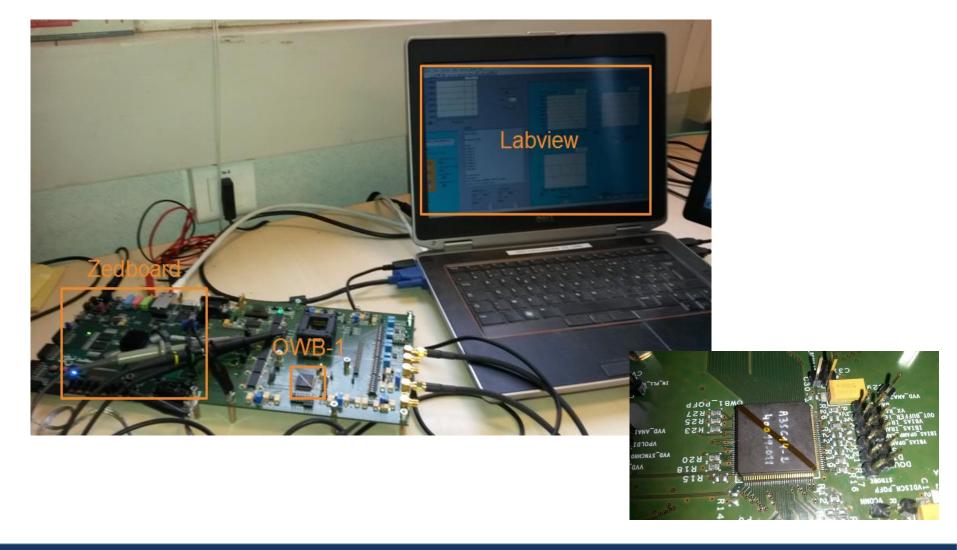

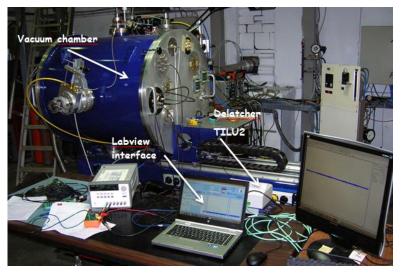

# Banc de test d'OWB-1

# Modes d'entrées : Plusieurs configurations possibles

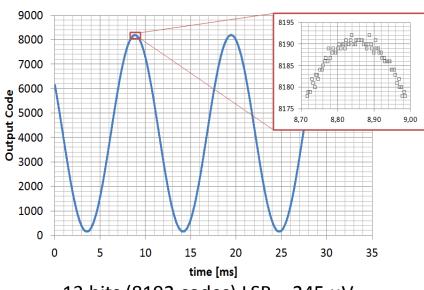

### 1 – Mode direct

Conversion « single shot »avec un sinus de 2V à 100 Hz sur l'entrée d'une voie de l'ADC :

13 bits (8192 codes) LSB = 245  $\mu$ V

#### L'ADC fonctionne correctement :

- Tous les voies sont fonctionnelles

- Les configurations du Slow-control fonctionnent

- Aucun code manquant

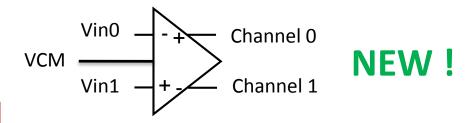

# 2 – Mode avec décalage DC

Vin peut être décalée grâce à une tension de mode commun interne programme (VCM)

# 3 - Mode différentiel

Vin est injectée dans les 2 canaux adjacents et peut être décalé grâce à tension de mode commun

# 4 - Mode inverseur

Vin est inversé et peut être décalée grâce À une tension de mode commun

# Performances en linéarité de l'ADC

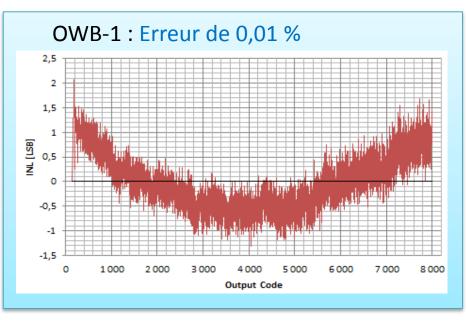

# **INL: Integral Non Linearity**

# **DNL: Differential Non Linearity**

Mesure: 512 acquisitions / pas de 16 bits du DAC en entrée :

$$INL = +2,1 \text{ à } -1,3 \text{ LSB}$$

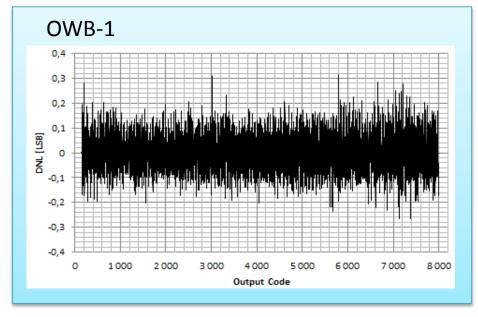

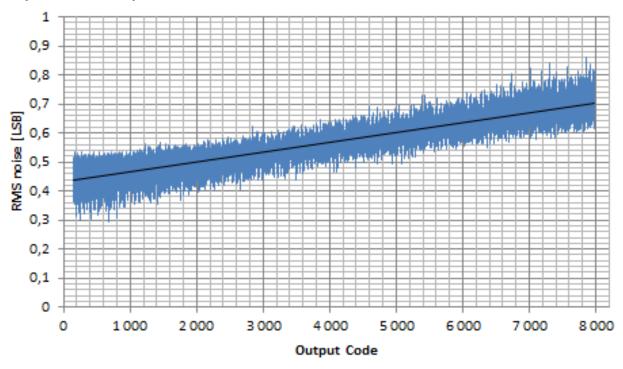

# Performances en bruit de l'ADC

### **Bruit RMS**

Mesure: 512 acquisitions / pas de 16 bits du DAC en entrée :

Bruit rms = 0,3 à 0,9 LSB

#### Les sources de bruit dominantes:

- La source de courant du générateur de rampe

- Le jitter du discriminateur

# Readout modes and sampling rate

Data transfer: pipeline

convert:

Coding Data<1:32>

Coding Data<33:64>

Read:

Data transfer Data<1:32>

Data transfer Data<33:64>

2.7µs

Conversion time for 32 channels : Scalable nbr of bits : 2,7  $\mu$ s (13 bits), 1,42  $\mu$ s (12 bits), 0,78  $\mu$ s (11 bits)

# 2 readout modes

|                                                                                 |                                                                       | Parallel mode |          | Serial mode                                                              |             |          |  |  |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|----------|--------------------------------------------------------------------------|-------------|----------|--|--|--|

| Conversion time                                                                 | 5,26 μs (14-bit)                                                      |               |          |                                                                          |             |          |  |  |  |

|                                                                                 | 2,7 μs (13-bit)                                                       |               |          |                                                                          |             |          |  |  |  |

|                                                                                 | 1,42 μs (12-bit)                                                      |               |          |                                                                          |             |          |  |  |  |

|                                                                                 | 0,78 μs (11-bit)                                                      |               |          |                                                                          |             |          |  |  |  |

| Data read time                                                                  | $(2 \times X + 2 \text{ (start and end of frame)) / }$<br>$CLK\_READ$ |               |          | $(2 \times X + 2 \text{ (start and end of frame)}) \times 12 / CLK_READ$ |             |          |  |  |  |

| Sampling rate [kHz]<br>(CLK_READ = 100<br>MHz and for 32<br>channels activated) | Bits                                                                  | No Pipeline   | Pipeline | Bits                                                                     | No Pipeline | Pipeline |  |  |  |

|                                                                                 | 14                                                                    | 169           | 190      | 14                                                                       | 76          | 126      |  |  |  |

|                                                                                 | 13                                                                    | 297           | 370      | 13                                                                       | 94          |          |  |  |  |

|                                                                                 | 12                                                                    | 480           | 704      | 12                                                                       | 107         |          |  |  |  |

|                                                                                 | 11                                                                    | 694           | 1282     | 11                                                                       | 115         |          |  |  |  |

# **SEL (Single Event Latchup)**

# Linear energy transfer (*LET*)

Test avec des ions lourds à Louvain en septembre 2015

|        | lon LET<br>(MeV.cm²/mg) | Fluence<br>(part/cm²) | Tilt (°) | Eff LET<br>(MeV.cm²/mg) | Nb SEL | XS<br>(cm²) |

|--------|-------------------------|-----------------------|----------|-------------------------|--------|-------------|

| Chip 1 | Xe 62,5                 | 1E7                   | 0        | 62,5                    | 0      | 1E-7        |

| Chip 2 | Xe 62,5                 | 1E7                   | 0        | 62,5                    | 0      | 1E-7        |

# LET > 62.5 MeV.cm<sup>2</sup>.mg<sup>-1</sup>

# Test d'endurance

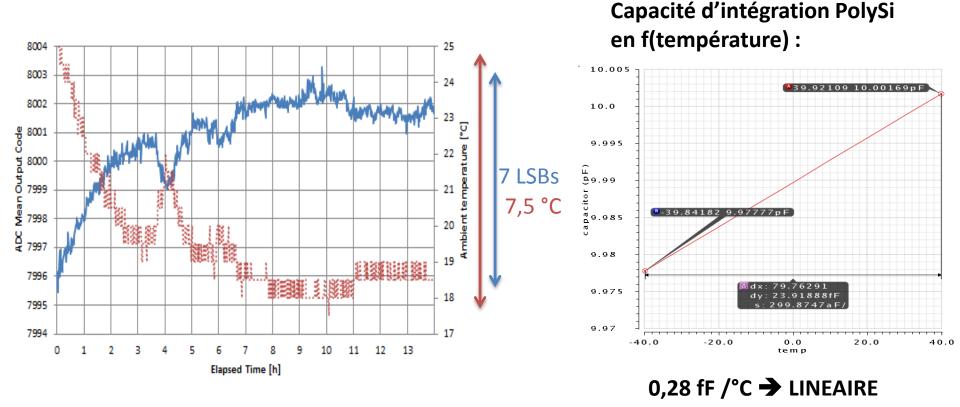

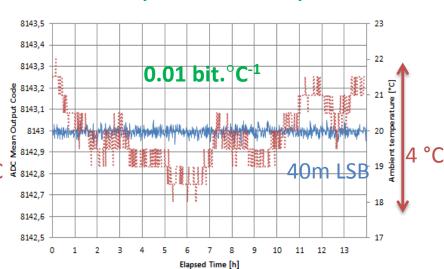

**Aquisition du code de l'ADC**: moyenne de 512 acquisitions toutes les minutes pendant 14 heures en haut de plage VIN = 1,9 V en fonction du temps et de la température

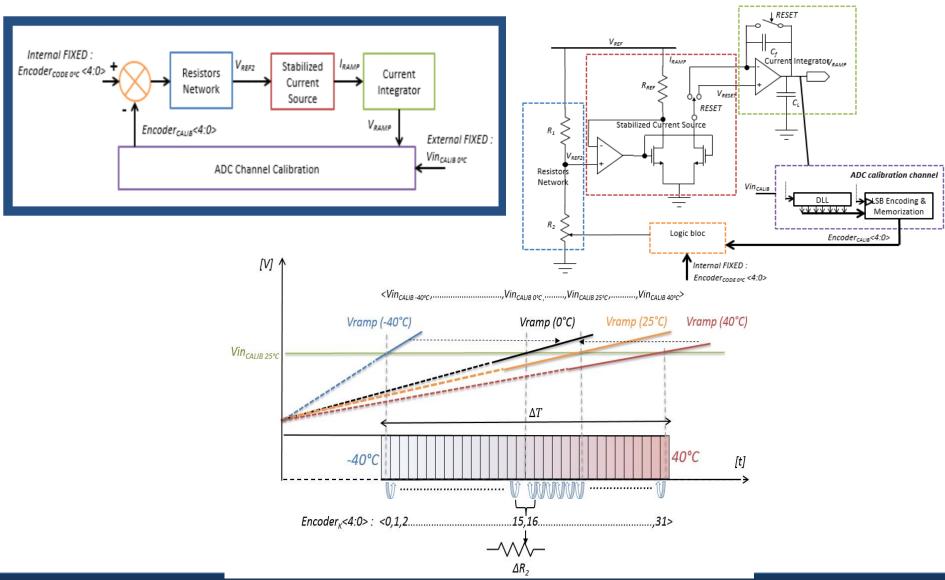

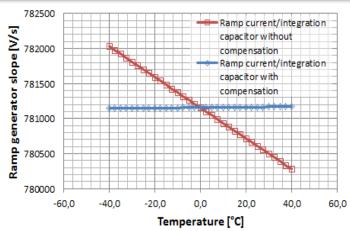

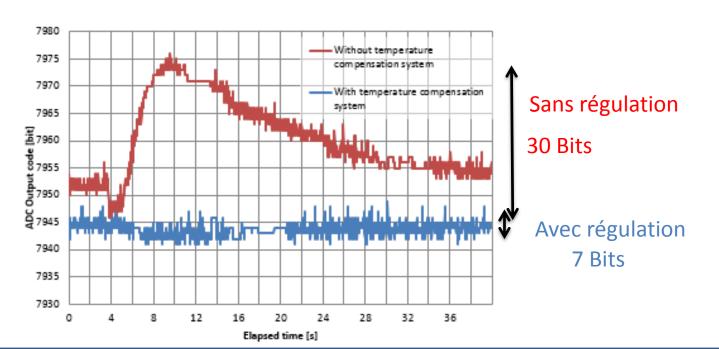

# Système d'auto-compensation en température intégré

# Système d'auto-compensation en température intégré

## Sensibilité en température :

- Sans système d'auto-compensation

- Avec système d'auto-compensation

**Mesure du code de l'ADC**: moyenne de 512 acquisitions toutes les minutes pendant 14 heures en haut de plage VIN = 1,9 V en fonction du temps et de la température

Sans auto-compensation en température :

#### 8004 8002 8002 8000 7999 7998 7997 7996 7996 7997 7996 7997 7996 7999 0 1 2 3 4 5 6 7 8 9 10 11 12 13 Elapsed Time [h]

#### Avec auto-compensation en température :

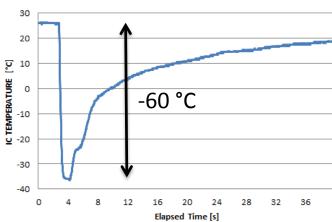

# Système d'auto-compensation en température intégré

Changement rapide en température

# Conclusion

### **OWB-1** PERFORMANCES MEASURED

OWB-1: ADC 13 bits 32 canaux // de faible consommation à haute linéarité en techno AMS  $0.35 \mu m$

- Liaison SPI pour le slowcontrol avec un power & reset

- Buffer d'entrée avec une adaptation DC programmable

- Une option Alim-on: chaque canal peut être désactivé pour réduire la consommation

- Une PLL avec un faible jitter pour éviter d'injecter une fréquence élevée externe.

- Données peuvent sortir en LVDS ou CMOS

- Système d'auto-compensation en température intégré

- Durci au Latchup

- Faible consommation

#### SUITE

Test avec un ASIC front-end et un detecteur

# Merci pour votre attention