## STEREO electronics overview

JL. Bouly, G. Bosson, O. Bourrion, J. Bouvier, C. Li, N. Ponchant, D. Tourres, C. Vescovi

CNRS-IN2P3-LPSC Grenoble

1er Juin 2016

- Overview

- General requirements

- Electronics overview

- First level triggering and processing

- 2 Front-end description

- Specifications

- Hardware

- Firmware

- FE8 ↔ TRB communication

- 3 Trigger and readout description

- Hardware

- Firmware

- 4 LED board

- Hardware

- Firmware

## General requirements

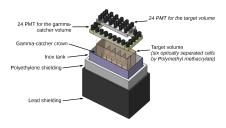

- Monitor 68 channels required in 3 classes (for triggering)

- 24 PMT for Gamma catcher

- 24 PMT for target (gadolinium-loaded liquid scintillator)

- 20 PMT for muon veto (Cerenkov detector)

- Withstand a mean trigger rate of 1 kHz

- Have no dead-time (pile-up excepted)

- Manage various trigger schemes and conditions (coincidence and anti-coincidence)

- $\bullet$  Process signals on board: compute  $Q_{\rm tot}$  and  $Q_{\rm tail}$  for Pulse Shape discrimination (PSD)

## Electronics overview

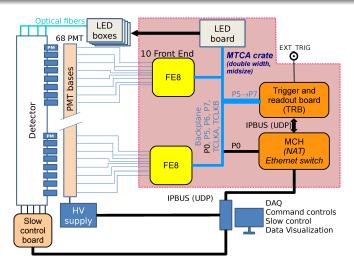

- Trigger board (TRB) for: triggering, FE readout and LED control

- $\bullet \ \, \text{Communication FE} \leftrightarrow \text{Trig Board with custom protocol} \\$

- Readout and slow control via IPBus (Secured UDP from CERN)

# First level triggering (T1) and processing

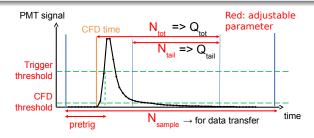

- FE emits a trigger when at least one PMT signal > trig threshold

- Confirmed trigger (T1a) reception initiate PSD processing

- Beginning of signal is to be found with a Constant Fraction Discriminator (CFD) having its own threshold (above noise)

- Adjustable parameter defined prior to run

- $\bullet$   $N_{\rm tot}$  represents typical pulse duration

- $\bullet$   $N_{\rm sample}$  time window for analysis and samples to record in debug mode

- Overview

- General requirements

- Electronics overview

- First level triggering and processing

- 2 Front-end description

- Specifications

- Hardware

- Firmware

- FE8 ↔ TRB communication

- 3 Trigger and readout description

- Hardware

- Firmware

- 4 LED board

- Hardware

- Firmware

# Front-end 8 (FE8) specifications

- 8 channels board (13 bit ADC @250 MSPS, dynamic range 1.0 V)

- Preamplifier + amplifier with 2 selectable gains, e.g x1 and x20

- The ADC input feature anti-aliasing filter (80 MHz)

- Readout by custom serial protocol, slow control by IPBus

- First level trigger on amplitude **OR** charge, selectable by mask :

- Individual channel

- sum of first 4 channels

- sum of last 4 channels

- sum of 8 channels

- Trigger bit inserted in the data flow

- Each channel has a high pass IIR to suppress pedestal

- Scalers for individual PMT monitoring

- ullet CFD and PSD for each channel.  $Q_{\mathrm{tot}}$  and  $Q_{\mathrm{tail}}$  computed on board

- Transfer of  $Q_{\rm tot} \times 8$ ,  $Q_{\rm tail} \times 8$ , zero crossing  $\times 8$

- $\bullet$  Optional debug mode to readout the  $N_{\rm samples}$  used to compute CFD and PSD

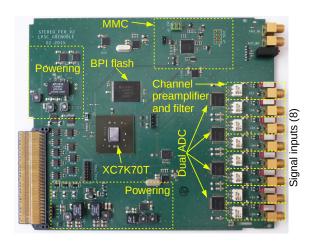

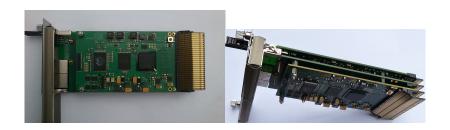

## FE8 hardware

- Main FPGA: XC7K70-2TFBG676,

- ullet ADC: Texas Instrument ADS42LB49 (AC coupled,  $f_{\rm c} > 30\,{\rm kHz})$

8/21

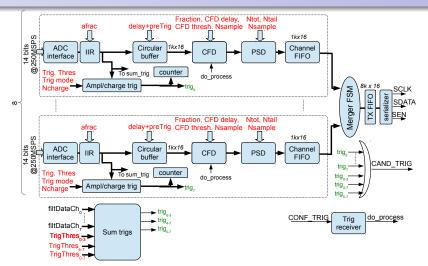

## FE8 firmware overview

Parameters are in red

Pipelined processing: 1<sup>st</sup> CFD, then PSD, then data concentrated and finally serialized

## FE8 ↔ TRB communication

Serial link operated at 125 Mbit/s, typical frame content: 4 words of 32 bit (mandatory) N<sub>samples</sub> words of 16 bit (optionnal)

Q<sub>tot</sub> ch0 Q<sub>tot</sub> ch0 Time offset ch0 Param ch0 smp<sub>0</sub> ch0 smp<sub>1</sub> ch0 .... smp<sub>Noampion 1</sub> ch0 Q<sub>tot</sub> ch1 Q<sub>tot</sub> ch1 Time offset ch1 Param ch1

### Average trigger rate limitation due to serial link

- In normal mode, rate limited at 125MHz/(4x32x8)=122 kHz.

- In debug mode, rate limited at 13.5 kHz (worst case, 64 samples).

- CFD time offset word contains:

- N\_ZC: relative offset of the CFD threshold crossing

- Y1, Y2: CFD values before and after threshold crossing

- Param word contains:

- ADC or IIR overflow: 1 bit

- Trigger source bit (channel, sum4, sum8): 3 bit mask

- Triggering path at 250 MHz (to be sample accurate)

- ⇒ Delay from candidate trigger to confirmed trigger, a **circular buffer** is required in the front-end (about 120 ns or 30 samples)

- Overview

- General requirements

- Electronics overview

- First level triggering and processing

- 2 Front-end description

- Specifications

- Hardware

- Firmware

- FE8 ↔ TRB communication

- 3 Trigger and readout description

- Hardware

- Firmware

- 4 LED board

- Hardware

- Firmware

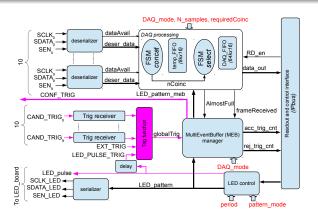

# Trigger and Readout Board (TRB)

#### NAT-MCH and extensions (2 boards)

- Tongue 1: NAT-MCH featuring an Ethernet switch.

- Tongue 2: Clock trees (FCLKA, TCLKA), clock reception (TCLKB)

- Tongue 3: Main board with FPGA (XC6SLX45T-FGG484), power, Ethernet (GTP and spare phy)

- Tongue 4: Fast SMA inputs, RJ45 (spare Ethernet, LED box control)

### TRB firmware

- MEB is implemented: up to 84 (normal)/6 (debug) consecutive triggers can be accepted (if separated by  $N_s$ amples  $\times$  4 ns)

- T1 trig function.

- T2: event selection in hardware (FSM\_select)

- 🤌 In calibration mode (LED) several pattern sequences are possible.

13 / 21

C. Vescovi STEREO electronics

# **Triggering**

#### T1 trigger

- For now OR of the trigger issued by the FE8.

- FE8 triggers can be individually masked.

- Accepted and rejected T1 are monitored (32 bit counters).

### T2 trigger

- Performed after T1 upon data reception in TRB.

- Event suppressed are not stored in DAQ\_FIFO.

- For now T2 on coincidence is implemented: event is kept if the number of CFD thresholds crossed is above a programmed value for the whole system.

- Not monitored.

# Typical readout frame

#### Common header:

- Word[0]: DATE LSB

- Word[1]: DATE MSB

- Word[2]: LED pattern

- Word[3]: T\_VETO

#### Details:

- DATE is produced by a 32-bit counter incremented every 4 ns, recorded at T1a.

- T\_VETO: time since previous veto trigger, resolution of 128 ns, 16-bit counter (max time 8.38 ms)

#### One channel data:

- Word[off+0]: Q\_tot LSB

- Word[off+1]: Q\_tot MSB

- Word[off+2]: Q\_tail LSB

- Word[off+3]: Q\_tail MSB

- Word[off+4]: CFD\_time LSB

- Word[off+5]: CFD\_time MSB

- Word[off+6]: Param word

- Word[off+7]: sample[0]

- Word[off+8]: sample[1]

- Word[off+...]: sample[i]

Trigger rate in normal mode above 1 kHz (related to the readout rate of the acquisition computer).

15 / 21

- Overview

- General requirements

- Electronics overview

- First level triggering and processing

- 2 Front-end description

- Specifications

- Hardware

- Firmware

- FE8 ↔ TRB communication

- Trigger and readout description

- Hardware

- Firmware

- 4 LED board

- Hardware

- Firmware

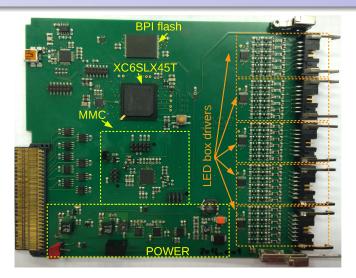

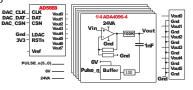

## LED board hardware

- Slow control by IPBus (for LED voltage level and BPI programming)

- LED pattern and timing are selected and driven by the trigger board.

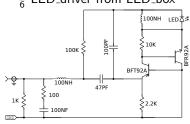

## LED box driver and led box

#### $\frac{1}{5}$ LED\_box\_driver from LED\_board

### $\frac{1}{6}$ LED\_driver from LED\_box

Courtesy from G. Bosson

- Each LED box contains 6 LED and a discrete LED driver.

- LED light driver supplied and driven via a single coax cable:

- LED light level set by mean voltage (DAC setting via IPBus)

- 2 Square pulse > 2 V fires the LED (generated by FPGA)

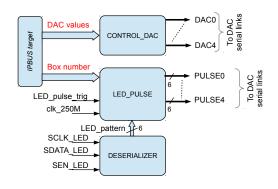

## LED board firmware

- Use IPBus to configure DAC and select the LED boxes to drive.

- Serial data frame is used to set the required pattern (for instance incremental pattern).

- After each serial frame, a led pulse trigger is sent by the trigger board to activate the LED pattern.

- Overview

- General requirements

- Electronics overview

- First level triggering and processing

- 2 Front-end description

- Specifications

- Hardware

- Firmware

- FE8 ↔ TRB communication

- 3 Trigger and readout description

- Hardware

- Firmware

- 4 LED board

- Hardware

- Firmware

- 5 Summary

## Summary

- FE8, LED\_board and TRB validated on prototype experiment.

- Spare boards available: 2 FE8, 1 LED\_board, 1 TRB

- Firmwares can be remotely updated, evolutions are possible, just ask.

More details can be found in arXiv:1510.08238