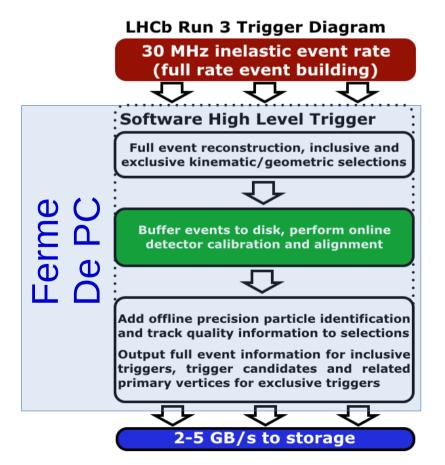

Nouvelle acquisition pour LHCb avec reconstruction de tous les évènements en ligne à 30MHz sans filtre

Pierre-Yves Duval (CPPM)

Au nom de la collaboration LHCb

## Sommaire

- 1) Nouvelles spécifications de performances

- 2) Composants de la chaîne d'acquisition

- 3)Les 3 flux d'informations DAQ, ECS, TFC

- 4)La nouvelle carte polyvalente PCIe40

- 5)L'Architecture d'assemblage d'événements

- 6)Outils de développement pour la collaboration

- 7)Outils logiciels pour la collaborations

- 8)Conclusions

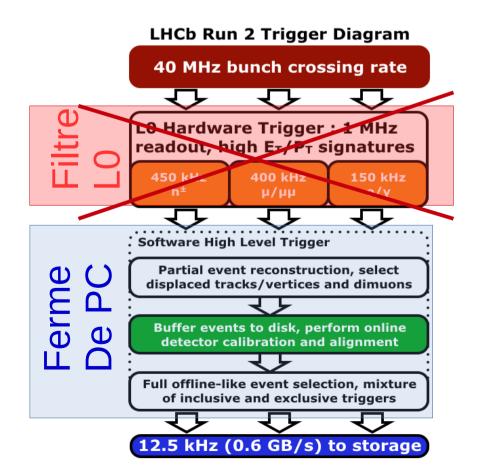

## Nouvelles spécifications

- 1) Acquérir les données de toutes les collisions à 30MHz (versus 1MHz)

- 2) Gérer un plus fort taux d'empilement (pile-up)

- 3) Augmenter la résolutions des détecteurs

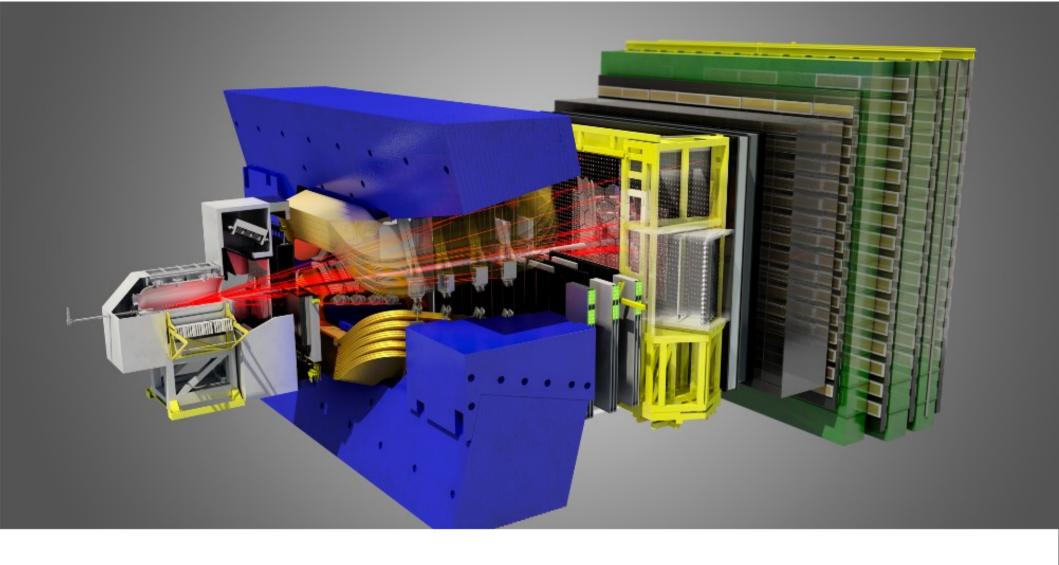

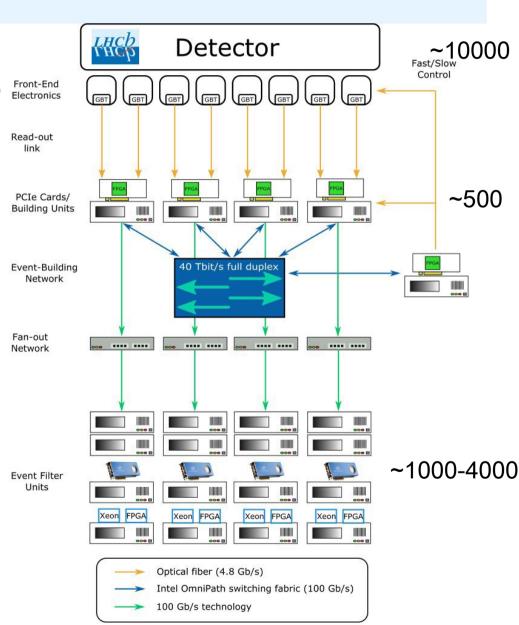

## Composants du DAQ

Plus de sélection hardware au niveau 0

La ferme doit traiter :

- Des évènements plus gros (~50KB à ~100KB)

- à une **fréquence plus élevée** (~1MHz à ~30MHz)

- Une grande bande passante de 40Tbit/s

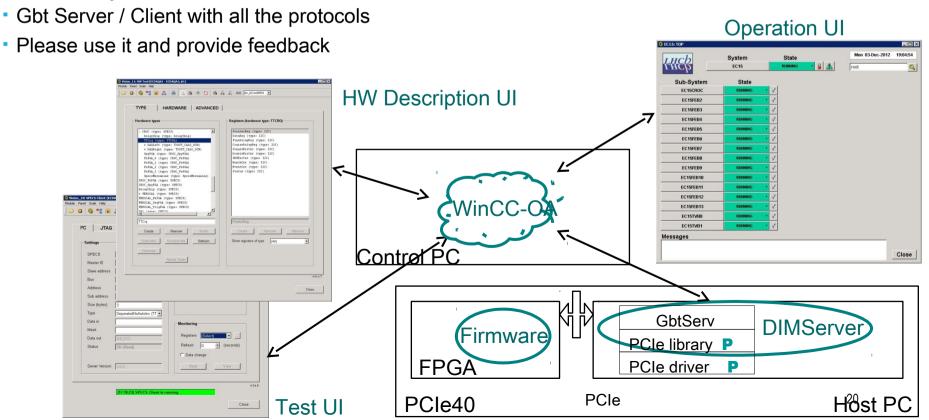

Configuration et contôle vie le sous système ECS (WINCCOA)

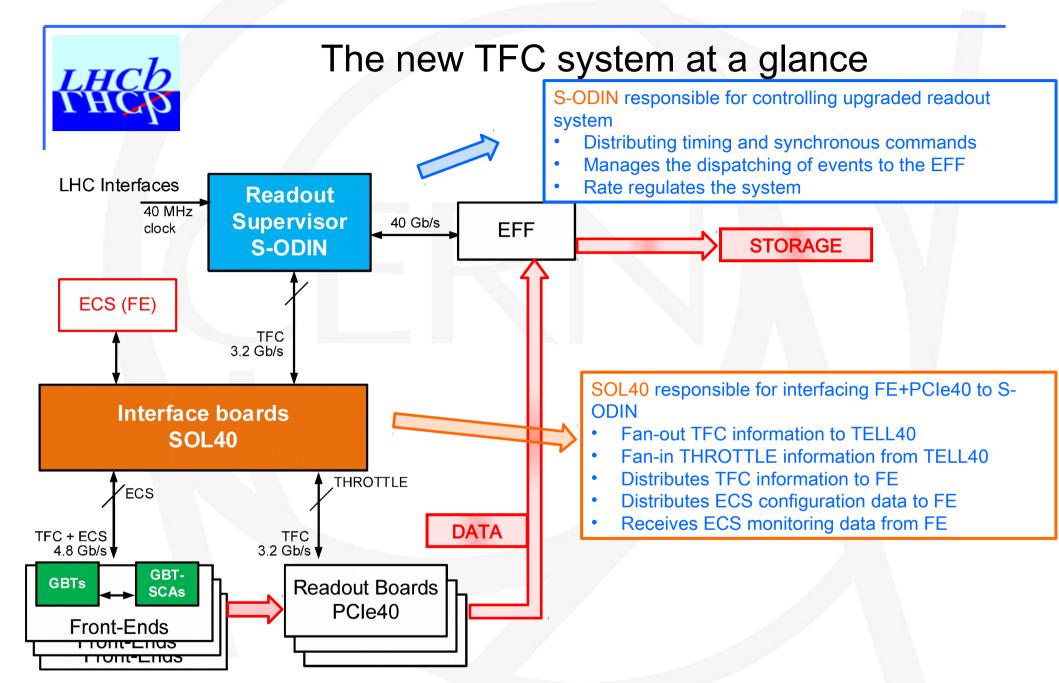

Synchronisation globale via le sous système TFC

(horloge, messages rapides de sync)

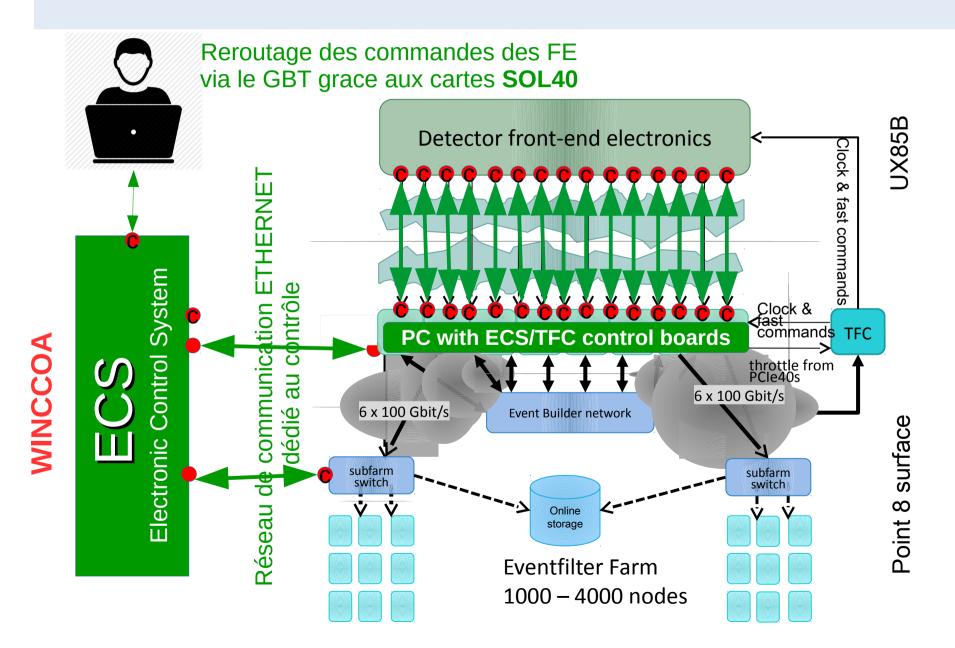

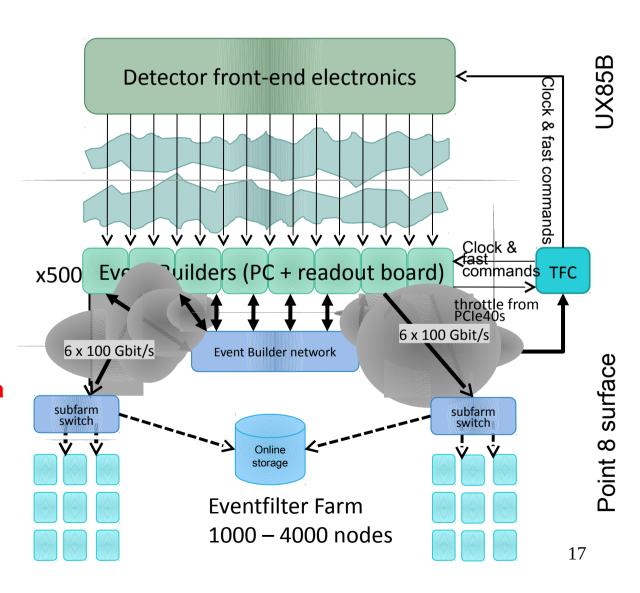

## Les trois flux DAQ, ECS, TFC

#### JX85B **GBT** Detector front-end electronics Protocole développé au CERN pour des liaisons Front-End à 4,8Gb/s. Clock & commands TFC Composants durcis x500 Eve uilders (PC + readout board) contre les radiations throttle from PCIe40s ibit/s 6 x 10 00 Gbit/s evenus ider networ Point 8 surface subfarm subfarm switch Online storage **Eventfilter Farm** 1000 – 4000 nodes

## Les trois flux DAQ, ECS, TFC

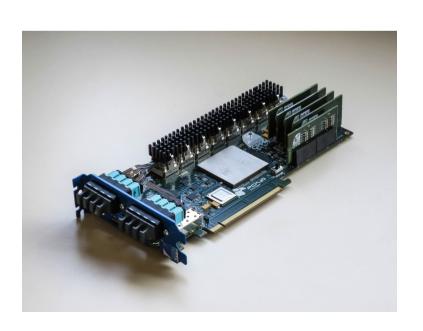

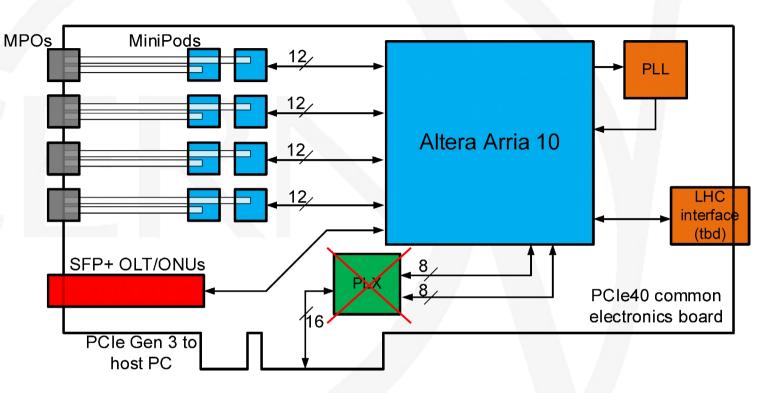

## La nouvelle carte polyvalente PCIe40

Besoin d'une carte avec beaucoup de liaisons et un timing très précis. Elle n'existe pas sur le marché.

- → Carte PCIe Gen3X16 (125Gbits/s)

- → 48 GBT bidirectionels sur 96 liens et 1 SFP+

- → FPGA ALTERA ARIA X

- → Moteur DMA à 100Gb/s

## La nouvelle carte polyvalente PCIe40

## Le firmware chargé définit la fonction :

- Nœud du sous-système DAQ (TELL40)

- Nœud de contrôle su sous-système ECS pour les Front End (SOL40)

- Noeud du sous-système TFC (SOL40)

## Collaboration fructueuse entre CERN, CPPM, LAPP :

- Hardware (CPPM)

- Firmware (LAPP coordination), CERN, CPPM

- Chaque groupe de détecteur y intègre son format de données et ses traitements propres

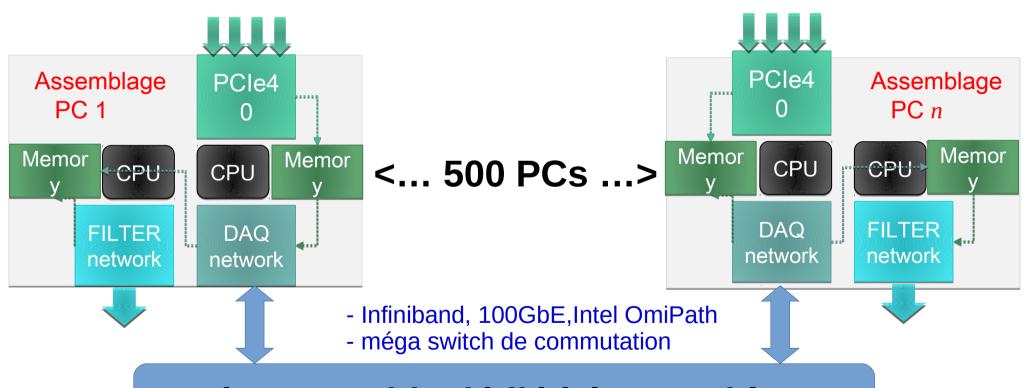

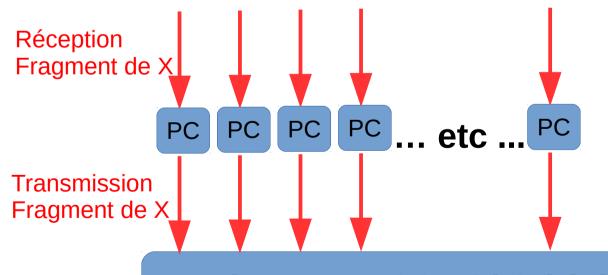

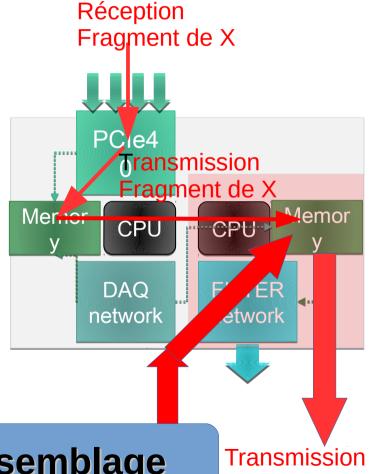

# L'architecture d'assemblage des événements

Chaque PC d'assemblage est à la fois:

- collecteur/distributeur de fragments

- assembleur/constructeur d'événement

Réseau rapide dédié à l'assemblage

# L'architecture d'assemblage des événements

#### 400 Gb/s de bande passante totale

PC assembleur de l'événement X

- 100Gb/s réception PCIe

- 100Gb/s envoi des fragments sur le réseau assemblage

- 100Gb/s réception sur le réseau d'assemblage

- 100Gb/s envoi de l'événement assemblé à la ferme

Mesuré 111.5 Gb/s sur le PCIe entre FPGA et mémoire

événement X

a la fermé0

Réseau rapide dédié à l'assemblage

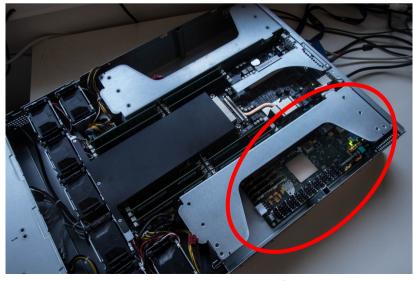

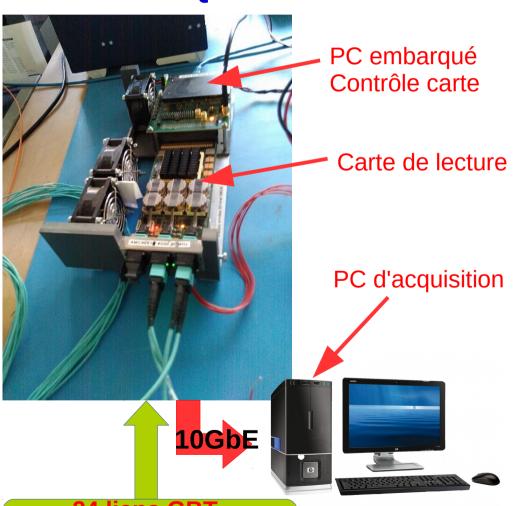

# Outils de développement pour la collaboration MiniDAQ1

### MiniDAQ1

Chaque groupe de détecteur doit intégrer ses propres fonctionnalités dans le système DAQ pour :

- intégrer son propre format d'événement dans les cartes de lecture (firmware)

- intégrer son contrôle de front end et d'acquisition dans l'ECS (logiciel)

Besoin de tester et mettre au point la chaîne DAQ de leur détecteur en laboratoire

Une plateforme de développement appelée MiniDAQ livrée avec des frameworks logiciels contenant déjà toutes les fonctionnalité communes.

**24 liens GBT**FE en développement

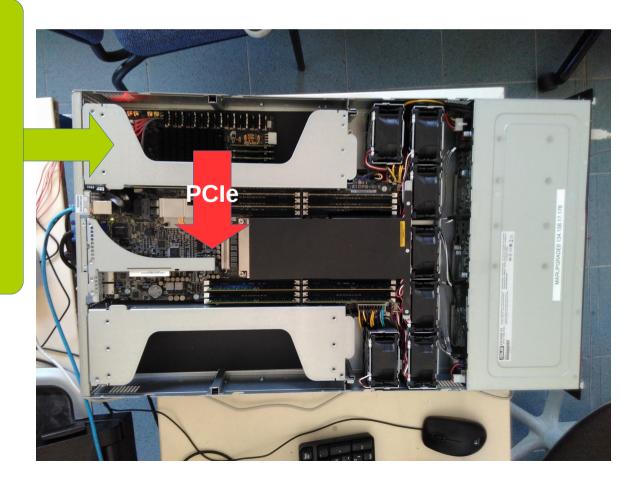

# Outils de développement pour la collaboration MiniDAQ2

Les mêmes fonctionnalités sont portées sur la nouvelle PCIe40 et le PC d'acquisition avec la lecture à travers le PCIe à 100Gbs.

**24 liens GBT** FE en développement

## Outils logiciels pour la collaboration

### <u>Développement collaboratif avec GIT:</u>

- 6 groupes de développement associés à des détecteurs

- 9 développements associés à des modules ou variantes spécifiques

À intégrer dans un seul framework

Shéma d'organisation : une branche par activité et master pour l'intégration

Support : GITLAB CERN + CI vérifier le domaine d'intervention des développeurs

### **Communication et distribution avec REDMINE:**

- Documentations

- Mise à disposition des distributions/releases

- Système de tickets pour les bugs et demandes de fonctions

- Communication en générale

## Conclusions

LHCb sera pionnier sur la réalisation d'un DAQ sans sélection au LHC.

Très forte utilisation de composants standards du commerce (COTS).

Développement de sa propre carte PCIe polyvalente conçue autours des besoins d'une l'expérience LHC : DAQ, Contrôle et TFC.

Nombreux développeurs géographiquement répartis qui doivent se coordonner à travers des outils collaboratifs.

L'IN2P3 à travers le CPPM et le LAPP est un acteur majeur dans ce projet

## Compléments

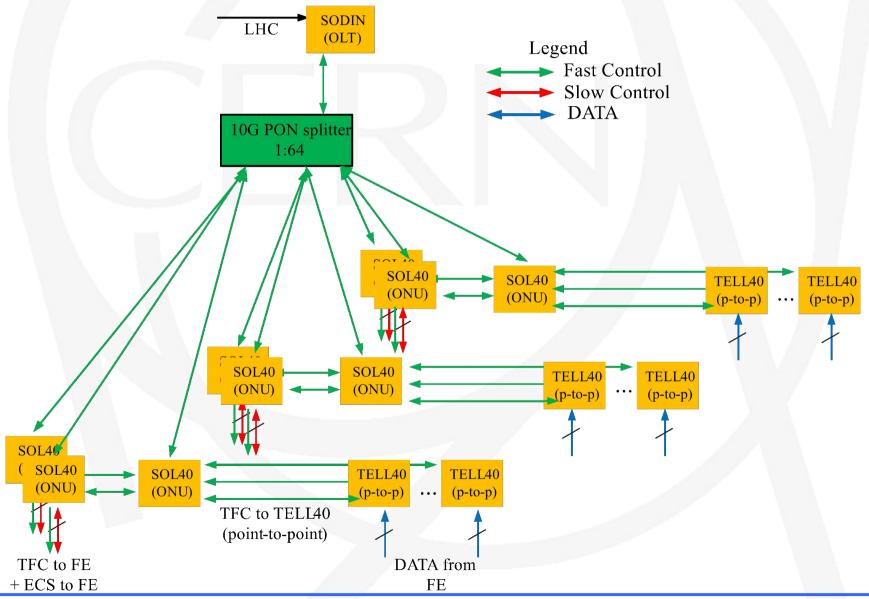

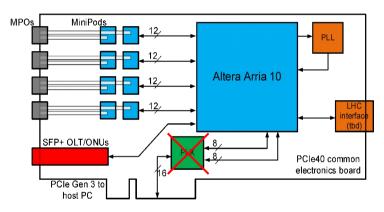

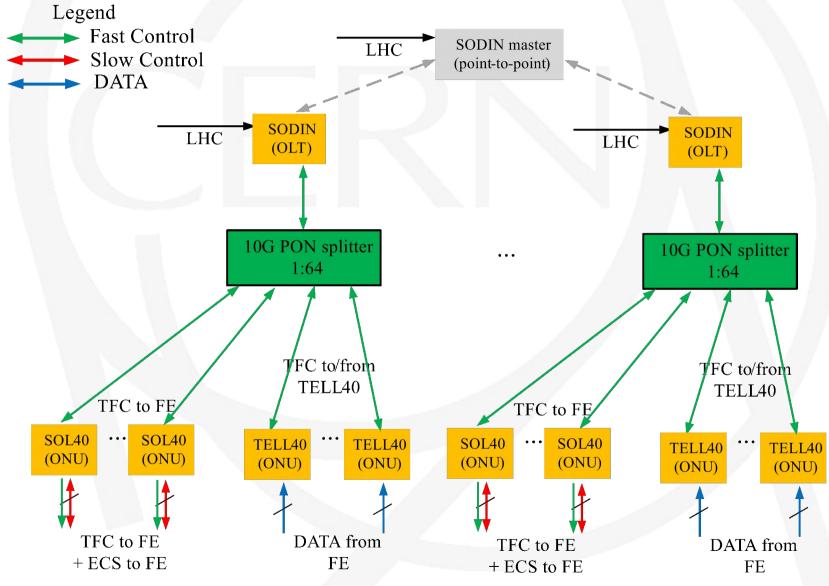

## TFC on common hardware backbone

#### In principle:

- Firepower of 48 bidir links

- TTC-PON interface OLT/ONUs with SFP+

- Deterministic on board external PLL for resynchronization

Same exact hardware (PCle40), firmware defines the functionality: SODIN, SOL40, TELL40

- The Host PC is the PC controlling the board

- In principle ~100 Gbps of ECS access

The only difficulty in the system is the PON splitter, currently limited to 64 destinations

- May need cascading or may need a different SODIN hardware (with many SFP+ OLT/ONUs instead

of MiniPods) → to be discussed later on

- As usual, tight and proficuous collaboration with CPPM and EP-ESE

## Composants du DAQ

### Dimension du sytème:

- ~10000 liens à 4,8 Gb type GBT

- ~500 nœuds d'acquisition (PC)

- ~30 MHz vitesse de l'event builder

- ~130 kB par évènement

### Réseau d'assemblage :

~40 Tb/s bande passante agrégée

Utilisation de réseau standards à 100

Gbit/s

## Configuration et contrôle via le sous-système ECS (WINCCOA)

Synchronisation globale via the sous-système TFC (horloges, message rapides sync)

# EVENT BUILDING NETWORK TESTS

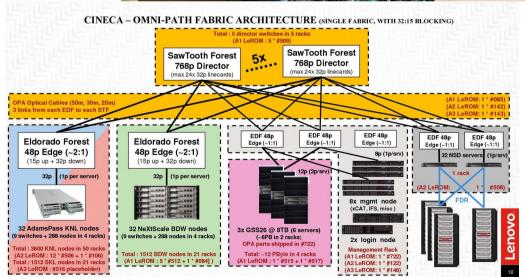

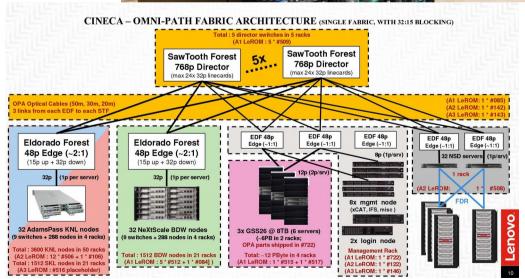

DAQPIPE Scalability tests with Intel OMNI-PATH on the MARCONI Super computer at CINECA

#### What we used:

- Up to 512 nodes

- Comparable size with the future event builder

- Topology:

- Each 48 switch port

- 32 links to nodes

- 15 up links to 5 spine switch

- To get similar to full fat tree:

- Using only 16 nodes per island

# EVENT BUILDING NETWORK TESTS

DAQPIPE Scalability tests with Intel OMNI-PATH on the MARCONI Super computer at CINECA

#### What we used:

- Up to 512 nodes

- Comparable size with the future event builder

- Topology:

- Each 48 switch port

- 32 links to nodes

- 15 up links to 5 spine switch

- To get similar to full fat tree:

- Using only 16 nodes per island

## ECS UPGRADE

### Controls and monitors all subsystems

DAQ, TFC, HLT, farm and FEs!

### Continuity from current implementation

JCOP / DIM / WinCCOA / SMI++ / Recipes

Main ECS components to control the Front End Devices via the GBT-SCA ready and available to sub-detectors

21

# TFC architecture – option 1 fully PON architecture

# TFC architecture – option 2a hybrid w/ single SODIN