# R&D autour d'un Si-W ECAL

R. Cornat, LLR remi.cornat@in2p3.fr

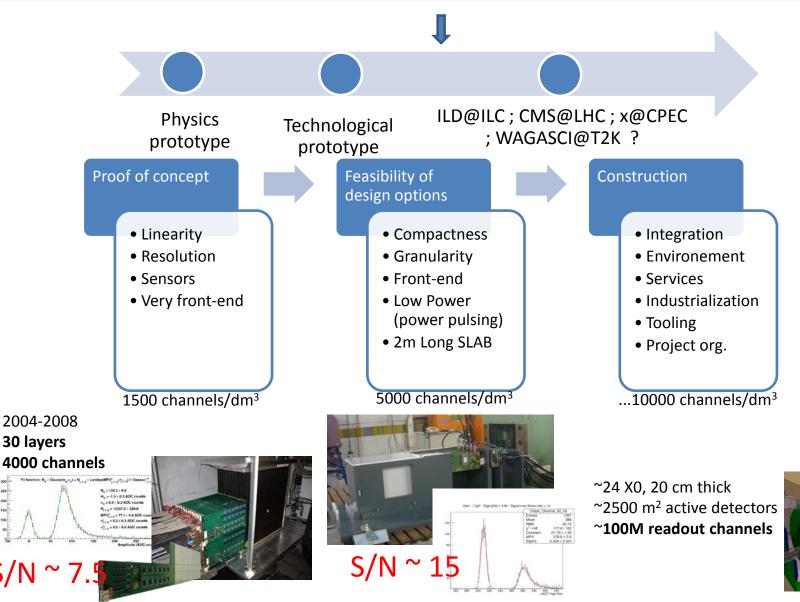

# Time line

#### Prototyping : who is doing what

POLYTECHNIQU

## Activities at LLR (CALICE)

|        | Sensors                                                           | VFE & FE boards                                                                             | DAQ                                                                                    | Integration<br>& super-structure                                              | SW ecosystem<br>s for ECAL                                                                 |

|--------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| <2015  | · ·                                                               | -VFE : 256 chn, not opt<br>-Universal Det. Interface<br>-Test tools (w/o gluing)            | -Universal DAQ for<br>small throughput<br>-Moderate power                              | Prototypes<br>-Composite struct.<br>-Single layer slab<br>-Cooling, Gluing    | <ul> <li>configuration &amp;<br/>raw data storage</li> <li>Det &amp; test bench</li> </ul> |

| 2015   | -Test tools<br>-Larger size13cm<br>-LFoundry<br>-Small prod tests | -VFE : 1024 chn.<br>-Long slab (4 boards)<br>-Partial Opt. of PSRR &<br>interchip couplings | -Partial inclusion of<br>DIF functionalities:<br>towards a local<br>controller 100kchn | -Small prod of ASUs<br>-Test with cosmics<br>-Slim slab design                | -Extended with<br>data logger,<br>pre-processing,<br>run control                           |

| future | -Harvesting new<br>manufacturers<br>-Mass tests tools             | -Longer slab (8 boards)<br>-System redesign (PSRR)<br>-Power distribution                   |                                                                                        | -Design update<br>-Long slab<br>-Consolidated proto.<br>-Tools<br>-Beam tests | -Connexions to<br>other sub-syst.<br>-Event bulding                                        |

ÉCOLE POLYTECHNIQUE

#### Project activities (mid term)

|         | Sensors                                                     | VFE & FE boards                                                          | DAQ                                                                                                | Integration<br>& super-structure                                                             | SW ecosystem                                                                      |

|---------|-------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| outcome | -HPK w/o GR                                                 | -performance of single<br>(few) channel(s) with<br>power pulsing and SK2 | -Modular system for<br>Small setups                                                                | Prototypes<br>-Composite struct.<br>-Single layer slab<br>-Gluing                            | -Modular SW<br>-Diffusion among<br>partners                                       |

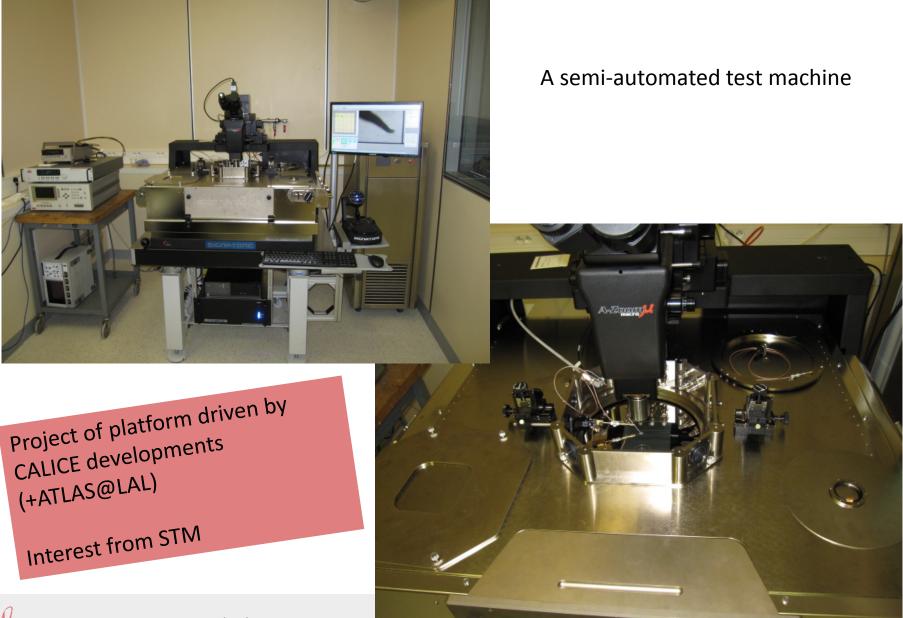

| ongoing | -Lowering dead<br>area                                      | -understand self couplings<br>-Performance with beam<br>-                |                                                                                                    | -Semi-automated<br>Integration bench                                                         | -Add function.                                                                    |

| issue   | Rad. Hard.<br>New GR struct.<br>(larger panel of<br>manuf.) | -System redesign for<br>SK2: PSRR, PP<br>-New chip ?<br>-Chip on board   | -Higher level data<br>Concentrator<br>- Real low power<br>-LV & HV distribution<br>-DCS and system | -reproducibility<br>-Full integration<br>with cooling,<br>top of module elec.<br>& structure | -Double layer slab<br>-Long slab<br>-Consolidated proto.<br>-Tools<br>-Beam tests |

5

\_\_\_\_ remi.cornat@in2p3.fr – 05/10/15 - Calice France

### Long term activities

- Scaling to an experiment depends...on the experiment (not the scope of current activities)

- But: on going R&D based on requirements for ILC (since 2006) for the demonstration of the concept

- Gain of credibility with a well integrated prototype (was EUDET prototype)

- Needs funds and manpower (buy sensors, intrinsic cost of serious hardware, prototyping iterations, etc...)

- Needs a definition of the project and its management

- Many spin-off (LLR): CMS/HGCal, T2K, JUNO, CPEC, ILC...

- Demonstration in the following:

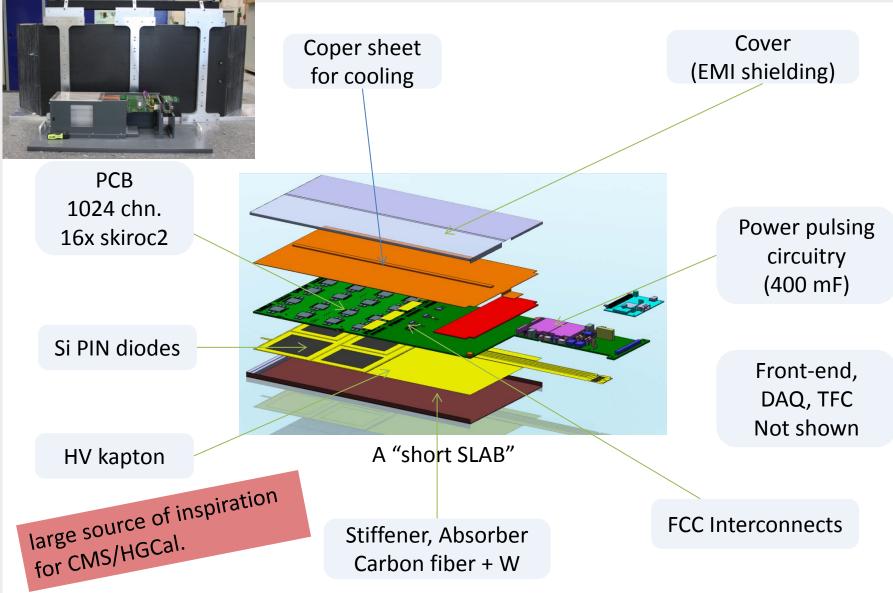

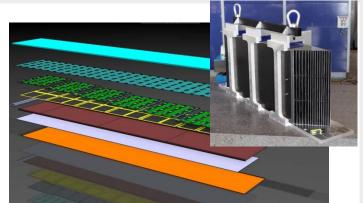

### A detector module + composite structure

# Next version(s) of VFE board

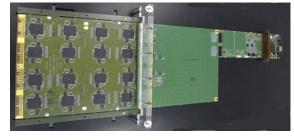

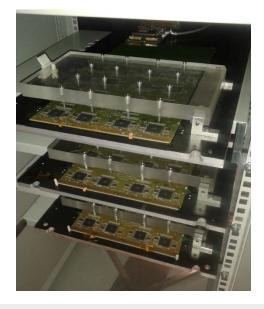

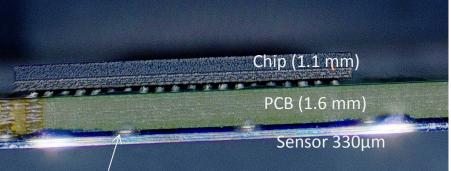

18 x 18 cm<sup>2</sup> front-end board includes 1024 channels (16 chips), almost perfect flatness required for gluing the sensors : 1.6mm symmetrical stacking

LFBGA packaged chips and Panasonic Sp-CAP CX series ⇒ 1.1mm thick components envelop

With packaged chips version the overall module thickness would be 5.5 mm (+absorber) : >4600 ch/dm<sup>3</sup>

Naked die version would provide optimal module thickness (<4mm in total, >6000 chn/dm<sup>3</sup>)

Electrical tests are ok but flatness is incompatible with sensor gluing.

### DAQ

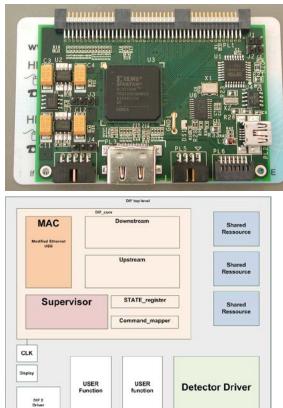

#### DIF

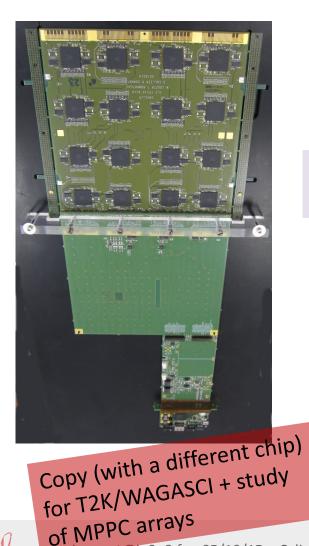

Baseline for T2K/WAGASCI + JUNO/Trigger-DAQ Read out of SKIROC2, SPIROC2, MAROC3, EASIROC...

9

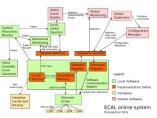

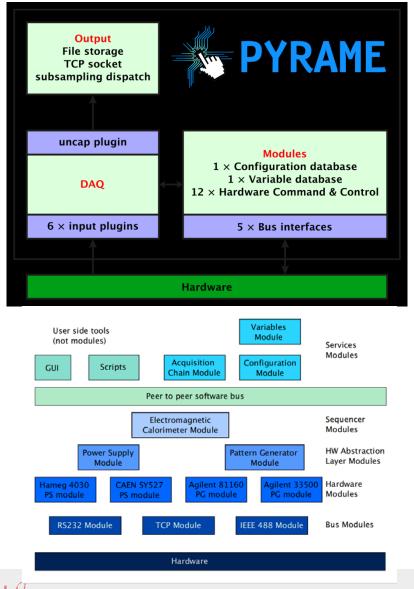

#### SW http://llr.in2p3.fr/sites/pyrame/

remi.cornat@in2p3.fr - 05/10/15 - Calice France

Prototyping framework for online systems. Heavily modular for control-command or data acquisition.

Flexible and providing lots of options, allowing the system to evolve as fast as the testbench.

Baseline for T2K/WAGASCI Used on P2IO/captinnov platfom

```

Used on CILEX/Galop

Used on CTA/NectarCam test

benches

```

Proposed to CMS/HGCal and JUNO (small setup DAQ)

Used on many LLR testbenches And at LAL & Japan for ECAL test benches

ÉCOLE POLYTECHNIQUE Inverteure Partie-Facture 10

### Latest news @LLR

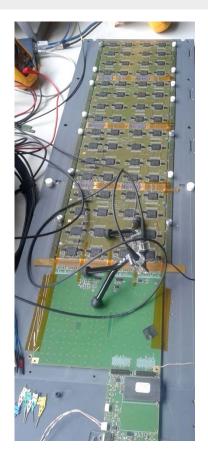

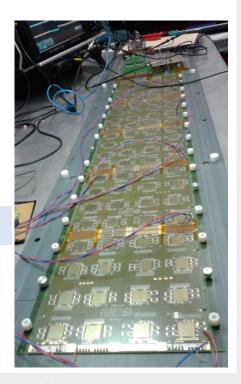

Long slab with 4096 channels : Configuration ✓ ok Read-out ✓ ok

Study of long transmission lines with high capacitive load : × on going Study of power distribution : × on going

Preparation of a test beam setup @CERN (Nov. 4-16 2015) : 3 planes ✓ok Slow control & Read-out ✓ ok

Study of long transmission lines with 4<sup>th</sup> plane : × on going Calibration : × on going

# Follow up of generic R&D 2016-17 @LLR

- Merging of DIF&(G)DCC : generic read-out HW , addressing issue of syncho, time stamping and time measurement.

- Designing long detector modules (CALICE as a study case)

: R&D on transmission lines with high capacitive loads,

power distribution (sim & proto), power pulsing

- Integrating the "EUDET" module : simulations of heat dissipation, miniaturized connections, stress tests of composite structures, slab design (CMS, ILC, CEPC)

- Toward the completeness of the online software : event building + integration with other frameworks (XDAQ, EUDAQ, etc...) and standards (OPCUA, IPBus,...)

# IT Manpower at LLR

| Nom                | Sujet                   | Generic (CALICE) | Specific        |

|--------------------|-------------------------|------------------|-----------------|

| Michael Frotin     | Intégration             | 10%              | 40% (CMS)       |

| Marc Anduze        | Structures              | 10%              | 25% (CMS)       |

| Frédéric Magniette | Online SW               | 20%              | 80% (CMS)       |

| Miguel Rubio-Roy   | Online SW               | 20%              | 80% (LLR)       |

| Jérome Nani        | Instrumentation,<br>DAQ | 50%              | 50% (LLR)       |

| Franck Gastaldi    | DAQ                     | 10%              | 90% (T2K, JUNO) |

| Rémi Cornat        | Instrumentation,<br>DAQ | 40%              | 40% (JUNO, CTA) |

|                    |                         | 1.6 FTE          |                 |

remi.cornat@in2p3.fr – 05/10/15 - Calice France

#### R Manpower at LLR

| Nom                 |         |             |

|---------------------|---------|-------------|

| Vladik Balagura     |         | 100%        |

| Vincent Boudry      |         | 100%        |

| Henri Videau        |         | 100%        |

| Jean-Claude Brient  |         | 10%         |

|                     |         |             |

| Kostya Spack        | PhD.    | 100%        |

| Dan Yu              | PhD.    | 100%        |

| Trong Hieu -> Bo Li | PostDoc | 100%        |

|                     |         | 3.1 + 3 FTE |

remi.cornat@in2p3.fr – 05/10/15 - Calice France

# 2015 Results

# I.2 Sensitivity to noise from other chips

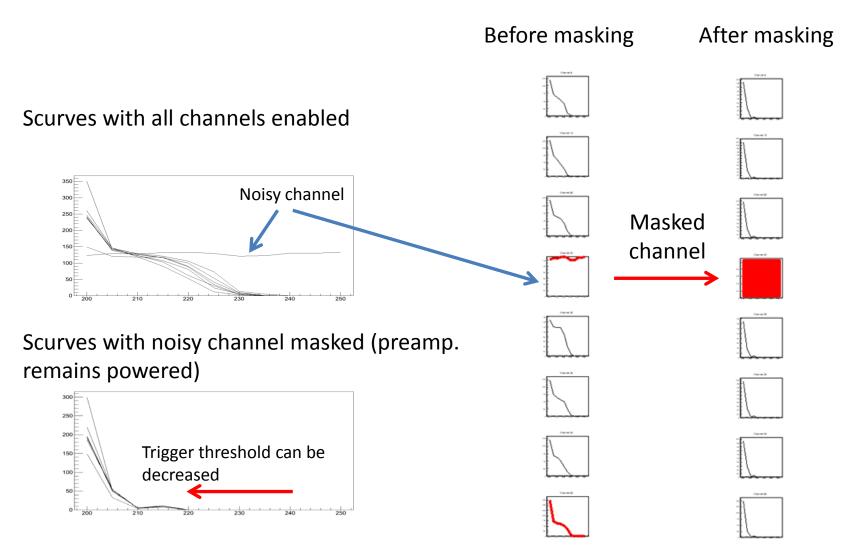

Rough Scurves of a few selected reference channels on a reference chip

0, 8, 16 then 32 channels/chip are made noisy (trigger enabled + threshold set at 180 maximum toggling of internal triggers)

→ Reference Scurves remains the same whatever the number of noisy channels is

#### Courtesy of J. Nanni (LLR)

# I.3 Internal noise

→ Digital noise due to generation of internal triggers

17

POLYTECHNIQUE

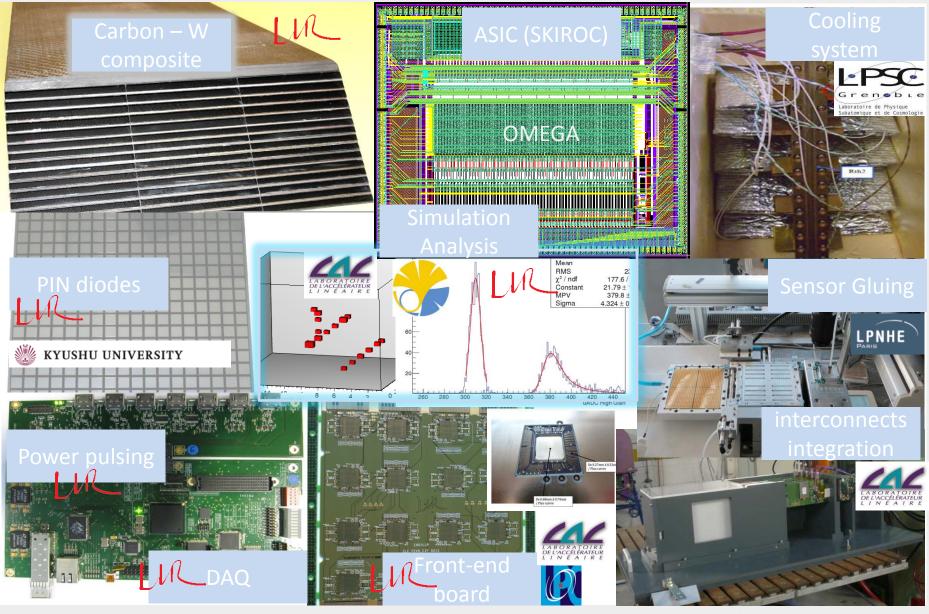

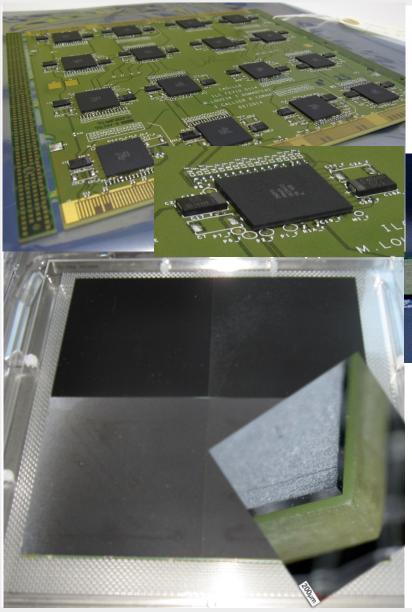

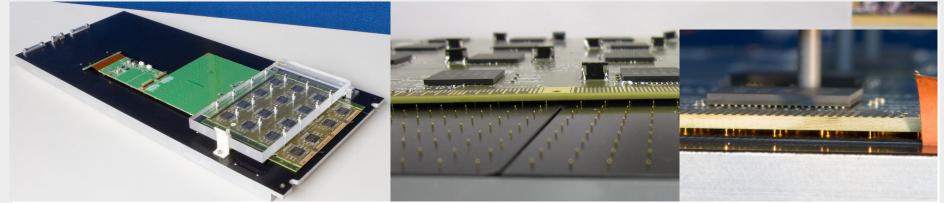

### **Detector module assembly**

Robots for gluing sensors are developed (LPNHE) ⇒ First step towards industrialization

Conductive glue dots (200µm)

4 wafers 9cm x 9 cm wide can be glued with a 20  $\mu$ m precision and a reproducible process. Glue is dispensed then pressed in order to form 200  $\mu$ m thick dots

remi.cornat@in2p3.fr – 05/10/15 - Calice France

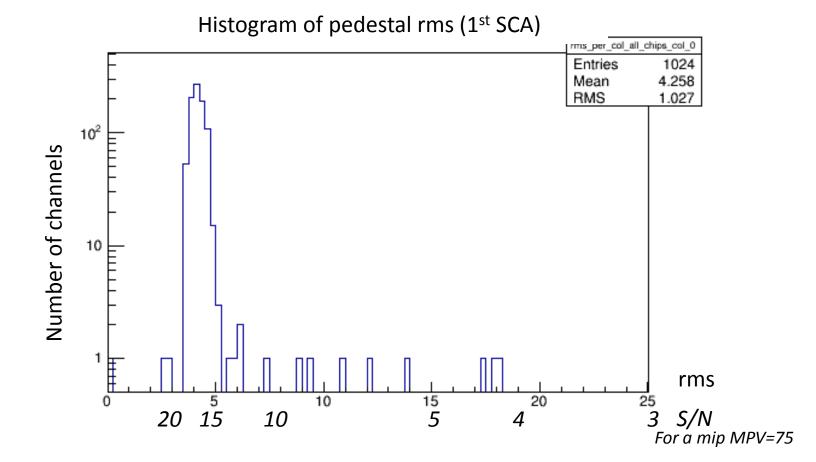

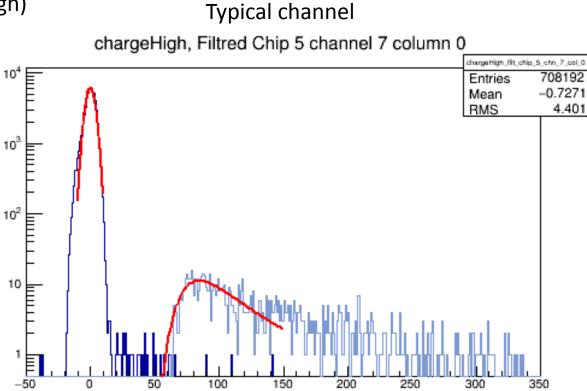

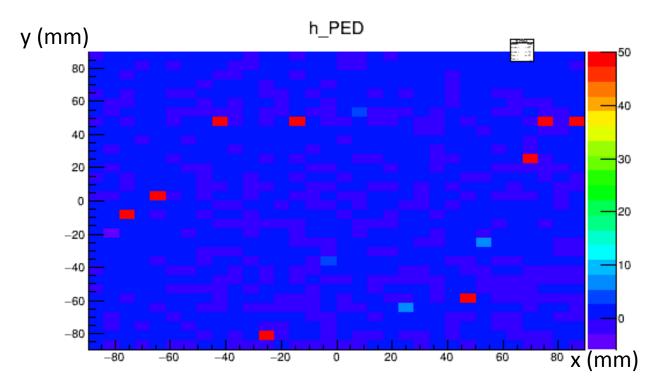

## II.1 Pedestals with glued sensors

remi.cornat@in2p3.fr – 05/10/15 - Calice France

19

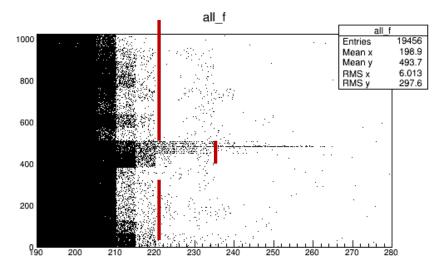

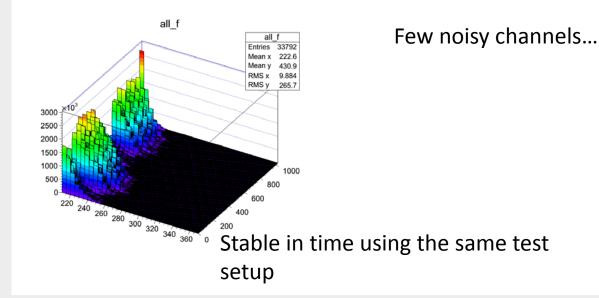

### II.2 Scurves

New cabling of the power supplies , isolated room

Uniform threshold arround 220-230 DACu possible

POLYTECHNIQUI

#### II.2 Scurves

Probable effect of internal digital noise

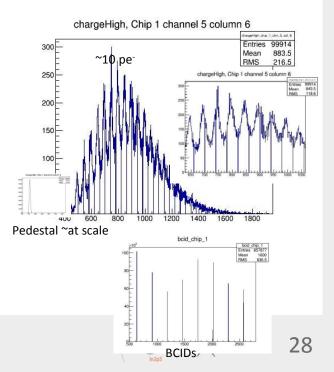

## II.3 Cosmics data taking

50 hours, Spill at 10 Hz, duty cycle 60% DIF in TestBeam mode

Gain: 1.2 pF (high)

## II.3 Cosmics data taking

5 cosmics run taken, ~consitent

Pedestal uniformity after correction (= mean of gauss fit)

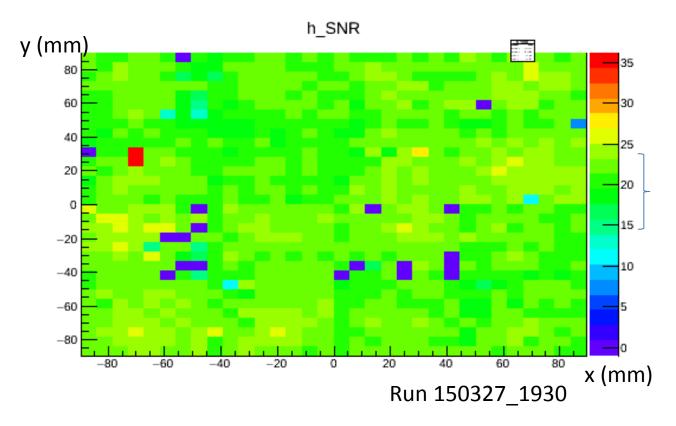

# II.3 Cosmics data taking : SNR

Some fit error + missing channels (to be verified)

Quality of fits not checked

Part of landau can but cut (high threshold) : overestimation of MPV

... but preliminary results are encouraging!

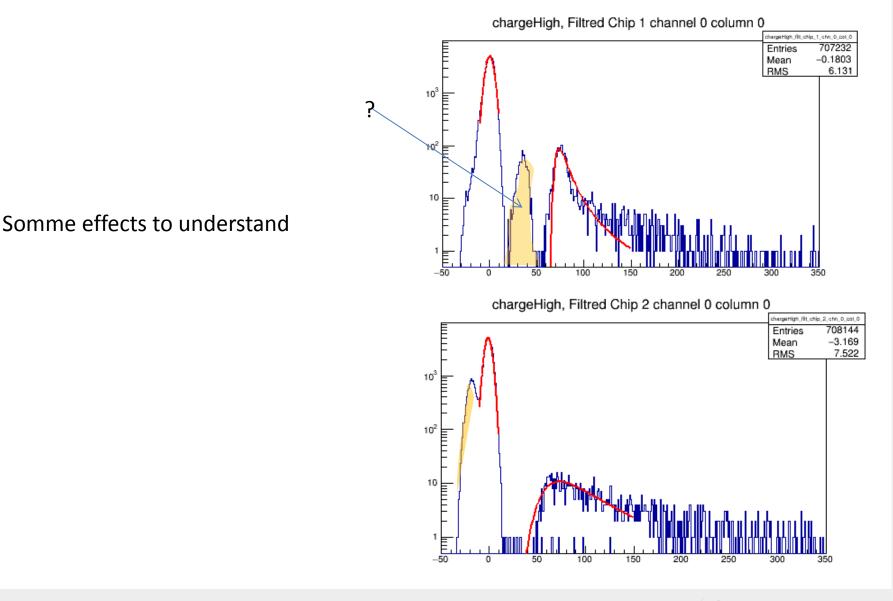

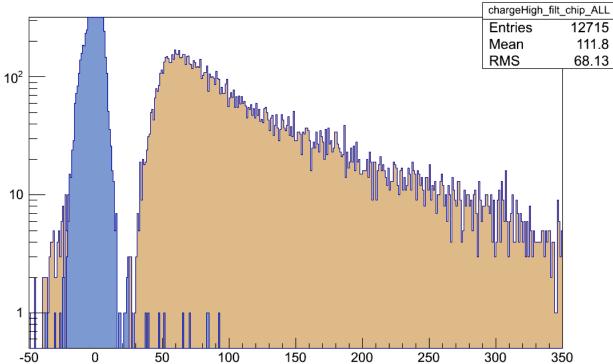

### II.3 Cosmics data taking

#### All channels of a chip merged together (raw data with no cut)

chargeHigh, Filtred ALL

# Toward a full length module

In principle, front-end boards will be chained forming up to 2m long detector SLAB, most of signals in bus

Issue 1 : clock distribution (5 & 50 MHz) Interconnects are not impedance controlled (FFC) One clock line may be loaded by 40 to 80 ASICS

⇒ Use of MLVDS adapted with 100 Ω on both sides, 100 mVpp remaining signal at the end (6 Ohms loss/board, 20-40 pF/board, up to 10 boards)

⇒ Next version ASIC will have a PLL generating the highest frequency

Issue 2 : Power distribution (12 A pulses) & blocking capacitors (tested with FET switches as loads)

$\Rightarrow$  Current taken from a 800mF super cap (16m $\Omega$  ESR) + 2mF/board

Along 6 boards, static loss is 250 mV due to connectors (w/o chips).

May foresee to distribute power in a star topology.

4 boards SLAB being assembled at LAL

large C-W structure exists

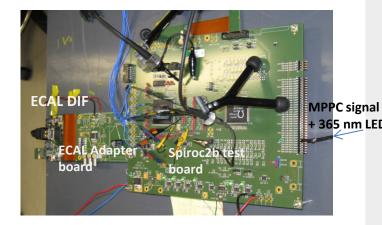

# V. Extension to other chips (T2K, JUNO)

#### Test setup with a spiroc2b

- Use of a modified test board from Omega

- Fpga bypassed by an ECAL DIF

- ~<u>same DIF firmware</u> as for ECAL (modified pin-out and signal levels)

- MPPC + LED pulser (16 pulses within a spill)

#### **Combined tests**

- Added an ECAL slab in the setup

- Common data acquisition as soon as SPILL signal is sent

- CCC : Same SPILL, same slow clock

- Events not in time (LED on one side, noise on the other) but cosmics would have been.

- Easiroc and Maroc will be added soon (started)

## Wafer R&D

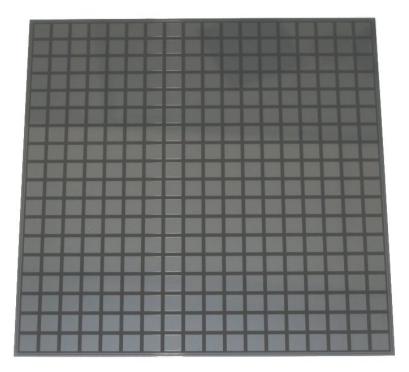

#### Large size matrix burned on 8' wafers

- Ordered (LFOUNDRY)

- 700, 500 or 300 µm thickness

- 13.5 cm large

- 24\*24 pixels

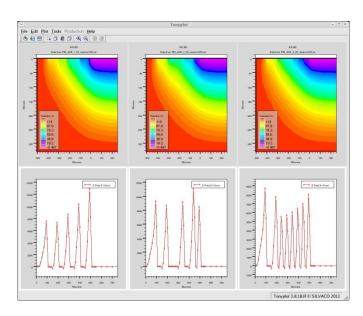

#### **Segmented guardrings**

- Layout done at LLR

- From previous designs (baby wafers)

- Attempt to optimize structure by simulation

POLYTECHNIQU

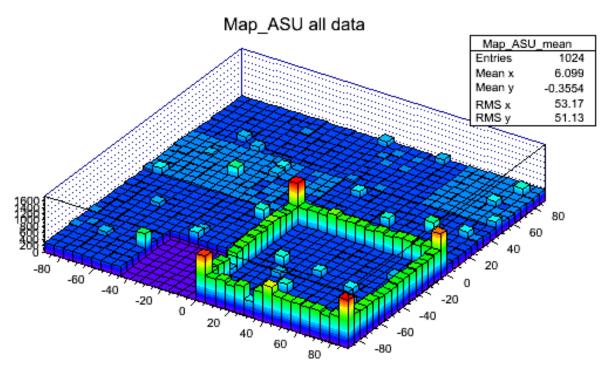

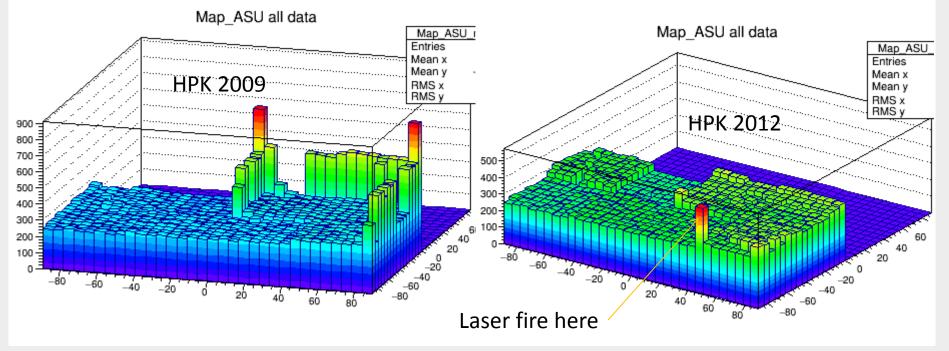

## II.4 Square events

Infrared laser + fibre 20 ps light pulse FEV10 board + glued sensors (from 2009 batch)

All channels enabled (no masking), power pulsing Gain : 1.2 pF, Threshold : 400

#### III. Desktop test setup with unglued sensors

Comparison of 2 different wafer design (with/witout guard rings) Missing signals (bad contacts with springs ?)

## P2IO/Captinnov Platform

1

# Example of an application

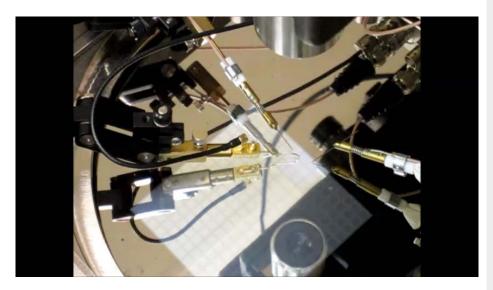

Map of leakage current of the 16 x 16 (9x9 cm<sup>2</sup>) PIN diodes detector for the CALICE/ILD Si-W ECAL

The scan is fully automated and the measurements are synchronized with the machine, Duration of the scan: 30 minutes for 256 diodes.

Map from the manufacturer (2011)

Measured map (09/06/2015 – preliminary –)

nA nA 22-20-18-16 14 12 10 10 8 6 4 2 0 2 Correlation Manufacturer 10

Measured

#### HPK WMap

#### WMap

# Conclusion

#### Preliminary tests of the first front-end board

LPNHE

All results should be checked will higher statistics and better methodology Signal over noise ratio seems to exceed design goal<sup>RunNum = 0, EventNum = 5401</sup> 98% of channels are responding (cosmics) Successful operations with **full** power pulsing Missing : linearity, crosstalk etc...

Production of a small batch of 8 slabs Gluing of sensors planed for end of May/June Assembly of slabs : September

Next engineering step is building a long detector module Requires specific studies of the power distribution Already tested 2 front-end boards together