### **HARDROC 3 for SDHCAL**

02 / 02 / 2014 - HGC4ILD Workshop

**OMEGA** microelectronics group

Ecole Polytechnique CNRS/IN2P3 , Palaiseau (France)

Organization for Micro-Electronics desiGn and Applications

# ROC chips for ILC prototypes Omega

SPIROC2 Analog HCAL (AHCAL) (SiPM) 36 ch. 32mm<sup>2</sup> June 07, June 08, March 10, Sept 11

ROC chips for **technological prototypes**: to study the feasibility of large scale, industrializable modules (Eudet/Aida funded)

**Requirements for electronics**

- Large dynamic range (15 bits)

- Auto-trigger on ½ MIP

- On chip zero suppress

- 10<sup>8</sup> channels

- Front-end embedded in detector

- Ultra-low power : 25µW/ch

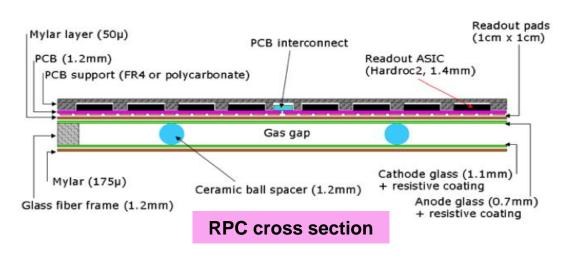

HARDROC2 and MICROROC Semi Digital HCAL (SDHCAL) (RPC, µmegas or GEMs) 64 ch. 16mm<sup>2</sup> Sept 06, June 08, March 10

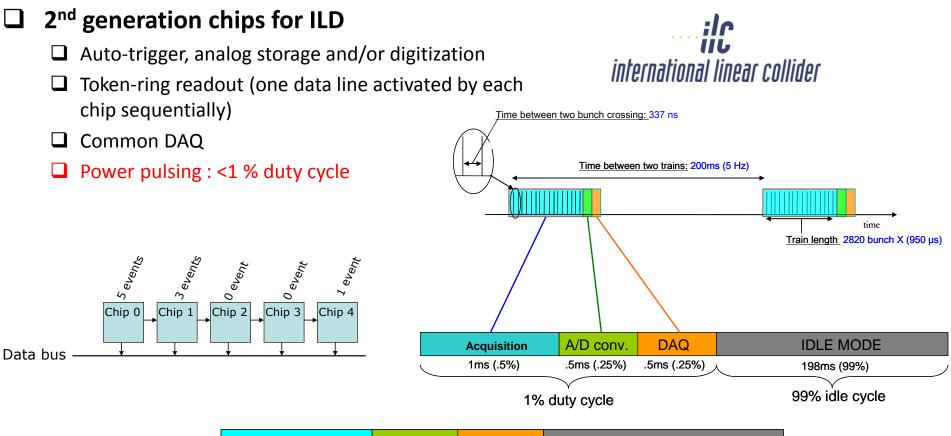

# From 2<sup>nd</sup> generation...

| Chip 0 | Acquisition | A/D conv. | DAQ  |     | IDLE | MODE      |

|--------|-------------|-----------|------|-----|------|-----------|

| Chip 1 | Acquisition | A/D conv. | IDLE | DAQ |      | IDLE MODE |

| Chip 2 | Acquisition | A/D conv. | IDLE |     |      | IDLE MODE |

| Chip 3 | Acquisition | A/D conv. | IDLE |     |      | IDLE MODE |

| Chip 4 | Acquisition | A/D conv. | IDLE |     | DAQ  | IDLE MODE |

## ...To 3<sup>rd</sup> generation

- □ 3<sup>rd</sup> generation chips for ILD

- Independent channels (zero suppress)

- I2C link (@IPNL) for Slow Control parameters and triple voting

- configuration broadcasting

- geographical addressing

□ HARDROC3: 1<sup>st</sup> of the 3<sup>rd</sup> generation chip to be submitted

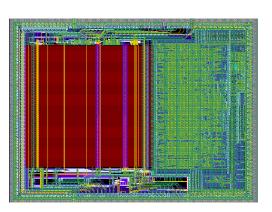

- Received in June 2013 (SiGe 0.35µm) (AIDA funded)

- Die size ~30 mm<sup>2</sup> (6.3 x 4.7 mm<sup>2</sup>) Packaged in a QFP208

### **HR3: Simplified schematics**

64 channels 🚽 H o ld Read Multiplex 64 channels with current preamplifiers Gain correction Charge output SLOW Shaper 8 bits/channel Variable Trigger less mode (auto trigger 15fC up **Bipolar FAST** ∟Read Gain PA Chj\_trig0 Latch to 10pC) Shaper 0 Vth0 RS or64 0 <i Ctest ch<j> **<u></u><u></u><sup>+</sup> 2 p F** Vth0: 10fC to 100fC Discri. Slow Ctrl m ask0 trigger0<j> Gain correction (max factor 2) Chj trig1 Ctest\_Chi **Bipolar FAST** Latch Vth1 RS Shaper 1 nor64 1 <j; Discri mask1 trigger1<i> Vth1: 100fC to 1pC 3 shapers + 3 discriminators (encoded in Read Chj\_trig2 **Bipolar FAST** 2 bits for readout) Latch Vth2 Shaper 2 RS nor64 2 <i> mask2 Vth2: 1pC to10pC trigger2<j> **I2C link for Slow Control** trigger0 encod0<i> trigger2 ENCODER RAM encod1<i> 8 events 12 Bit counter BCID Independent channels with zero trigger0<j> trigr0<j> valid\_trig0 WR\_MEM<j> (12+ 2) bits suppress trigger1<j> trigr1<j> valid trig1 1 Digital Memory/ch trigger2<j> trigr2<j> Max 8 events / channel with 12-b time valid\_trig2 stamping DIGITAL PART Common to the 64 channels DAC2 Vth2 Integrated clock generator: PLL 10 bits ≶ ≶ Vth1 or64 0<0:63> DAC1 **OR64** 10 bits Power pulsing mode nor64 1<0:63> Vth0 DACO or64 2<0:63> 5 10 bits

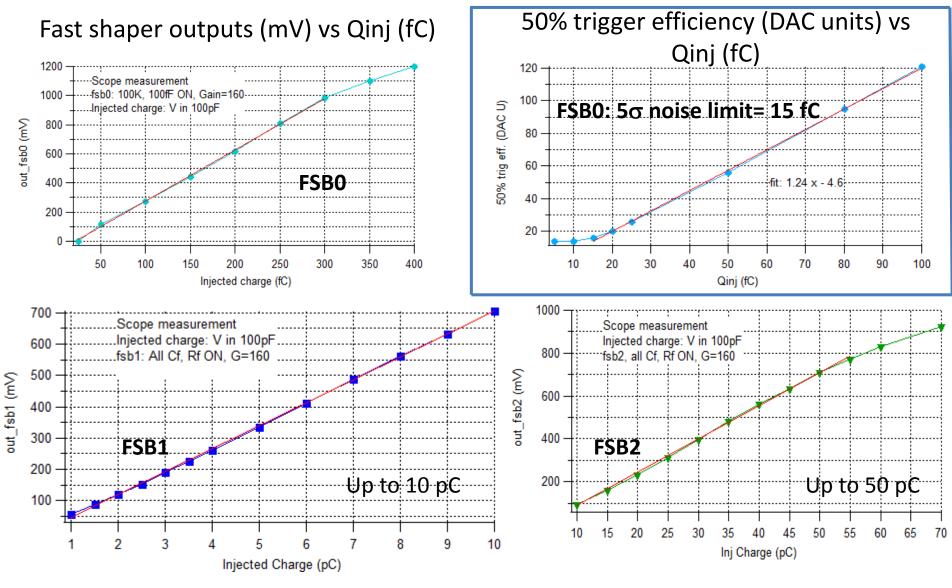

### **Analog Part: FSB Linearity**

Dynamic range: 15fC - 50 pC

### **Gain correction / Scurves**

Qinj=100fC

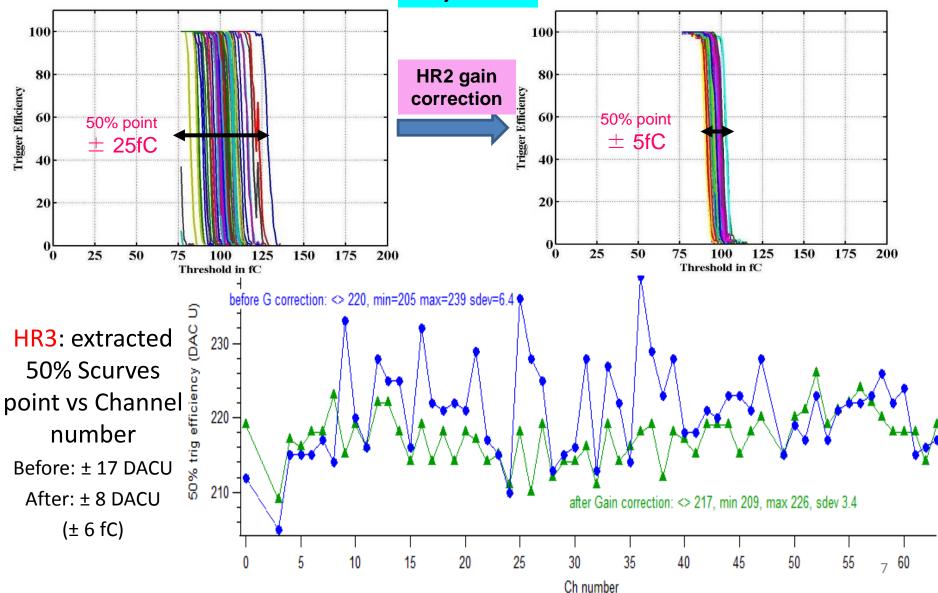

## **New Slow Control: I2C**

- I2C standard protocol access (max 127 chip / line)

- Possibility to broadcast a default configuration to all the chips

- Read and write access to a specific chip with its geographical address

- Triple voting for each parameter (redundancy)

- Read back of control bit (even if the chip is running / copy)

nega

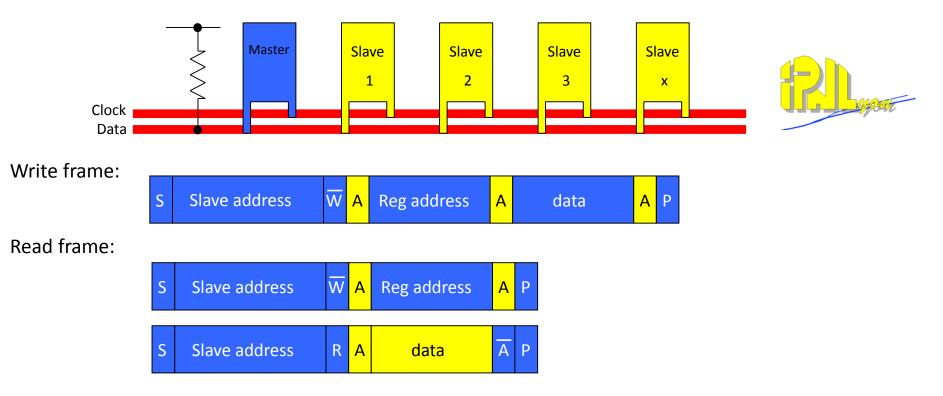

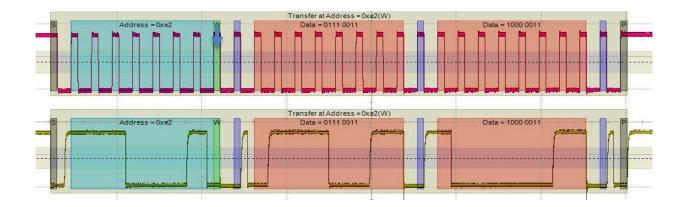

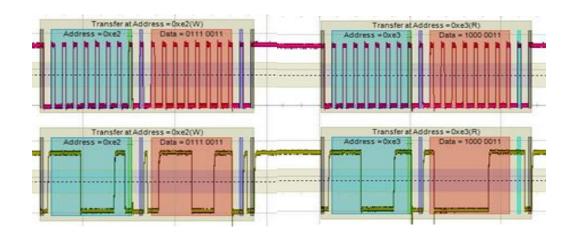

### **I2C** measurements

- I2C Write acces : Chip number (ID): 0xE2 / Reg @: 0x73 / WrData: 0x83

- I2C Read acces : Chip number (ID): 0xE2 / Reg @: 0x73

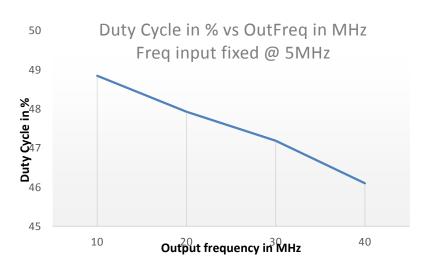

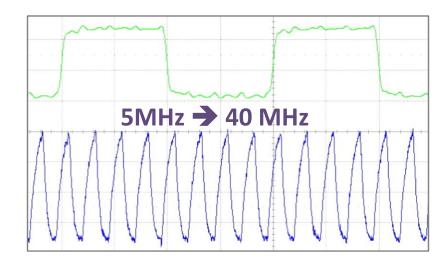

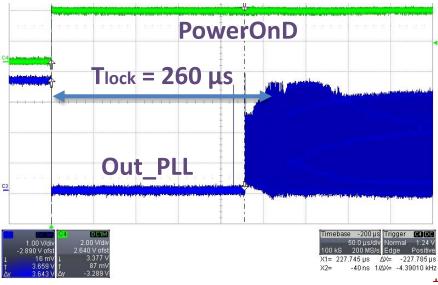

### **PLL measurements**

#### **2** clocks are needed to start the chip

- Slow Clock (1-10 MHz) related to the beam train (for Time stamping and data readout)

- ➡ Fast clock (40-50MHz) for internal the state machines

#### A PLL (clock multiplier) has been designed to generate the fast clock

- Multiplication factor is (N+1) / N is a SC parameter (1 to 31)

- □ Full chain tested using PLL

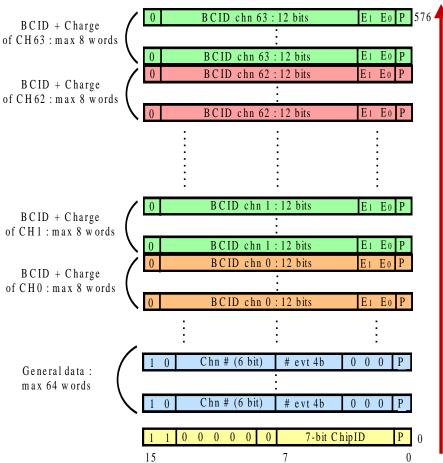

## Zero suppress: Memory mapping Omega

- Chip ID is the first to be outputted during readout (MSB first)

- MSB of each word indicates type of data:

- "1": general data (Hit ch number and number of of CH62 : max 8 words events)

- "0": BCID + encoded data

- A parity bit/word

- Up to 9232 bits (577x16) during readout

- Example of number of bits during readout:

|                        | HR2  | HR3 |

|------------------------|------|-----|

| 1 chn hit              | 160  | 48  |

| 8 chn hit              | 1280 | 272 |

| 4 chn hit @ same time  | 160  | 144 |

| 10 chn hit @ same time | 160  | 336 |

RE

A D

(readout)

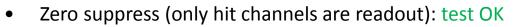

### Zero suppress: Tests

| Setup                                                      | Slow Co                                                                                                                  | ntrol 1  | Slo  | ow Cont           | rol 2 | SCA                                       | Read, | Temp. | FP                        | GA Configuration Info HARDRO |      |      | DC3  | I2C test Info pcb I/O |                                                                                                                                                                                                                          |      | Inf      | fo pcb   | Test | Mixe | eshold) |                             |   |   |   |   |   |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------|------|-------------------|-------|-------------------------------------------|-------|-------|---------------------------|------------------------------|------|------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|----------|------|------|---------|-----------------------------|---|---|---|---|---|

| Mixed Test: S-Curve (Threshold) all Ch. Analogue Test: DAC |                                                                                                                          |          |      | Analogue Test: DC |       |                                           |       |       | External ADC External ADC |                              |      |      |      | calib                 | calib Digital ASIC Debug / DAQ                                                                                                                                                                                           |      |          |          |      |      |         |                             |   |   |   |   |   |

| S                                                          | Step by Step DAQ<br>Reset ASIC Digital<br>Start Acquisition<br>FPGA External Trigger<br>Start ReadOut1<br>Start ReadOut2 |          |      |                   | E     | ChipSat<br>End ReadOut 1<br>End ReadOut 2 |       |       |                           |                              |      |      |      |                       | Automatic DAQ D<br>Automatic DAQ<br>Automatic DAQ<br>Start Acq. Sequence<br>ChipSatb must be enabled<br>SlowClock -> CLK_GENE_EXT<br>Nb of Acquisitions<br>10<br>TimeOut for 1 Acq/Conv/RD<br>10ms (Slow Clock @ 5MHz) \ |      |          |          |      |      | Dat     | Analyze saved<br>data now ! |   |   |   |   |   |

| ASIC                                                       | : Memory (F                                                                                                              | law Data | ) De | coded D           | ata   |                                           |       |       |                           |                              |      | _    |      |                       |                                                                                                                                                                                                                          | C    | lurrent. | Acquisit | ion  | 0    | # Sile  | s found                     | 0 |   |   |   |   |

| HR3 Decoded Data                                           |                                                                                                                          |          |      |                   |       |                                           |       |       | Sig                       | nal                          | inje | ecte | ed c | :h 2                  | 0 ar                                                                                                                                                                                                                     | nd d | ch 4     | 13       |      |      |         |                             |   |   |   |   |   |

| Ch                                                         | annel #                                                                                                                  | 20       | 20   | 20                | 20    | 20                                        | 20    | 20    | 20                        | 43                           | 43   | 43   | 43   | 43                    | 43                                                                                                                                                                                                                       | 43   | 43       | 0        | 0    | 0    | 0       | 0                           | 0 | 0 | 0 | 0 |   |

| вс                                                         | ID                                                                                                                       | 3753     | 3253 | 2753              | 2253  | 1753                                      | 1253  | 753   | 253                       | 3753                         | 3253 | 2753 | 2253 | 1753                  | 1253                                                                                                                                                                                                                     | 753  | 253      | 0        | 0    | 0    | 0       | 0                           | 0 | 0 | 0 | 0 | - |

|                                                            | / E0                                                                                                                     | 1        | 1    | 1                 | 1     | 1                                         | 1     | 1     | 1                         | 1                            | 1    | 1    | 1    | 1                     | 1                                                                                                                                                                                                                        | 1    | 1        | 0        | 0    | 0    | 0       | 0                           | 0 | 0 | 0 | 0 | 1 |

- Roll mode SC : test OK

- If RollMode = "0" → Backward compatibility with 2Gen ROC chips behavior

- Only the N first events are stored

- If RollMode = "1" → 3Gen ROC chips behaviour

- Use the circular memory mode

- Only the N last events are stored

- "Noisy Evt" SC: 64 triggers => Noisy event => no data stored : test OK

- "ARCID" SC (Always Read Chip ID): test OK

- If ARCID = 0  $\rightarrow$  Backward compatibility: No event  $\rightarrow$  No readout

- If ARCID= 1 → New behavior: No event → Read CHIP ID

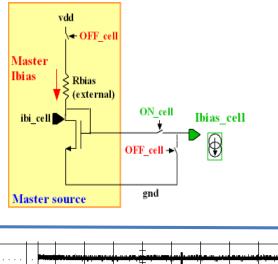

## **Power pulsing in HR chips**

### **O**mega

#### Power pulsing:

- Bandgap + ref Voltages + master I: switched ON/OFF

- Shut down bias currents with vdd always ON

- Compared to HR2, HR3 power consumption is higher due to:

- The extended dynamic range (from 15pC to 50pC)

- The integration of the zero suppress algorithm

- If the PLL is used, the power consumption is increased by 3% (due to the PLL VCO)

| Power supply                      | HR3 with LVDS<br>(5M + 40M)<br>μW / channel | HR2 with LVDS<br>(5M + 40M)<br>μW / channel |  |  |  |  |  |

|-----------------------------------|---------------------------------------------|---------------------------------------------|--|--|--|--|--|

| PowerOnA (Analog)                 | 1650                                        | 1325                                        |  |  |  |  |  |

| Only PowerOnDAC                   | 55                                          | 50                                          |  |  |  |  |  |

| Only PowerOn D                    | 725                                         | 50                                          |  |  |  |  |  |

| Power-On-All                      | 2430                                        | 1425                                        |  |  |  |  |  |

| Power-On-All<br>@ 0,5% duty cycle | 12,2                                        | 7,5                                         |  |  |  |  |  |

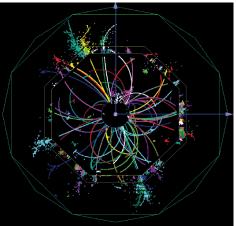

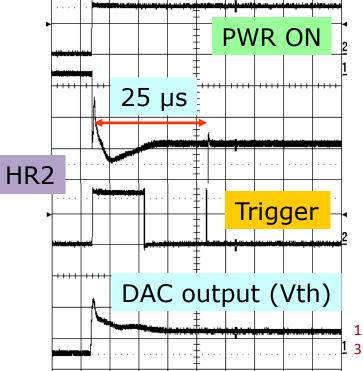

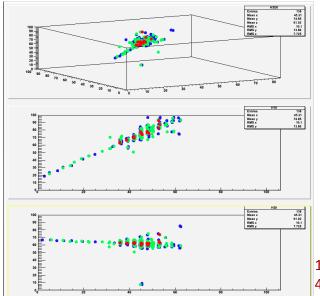

# Power pulsing: Testbeam HR2 Omega

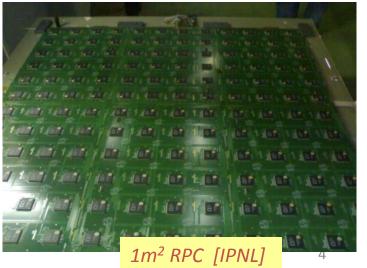

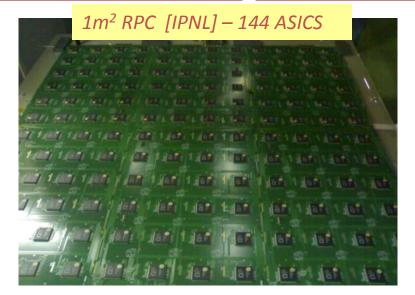

- SDHCAL technological proto with up to 50

layers (7200 HR2 chips) built in 2010-2011.

- Scalable readout scheme successfully tested

- Complete system in TB with 460 000 channels,

AUTOTRIGGER mode and power pulsing (5%)

#### Vth0 Vth1 Vth2

### Summary and next steps

- Good analog performances

- Dynamic range extended up to 50 pC

- Circuit is able to work with only 1 external clock (thanks to PLL)

- New I2C tested successfully

- New digital features validated on testboard

- Zero suppress, roll mode, ARCID mode and Noisy event mode

- External trigger available to be able to check the status of each channel

- Next steps

- Production run (HR3 + 11 others chips) will be submitted mid-February 2015

- 2-3m long RPC chambers to be built and equipped with HR3 in 2015

- Moving SPIROC / SKIROC to 3<sup>rd</sup> generation

- Much more complicated due to internal ADC / TDC / SCA management

- Integration and tests of HR3 on the 2-3m long RPC will be very helpful

ega